半导体的镀膜方法与流程

本发明涉及微电子制造,尤其涉及一种半导体的镀膜方法。

背景技术:

1、半导体元器件通常在工作过程中,要应对高温高压的变化,其表面的镀膜通常质地较为硬脆,往往会收到恶劣环境的影响而造成脱落,因而如何增强其拉伸应力是亟待解决的问题。

技术实现思路

1、本发明实施例提供一种半导体的镀膜方法,能有效提高半导体表面镀膜的拉伸应力。

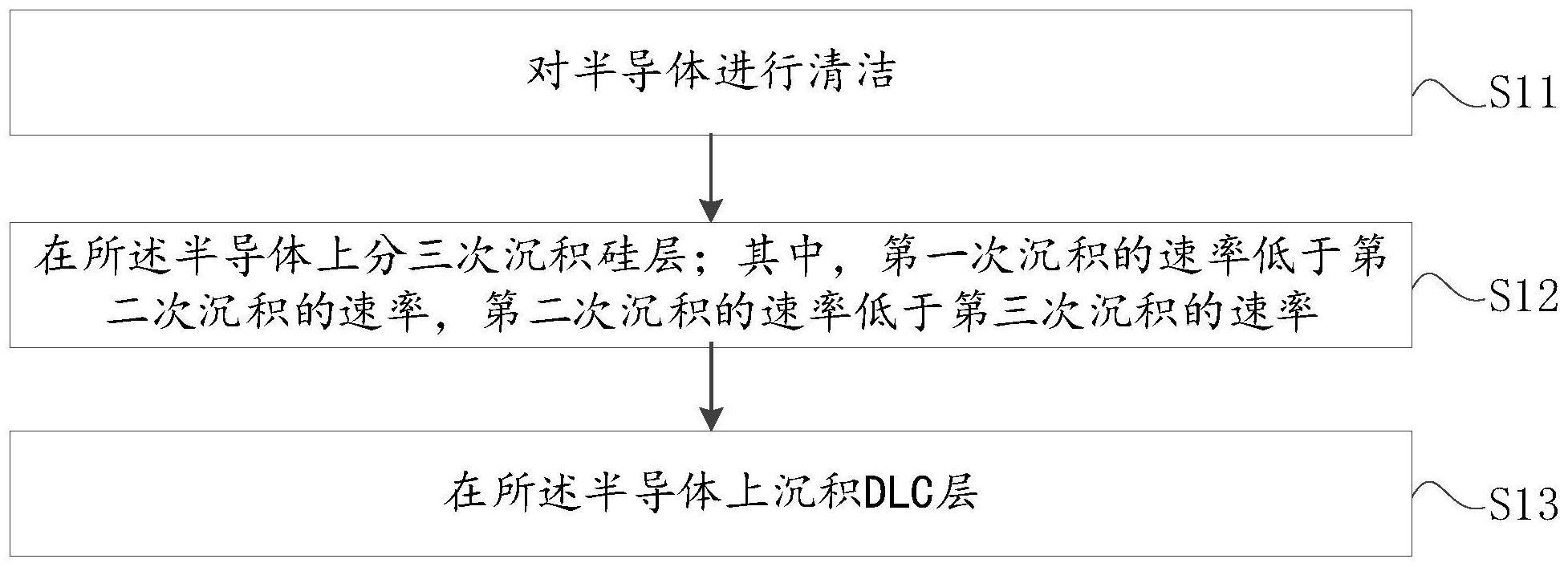

2、本发明一实施例提供一种半导体的镀膜方法,包括:

3、对半导体进行清洁;

4、在所述半导体上分三次沉积硅层;其中,第一次沉积的速率低于第二次沉积的速率,第二次沉积的速率低于第三次沉积的速率;

5、在所述半导体上沉积dlc层。

6、作为上述方案的改进,所述对半导体进行清洁,包括:

7、使用nmp溶剂浸泡半导体;

8、用去离子水清洗所述半导体;

9、将所述半导体放入ipa溶剂中进行超声波清洗;

10、待所述半导体干燥后,对所述半导体进行离子清洗。

11、作为上述方案的改进,所述nmp溶剂的温度为20-40℃,浸泡时间为15-25分钟。

12、作为上述方案的改进,所述超声波清洗的时间为25-35分钟。

13、作为上述方案的改进,所述待所述半导体干燥后,对所述半导体进行离子清洗,包括:

14、待所述半导体干燥后,将所述半导体置入真空室;

15、对所述真空室进行抽真空并加热到200-250℃;

16、通入预设气体到真空室;其中,所述预设气体为氩气、氩氧混合气体、氩乙烷混合气体或氮氦混合气体;

17、在真空室气压达到10-15pa时,对所述预设气体进行电离形成等离子体,并利用所述等离子体对所述半导体的表面进行轰击清洗;其中,轰击清洗的时间为30分钟。

18、作为上述方案的改进,所述第一次沉积的速率为0.45-0.55埃/秒,所述第二次沉积的速率为0.75-0.85埃/秒,所述第三次沉积的速率为0.95-1.05埃/秒。

19、作为上述方案的改进,所述在所述半导体上分三次沉积硅层,具体为:

20、采用溅射镀膜装置在所述半导体上分三次沉积硅层;其中,所述溅射镀膜装置的作业参数包括:真空度为1.5×10-1-2.5×10-1pa,离子源功率为2.0-2.5kw,工件负偏压为100-150v,溅射靶功率为1.2-1.5kw。

21、作为上述方案的改进,所述溅射镀膜装置使用的溅射气体为氩气;在所述第一次沉积中,氩气的流量为140-160sccm;在所述第二次沉积和所述第三次沉积中,氩气的流量为190-210sccm。

22、作为上述方案的改进,所述第一次沉积和所述第二次沉积的硅层厚度均为1.5-2.5nm,所述第三次沉积的硅层厚度为0.5-1.5nm;所述dlc层的厚度为3-5nm。

23、作为上述方案的改进,所述在所述半导体上沉积dlc层,具体为:

24、采用化学气相沉积装置在所述半导体上沉积dlc层;其中,所述化学气相沉积装置中通入的气体为氩气和甲烷,氩气的流量为140-160sccm,甲烷的流量为90-110sccm;所述化学气相沉积装置的作业参数包括:真空度为1.5×10-1-2.5×10-1pa,离子源功率为2.5-3.0kw,工件负偏压为140-160v,沉积时间为40-50min。

25、与现有技术相比,本发明实施例公开的半导体的镀膜方法,通过先对半导体进行清洁,能够清除半导体表面的杂质,提高镀膜结合力,再在半导体上分三次沉积硅层,并且,第一次沉积的速率低于第二次沉积的速率,第二次沉积的速率低于第三次沉积的速率,然后再沉积dlc层,能够使得形成的膜层缺陷较少,并且前两层硅层起到过渡作用,能够增强镀膜表面的拉伸应力。

技术特征:

1.一种半导体的镀膜方法,其特征在于,包括:

2.如权利要求1所述的半导体的镀膜方法,其特征在于,所述对半导体进行清洁,包括:

3.如权利要求2所述的半导体的镀膜方法,其特征在于,所述nmp溶剂的温度为20-40℃,浸泡时间为15-25分钟。

4.如权利要求2所述的半导体的镀膜方法,其特征在于,所述超声波清洗的时间为25-35分钟。

5.如权利要求2所述的半导体的镀膜方法,其特征在于,所述待所述半导体干燥后,对所述半导体进行离子清洗,包括:

6.如权利要求1所述的半导体的镀膜方法,其特征在于,所述第一次沉积的速率为0.45-0.55埃/秒,所述第二次沉积的速率为0.75-0.85埃/秒,所述第三次沉积的速率为0.95-1.05埃/秒。

7.如权利要求6所述的半导体的镀膜方法,其特征在于,所述在所述半导体上分三次沉积硅层,具体为:

8.如权利要求6所述的半导体的镀膜方法,其特征在于,所述溅射镀膜装置使用的溅射气体为氩气;在所述第一次沉积中,氩气的流量为140-160sccm;在所述第二次沉积和所述第三次沉积中,氩气的流量为190-210sccm。

9.如权利要求1所述的半导体的镀膜方法,其特征在于,所述第一次沉积和所述第二次沉积的硅层厚度均为1.5-2.5nm,所述第三次沉积的硅层厚度为0.5-1.5nm;所述dlc层的厚度为3-5nm。

10.如权利要求1所述的半导体的镀膜方法,其特征在于,所述在所述半导体上沉积dlc层,具体为:

技术总结

本发明公开了一种半导体的镀膜方法,包括:对半导体进行清洁;在所述半导体上分三次沉积硅层;其中,第一次沉积的速率低于第二次沉积的速率,第二次沉积的速率低于第三次沉积的速率;在所述半导体上沉积DLC层。采用本发明实施例,能有效提高半导体表面镀膜的拉伸应力。

技术研发人员:张俊群

受保护的技术使用者:东莞新科技术研究开发有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!