掩模与支撑部的连接体及其制造方法与流程

本发明涉及掩模与支撑部的连接体及其制造方法。更具体地,涉及一种在半导体晶片上形成像素时使用,且能够精密地形成超高分辨率的掩模图案的掩模与支撑部的连接体及其制造方法。

背景技术:

1、作为oled制造工艺中形成像素的技术,主要使用fmm(fine metal mask,精细金属掩模)方法,该方法将薄膜形式的金属掩模(shadow mask,阴影掩模)紧贴到基板且在所需位置上沉积有机物。

2、现有oled制造工序中在制造掩模薄膜之后,通过将掩模焊接到oled像素沉积框架并使用,但是固定的过程中存在很难对大面积掩模进行对准的问题。此外,在焊接固定到框架的过程中由于掩模膜的厚度过薄且为大面积,因此存在掩模基于荷重下垂或者扭曲的问题。

3、在超高画质的oled制造工序中,1μm以下细微的对准误差也会导致像素沉积失败,因此需要开发能够防止掩模的下垂或者扭曲等变形并使对准精确的技术等。

4、另外,最近vr(virtual reality,虚拟现实)机器中使用的微显示器(microdisplay)备受关注。为了在vr机器中将图像呈现在使用者眼前,微显示器画面尺寸不仅要明显小于现有的显示器,而且要在微小的画面内实现高画质。因此,需要制造出一种掩模图案,其尺寸明显小于现有超高画质oled制造工序中使用的掩模,以及在进行像素沉积工序之前需要对掩模进行更细微的对准作业。

技术实现思路

1、技术问题

2、因此,本发明是为了解决如上所述的现有技术中的诸多问题而提出的,目的在于提供一种能够实现微显示器(micro display)的超高画质像素的掩模与支撑部的连接体及其制造方法。

3、此外,本发明的目的在于,提供一种通过使掩模准确地对准从而能够提高像素沉积的稳定性的掩模与支撑部的连接体及其制造方法。

4、此外,本发明的目的在于,提供一种掩模的整个部分具有均匀的压力水平的掩模与支撑部的连接体及其制造方法。

5、但是,上述技术问题仅为示例性的,本发明的范围并不受限于此。

6、技术方案

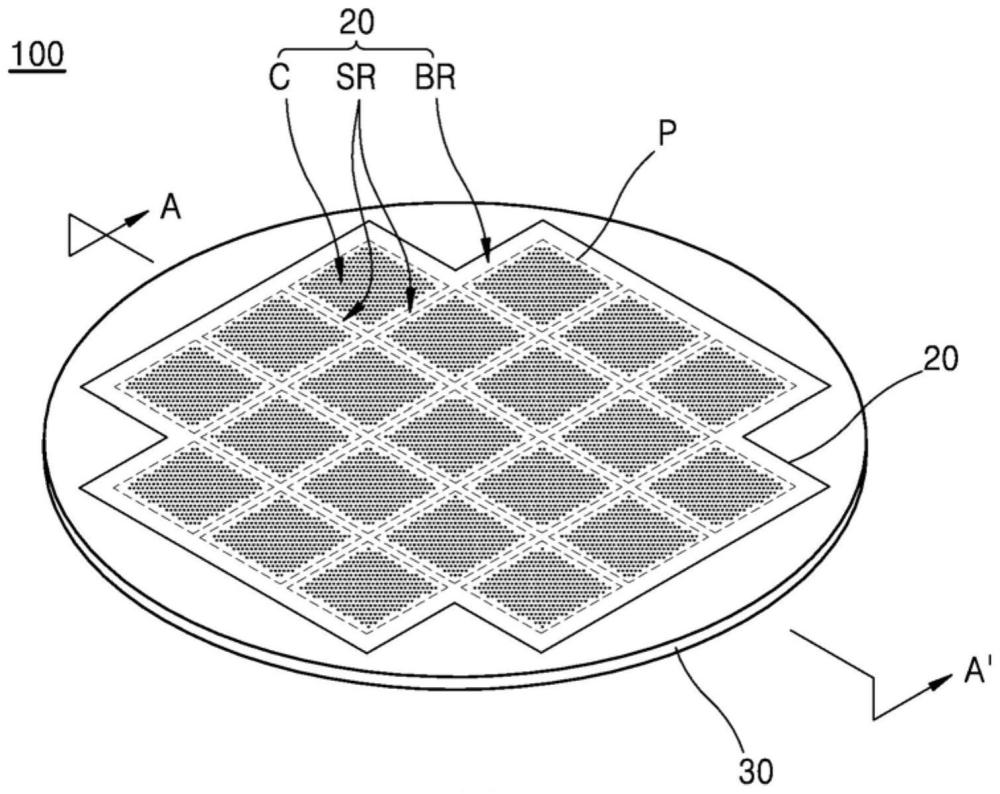

7、本发明的上述目的将通过掩模与支撑部的连接体实现,该连接体用于半导体晶片上的oled像素形成工艺中,包括:支撑部,其包括边缘部和栅格部;以及掩模,其连接在所述支撑部上,且包括形成有掩模图案的多个单元部,在所述支撑部的一面上,布置有所述掩模的单元部的区域以外的至少一部分区域中露出所述支撑部。

8、所述支撑部的边缘可以为圆形。

9、所述支撑部与所述掩模之间通过夹设连接部连接,所述连接部可包括ni、cu、ti、au、ag、al、sn、in、bi、zn、sb、ge、cd中至少一种材料。

10、可至少露出与所述支撑部的边缘部对应的区域。

11、所述栅格部可包括:多个第一栅格部,其沿着第一方向延伸地形成且两端连接于所述边缘部;多个第二栅格部,其沿着垂直于所述第一方向的第二方向延伸地形成且与所述第一栅格部交叉,两端连接于所述边缘部。

12、所述掩模可包括:所述多个单元部;划分部,其布置于所述多个单元部之间;以及外围部,其布置于所述多个单元部的外围边缘。

13、可露出与所述掩模的所述外围部外侧部分对应的所述支撑部的区域。

14、所述单元部为四边形形状,所述划分部和所述外围部可沿着第一方向及垂直于第一方向的第二方向形成。

15、所述外围部的宽度可大于所述划分部的宽度。

16、所述掩模可包括不同材料的第一掩模层和第二掩模层,所述第一掩模层为ni、cu、au、ag、al、co、ti、cr、w、mo中至少一种材料,所述第二掩模层为因瓦(invar)或者超因瓦(super invar)材料。

17、所述支撑部可由硅晶片形成,所述掩模在所述硅晶片上通过电铸(electroforming)形成。

18、所述支撑部的表面电阻为5×10-4ohm·cm至1×10-2ohm·cm。

19、所述硅晶片的(100)面或者(111)面结晶方向可与所述栅格部的形成方向不平行。

20、所述掩模可包括:所述多个单元部;以及外围部,其布置于所述多个单元部的外围边缘,每个所述单元部之间形成有狭缝线,以使所述单元部相隔布置。

21、所述栅格部的厚度可小于所述边缘部的厚度,所述边缘部的厚度为500μm至1000μm,所述栅格部的厚度为50μm至200μm。

22、此外,本发明的所述目的可通过掩模与支撑部的连接体的制造方法实现,该连接体用于半导体晶片上的oled像素形成工艺中,该方法包括如下步骤:(a)准备导电基板;(b)在所述导电基板的第一面上形成掩模,该掩模包括形成有掩模图案的多个单元部;(c)对所述导电基板和所述掩模进行热处理;以及(d)通过在所述导电基板第一面的反面即第二面上对所述导电基板进行蚀刻从而形成支撑部,该支撑部包括边缘部和栅格部;在所述(b)步骤与所述(c)步骤之间或者在所述(c)步骤与所述(d)步骤之间,进一步包括在所述支撑部的一面上,布置有所述掩模的单元部的区域以外的至少一部分区域中露出所述支撑部的步骤。

23、在所述支撑部的一面上,布置有所述掩模的单元部的区域以外的至少一部分区域中露出所述支撑部的步骤,可包括以下步骤:(1)在所述多个单元部上形成绝缘部;以及(2)去除未形成所述绝缘部且露出所述掩模的区域,从而使所述支撑部的至少一部分区域露出。

24、在所述(a)步骤与所述(b)步骤之间,可进一步包括以下步骤:形成包括ni、cu、ti、au、ag、al、sn、in、bi、zn、sb、ge、cd中至少一种材料的连接部。

25、在所述(c)步骤与所述(d)步骤之间,可进一步包括以下步骤:(c2)将模板以夹设临时粘合部状态粘合到所述掩模上;(c3)在所述导电基板的第一面的相反面即第二面上,将所述导电基板的厚度缩减至50μm至200μm。

26、在所述(c)步骤与(d)步骤之间,可进一步包括以下步骤:(c2’)将模板以夹设临时粘合部状态粘合到所述掩模上;以及(c3’)在所述导电基板第一面的相反面即第二面上,将至少形成有所述栅格部的区域的厚度缩减至50μm至200μm。

27、发明效果

28、根据如上所述构成的本发明,具有能够实现微显示器(micro display)的超高画质像素的效果。

29、此外,根据本发明,具有通过使掩模准确对准来提高像素沉积的稳定性的效果。

30、此外,根据本发明,具有掩模的所有部分保持均匀的压力水平的效果。

31、当然,本发明的范围不受上述效果的限制。

技术特征:

1.一种掩模与支撑部的连接体,其用于半导体晶片上的oled像素形成工艺中,包括:

2.如权利要求1所述的掩模与支撑部的连接体,其中,所述支撑部的边缘为圆形。

3.如权利要求1所述的掩模与支撑部的连接体,其中,所述支撑部与所述掩模之间通过夹设连接部连接,所述连接部包括ni、cu、ti、au、ag、al、sn、in、bi、zn、sb、ge、cd中至少一种材料。

4.如权利要求1所述的掩模与支撑部的连接体,其中,至少露出与所述支撑部的边缘部对应的区域。

5.如权利要求2所述的掩模与支撑部的连接体,其中,所述栅格部包括:

6.如权利要求5所述的掩模与支撑部的连接体,其中,所述掩模包括:

7.如权利要求6所述的掩模与支撑部的连接体,其中,露出与所述掩模的所述外围部外侧部分对应的所述支撑部区域。

8.如权利要求6所述的掩模与支撑部的连接体,其中,所述单元部为四边形形状,所述划分部和所述外围部沿着第一方向及垂直于第一方向的第二方向形成。

9.如权利要求8所述的掩模与支撑部的连接体,其中,所述外围部的宽度大于所述划分部的宽度。

10.如权利要求1所述的掩模与支撑部的连接体,其中,所述掩模包括不同材料的第一掩模层和第二掩模层,所述第一掩模层为ni、cu、au、ag、al、co、ti、cr、w、mo中至少一种材料,所述第二掩模层为因瓦或者超因瓦材料。

11.如权利要求1所述的掩模与支撑部的连接体,其中,所述支撑部由硅晶片形成,所述掩模在所述硅晶片上通过电铸形成。

12.如权利要求11所述的掩模与支撑部的连接体,其中,所述支撑部的表面电阻为5×10-4ohm·cm至1×10-2ohm·cm。

13.如权利要求11所述的掩模与支撑部的连接体,其中,所述硅晶片的(100)面或者(111)面结晶方向与所述栅格部的形成方向不平行。

14.如权利要求5所述的掩模与支撑部的连接体,其中,所述掩模包括:

15.如权利要求1所述的掩模与支撑部的连接体,其中,所述栅格部的厚度小于所述边缘部的厚度,所述边缘部的厚度为500μm至1000μm,所述栅格部的厚度为50μm至200μm。

16.一种掩模与支撑部的连接体的制造方法,该连接体用于半导体晶片上的oled像素形成工艺中,该方法包括如下步骤:

17.如权利要求16所述的掩模与支撑部的连接体的制造方法,其中,在所述支撑部的一面上,布置有所述掩模的单元部的区域以外的至少一部分区域中露出所述支撑部的步骤,包括以下步骤:

18.如权利要求16所述的掩模与支撑部的连接体的制造方法,其中,在所述(a)步骤与所述(b)步骤之间,进一步包括以下步骤:

19.如权利要求16所述的掩模与支撑部的连接体的制造方法,其中,在所述(c)步骤与所述(d)步骤之间,进一步包括以下步骤:

20.如权利要求16所述的掩模与支撑部的连接体的制造方法,其中,在所述(c)步骤与(d)步骤之间,进一步包括以下步骤:

技术总结

本发明涉及掩模与支撑部的连接体及其制造方法。根据本发明的掩模与支撑部的连接体,其用于半导体晶片上的OLED像素形成工艺中,包括:支撑部,其包括边缘部和栅格部;以及掩模,其连接在所述支撑部上且包括形成有掩模图案的多个单元部,在所述支撑部的一面上,布置有所述掩模的单元部的区域以外的至少一部分区域中露出所述支撑部。

技术研发人员:李永浩,金辉寿,李东真,李炳一,张泽龙,金钟一

受保护的技术使用者:悟劳茂材料公司

技术研发日:

技术公布日:2024/2/8

- 还没有人留言评论。精彩留言会获得点赞!