形成具有涂层的结构的方法及具有涂层的结构与流程

1.本发明涉及一种具有涂层的结构的形成方法和具有涂层的结构,尤其涉及一种涂层具有良好填隙能力和附着性的结构的形成方法和结构。

背景技术:

2.在镀膜制程中,为了在基底上形成膜层,现行主流的方法是利用镀膜技术,例如物理气相沉积法(pvd)与化学气相沉积法(cvd),以于基底上形成膜层。

3.然而,对于现行的镀膜技术,当基底的表面具有沟槽,特别是开口面积小(例如小于500纳米)且深宽比(aspect ratio)大于2的沟槽而言,现行的镀膜技术无法提供良好的填隙能力。因此,公知的镀膜技术无法提供良好的镀膜质量。

4.此外,当镀膜的厚度较厚时,通常需要较长的沉积时间,以形成均匀且较厚的沉积膜。然而,对于较厚的镀膜,其容易因沉积过程中产生的内应力或是基底表面的低表面能,而造成镀膜剥离于基底的表面。

技术实现要素:

5.有鉴于此,本发明揭露了一种形成具有涂层的结构的方法以及具有涂层的结构,以解决上述的缺陷。

6.根据本揭露的一实施例,揭露一种形成具有涂层的结构的方法,包括:提供基底;涂布流体至基底的表面,其中流体包括载体及多个含硅纳米颗粒;以及施行加热制程,以去除载体,并且将些含硅纳米颗粒转换成含硅层、金属硅化物层、或包括含硅层及金属硅化物层的堆栈层。

7.根据本揭露的另一实施例,揭露一种具有涂层的结构,包括:基底,包括多个沟槽,其中各沟槽的深宽比大于2;含硅层,填满沟槽;金属硅化物层,延伸设置于基底和含硅层之间,且金属硅化物层覆盖住各沟槽的内壁。

附图说明

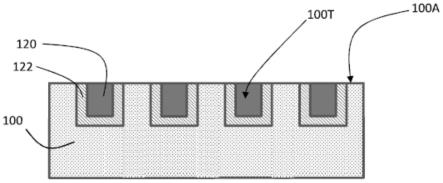

8.图1是本揭露一实施例的基底上设置有流体的剖面图;

9.图2是本揭露一实施例的基底上设置有含硅层的剖面图;

10.图3是本揭露一实施例的基底上设置有金属硅化物的剖面图;

11.图4是本揭露一实施例的含硅层上设置有半导体层的剖面图;

12.图5是本揭露一实施例的基底上设置有流体的剖面图;

13.图6是本揭露一实施例的基底上设置有含硅层的剖面图;

14.图7是本揭露一实施例的沟槽内设置有金属硅化物的剖面图;

15.图8是本揭露另一实施例的沟槽内设置有金属硅化物的剖面图;

16.图9是本揭露另一实施例的沟槽内设置有金属硅化物的剖面图;

17.图10是具体实施例一的sem图;

18.图11是具体实施例二的sem图;

19.图12是具体实施例三的sem图;

20.图13是具体实施例四的sem图;

21.图14是具体实施例五的sem图;

22.图15是具体实施例六的sem图;

23.图16是具体实施例七的sem图;

24.图17是具体实施例八的sem图;

25.图18是具体实施例九的sem图;

26.图19是具体实施例十的sem图;

27.图20是比较例一的sem图。

28.符号说明:

29.100

ꢀꢀꢀꢀꢀꢀꢀ

基底

30.100a

ꢀꢀꢀꢀꢀꢀ

表面

31.100t

ꢀꢀꢀꢀꢀꢀ

沟槽

32.110

ꢀꢀꢀꢀꢀꢀꢀ

流体

33.112

ꢀꢀꢀꢀꢀꢀꢀ

载体

34.114

ꢀꢀꢀꢀꢀꢀꢀ

含硅纳米颗粒

35.120

ꢀꢀꢀꢀꢀꢀꢀ

含硅层

36.122

ꢀꢀꢀꢀꢀꢀꢀ

金属硅化物层

37.130

ꢀꢀꢀꢀꢀꢀꢀ

半导体层

具体实施方式

38.图1是本揭露一实施例的基底上设置有流体的剖面图。参照图1,在形成具有涂层的结构的初始阶段,提供一基底100,基底100可以是金属材料、半导体材料、绝缘体材料或非金属材料,例如:铜(cu)、铁(fe)、镍(ni)与钼(mo)等金属材料、石墨(c)的非金属材料、氧化铝等绝缘体材料、以及氧化锌、氮化镓与氮化铝等半导体材料,但不限定于此。根据本揭露一实施例,基底100可以是耐温的材质,例如是在500℃-1500℃的温度下而不会变形或变性的材质。

39.接着,可以在基底100的表面100a涂布流体110,使流体110完整覆盖住基底100的表面100a。根据本揭露一实施例,可以利用旋转涂布制程,或其他合适的制程,以将流体110完整覆盖住基底100的表面100a。其中,流体110可以是胶体(colloidal)或浆料,其包括载体112及分散于载体112中的多个含硅纳米颗粒114。此外,端视实际需求,流体110也可以包括酸液、碱液、有机溶剂、水,胶体可为溶胶、有机化合物、高分子溶液、缔合胶体。载体112可以是气体或液体。含硅纳米颗粒114可以是结晶硅纳米颗粒或非晶硅纳米颗粒,含硅纳米颗粒114的尺寸可以为1nm-300nm,例如是20nm、30nm、100nm、200nm、或其中的任何数值。根据本揭露一实施例,含硅纳米颗粒114的表面可以存在原生氧化层,但是此原生氧化层的厚度较佳小于10nm,例如是5nm。需注意是,图1中所示的含硅纳米颗粒114的数量仅为例示,其实际的数量可端视需求而调整。

40.在流体110完整覆盖住基底100的表面100a之后,可接着施行加热制程,而形成图2

所示包括含硅层的结构。图2是本揭露一实施例的基底上设置有含硅层的剖面图。参照图2,在施行加热制程的过程中,可以去除载体112,并且将含硅纳米颗粒114转换成含硅层120,此含硅层120可作为基底100的涂层。根据本揭露一实施例,加热制程包括真空加热制程,例如压力为1x 10-2

torr至10x 10-1

torr及制程温度为500℃-2000℃的真空加热制程。通过施行加热制程,含硅纳米颗粒114可以被烧结(sintering)而产生多晶结构,例如多晶硅结构。

41.根据本揭露的实施例,载体112除了可以被用来分散含硅纳米颗粒114,其也可以对基底100具有一定的腐蚀性,因此可以用于增加基底100表面的粗糙度。因此,在加热制程中,被粗糙化的基底100的表面100a可以和含硅层120产生较大的接触面积,而增加基底100和含硅层120之间的附着强度。

42.图3是本揭露一实施例的基底上设置有金属硅化物的剖面图。参照图3,图3的结构类似图2所示的结构,主要差异在于,基底100上另包括金属硅化物层122,例如是设置在基底100和含硅层120之间的金属硅化物层122,因此金属硅化物层122及含硅层120可以被视为是设置于基底100上的堆栈层。其中,此金属硅化物层122也可以经由上述的加热制程而形成。举例而言,在加热制程中,流体110中的含硅纳米颗粒114可以和基底100产生反应,而生成金属硅化物层122。其中,金属硅化物层122可以包括由硅及部分主族元素(例如第1、2、13、14、15、16、17族主族元素)或部分过渡金属所构成的二元化合物,例如nisi、cu5si、cosi、mo5si3、fesi、sic等,但不限定于此。由于上述二元化合物的特性不尽相同,例如硅化钼层相较于钼基底可以具有更高的硬度,而碳化硅层相较于碳基底可以具有更高的硬度和绝缘性。因此,可以通过形成金属硅化物层122,而产生不同于原始基底100的特性。根据本揭露的另一实施例,基底100上的含硅层120也可以全部被反应成金属硅化物层122,使得在形成金属硅化物层122之后,基底100上不残留任何含硅层120。

43.图4是本揭露一实施例的含硅层上设置有半导体层的剖面图。在完成图3所示的结构之后,可以选择性的对含硅层120施行平坦化制程,并接着施行另一沉积制程或涂布制程,而形成半导体层130。通过含硅层120和基底100反应所生成的金属硅化物层122,可以增进含硅层120和基底100之间可以具有较佳的附着强度,因此即便设置于含硅层120上方的半导体层130可能会施予应力至含硅层120或基底100,含硅层120仍不会自基底100剥离。

44.除了上述实施例之外,基底100也可以是包括多个沟槽100t的基底100。图5是本揭露一实施例的基底上设置有流体的剖面图。参照图5,在形成具有涂层的结构的初始阶段,提供一基底100,且基底100的表面100a包括多个沟槽100t。

45.接着,可以在基底100的表面100a涂布或喷涂流体110,使流体110完整覆盖住基底100的表面100a,并填入沟槽100t。根据本揭露一实施例,可以利用旋转涂布制程、气流喷涂制程,或其他合适的制程,以将流体110完整覆盖住基底100的表面100a。其中,流体110可以是胶体(colloidal)、气溶胶(aerosol)或浆料,其包括载体112及分散于载体112中的多个含硅纳米颗粒114。此外,端视实际需求,流体110也可以包括酸液、碱液、有机溶剂、水,胶体可为溶胶、有机化合物、高分子溶液、缔合胶体。载体112可以是气体或液体。含硅纳米颗粒114可以是结晶硅纳米颗粒或非晶硅纳米颗粒,含硅纳米颗粒114的尺寸可以为1nm-300nm,例如是20nm、30nm、100nm、200nm、或其中的任何数值。根据本揭露一实施例,含硅纳米颗粒114的表面可以存在原生氧化层,但是此原生氧化层的厚度较佳小于10nm,例如是5nm。需注意是,图5中所示的含硅纳米颗粒114的数量仅为例示,其实际的数量可端视需求而调整。

46.在流体110完整覆盖住基底100的表面100a之后,接着可以将部分覆盖住基底100的表面100a的流体110移除,仅保留填入沟槽100t的流体110。根据本揭露一实施例,可以利用刮刀移除制程,或其他合适的移除制程,以将部分覆盖住基底100的表面100a的流体110移除,保留填入沟槽100t的流体110。之后,可接着施行加热制程,以去除载体112,并且将含硅纳米颗粒114转换成含硅层,而形成图6所示包括含硅层120的结构。图6是本揭露一实施例的基底上设置有含硅层的剖面图。参照图6,通过施行加热制程,含硅层120可作为涂层,并填满各沟槽100t,且含硅层120中不包括任何空穴。含硅层120可作为基底100的涂层,且含硅层120的表面形貌可不同于基底100原始的表面形貌。根据本揭露一实施例,加热制程包括真空加热制程,例如压力为1x10-2

torr至10x10-1

torr及制程温度为500℃-2000℃的真空加热制程。通过施行加热制程,含硅纳米颗粒114可以被烧结(sintering),而产生多晶结构,例如多晶硅层。根据本揭露一实施例,含硅层120不限于只能被设置于沟槽100t中,含硅层120也可以完整覆盖基底100,且含硅层120的表面形貌可不同于基底100原始的表面形貌。此外,对于填入沟槽100t的含硅层120,该些含硅层120也可以被视为是涂层。

47.根据本揭露的实施例,载体112除了可以被用来分散含硅纳米颗粒114,其也可以对基底100具有一定的腐蚀性,因此可以增加基底100表面或沟槽100t内壁的粗糙度。因此,在加热制程中,被粗糙化的基底100可以和含硅层120产生较大的接触面积,而增加基底100和含硅层120之间的附着强度。

48.图7是本揭露一实施例的沟槽内设置有金属硅化物的剖面图。图7的结构类似图6所示的结构,两者间的主要差异在于,基底100和含硅层120之间另外包括金属硅化物层122。举例而言,参照图5及图7,在图5中所示流体110完整覆盖住基底100的表面100a之后,将部分覆盖住基底100的表面100a的流体110移除,仅保留填入沟槽100t的流体110。根据本揭露一实施例,可以利用刮刀移除制程,或其他合适的移除制程,以将部分覆盖住基底100的表面100a的流体110移除,保留填入沟槽100t的流体110。之后,可接着施行加热制程,以去除载体112,并且将含硅纳米颗粒114转换成含硅层120,而形成如图7所示包括含硅层120与金属硅化物层122的堆栈层结构。此金属硅化物层122可以经由上述的加热制程而形成,并完整覆盖沟槽100t的内壁。举例而言,在加热制程中,流体110中的含硅纳米颗粒114可以和沟槽100t的内壁产生反应,而生成金属硅化物层122。其中,金属硅化物层122可以包括由硅及部分主族元素(例如第1、2、13、14、15、16、17族主族元素)或部分过渡金属所构成的二元化合物,例如nisi、cu5si、cosi、mo5si3、fesi等,但不限定于此。

49.图8是本揭露另一实施例的沟槽内设置有金属硅化物的剖面图。图8的结构类似图7所示的结构,两者间的主要差异在于,沟槽100t内的含硅层会被完全转换成金属硅化物层122,使得金属硅化物层122可以填满各沟槽100t,且位于沟槽100t内的金属硅化物层122中不包括任何空穴。举例而言,参照图5及图8,在图5中所示流体110完整覆盖住基底100的表面100a之后,将部分覆盖住基底100的表面100a的流体110移除,仅保留填入沟槽100t的流体110。根据本揭露一实施例,可以利用刮刀移除制程,或其他合适的移除制程,以将部分覆盖住基底100的表面100a的流体110移除,保留填入沟槽100t的流体110。之后,可接着施行加热制程,以去除载体112,并且将含硅纳米颗粒114转换成金属硅化物层122,而形成图8所示包括金属硅化物层122的结构。

50.图9是本揭露另一实施例的沟槽内设置有金属硅化物的剖面图。图9的结构类似图

7所示的结构,两者间的主要差异在于,含硅层120与金属硅化物层122不仅只设置于沟槽100t中,还会延伸覆盖住基底100的表面100a,因此含硅层120与金属硅化物层122所构成的堆栈层可以提供平坦的表面。举例而言,参照图5及图9,可以完整保留图5中所示的覆盖住基底100的表面100a的流体110,接着,施行加热制程,以去除载体112,并且将含硅纳米颗粒114转换成含硅层120,以及在基底100和含硅层120之间形成金属硅化物层122。其中,此金属硅化物层122可以经由上述的加热制程而形成,并完整覆盖基底100的表面100a及沟槽100t的内壁,而形成图9所示包括含硅层120及金属硅化物层122的堆栈层结构。

51.以下就形成具有涂层的结构的各具体实施例加以描述。

52.具体实施例一:

53.重量为1kg、平均粒径为200nm的硅粉体加入至4kg的去离子水中,以直流搅拌机进行均匀搅拌,调配成20%固含量的含硅流体。接着将含硅流体滴至铜(cu)金属表面后,以最高转速为1000rpm的旋转涂布方式对铜(cu)基底表面进行涂布。之后,将涂布有含硅流体的样品放入真空高温炉中,抽真空至5x 10-1

torr,加温至700℃,持温30分钟,即可产生铜硅合金于铜金属(金属基底)表面。相应的sem图如图10所示。

54.具体实施例二:

55.将重量为1kg、平均粒径为180nm的硅粉体加入至4kg的去离子水中,以直流搅拌机进行均匀搅拌,调配成20%固含量的含硅流体,接着将含硅流体滴至铁(fe)金属表面后,以最高转速为1000rpm的旋转涂布方式对铁(fe)金属表面进行涂布。之后,将涂布有含硅流体的样品放入真空高温炉中,抽真空至5x 10-1

torr,加温至900℃,持温30分钟,即可以产生铁硅合金于铁金属(金属基底)表面。相应的sem图如图11所示。

56.具体实施例三:

57.将重量为1kg、平均粒径为300nm的硅粉体加入至4kg的去离子水中,以直流搅拌机进行均匀搅拌,调配成20%固含量的含硅流体,接着将含硅流体滴至镍(ni)金属表面后,以最高转速为1000rpm的旋转涂布方式在镍(ni)金属表面进行涂布。之后,将涂布有含硅流体的样品放入真空高温炉中,抽真空至5x10-1

torr,加温至1100℃,持温30分钟,即可以产生镍硅合金于镍金属(金属基底)表面。相应的sem图如图12所示。

58.具体实施例四:

59.将重量为1kg、平均粒径为120nm的硅粉体加入至9kg的去离子水中,以直流搅拌机进行均匀搅拌,调配成10%固含量的含硅流体,接着将含硅流体通过加压气体乘载方式,输送至喷头出口,将喷头对准石墨(c)表面进行喷涂,本实施例的加压气体为氩气,气体压力为7bar,在形成硅薄膜于石墨(c)表面后,放入真空高温炉中,抽真空至5x 10-1

torr,加温至度1200℃,持温30分钟,即可以产生碳化硅于石墨(非金属基底)表面。相应的sem图如图13所示。

60.具体实施例五:

61.将重量为1kg、平均粒径为150nm的硅粉体加入至9kg的去离子水中,以直流搅拌机进行均匀搅拌,调配成10%固含量的含硅流体,接着将含硅流体通过加压气体乘载方式,输送至喷头出口,将喷头对准钼金属(mo)表面进行喷涂,本实施例的加压气体为氩气,气体压力为7bar。之后,将样品放入真空高温炉中,抽真空至5x 10-1

torr,加温至度2000℃,持温30分钟,即可以产生钼硅合金于钼金属(mo)(金属基底)表面。相应的sem图如图14所示。

62.具体实施例六:

63.将重量为1kg、平均粒径为120nm的硅粉体加入至4kg的去离子水中,以直流搅拌机进行均匀搅拌,调配成20%固含量的含硅流体,接着将含硅流体滴至氧化铝表面后,以最高转速为1000rpm的旋转涂布方式在氧化铝表面进行涂布。之后,将涂布有含硅流体的样品放入真空高温炉中,放入真空高温炉中,抽真空至5x 10-1

torr,加温至度900℃,持温30分钟,即可以产生硅薄膜于氧化铝(绝缘体基底)表面。相应的sem图如图15所示。

64.具体实施例七:

65.将重量为1kg、平均粒径为120nm的硅粉体加入至4kg的去离子水中,以直流搅拌机进行均匀搅拌,调配成20%固含量的含硅流体,接着将含硅流体滴至氧化锌表面后,以最高转速为1000rpm的旋转涂布方式在氧化锌表面进行涂布。之后,将涂布有含硅流体的样品放入真空高温炉中,抽真空至5x10-1

torr,加温至度900℃,持温30分钟,即可以产生硅薄膜于氧化锌(半导体基底)表面。相应的sem图如图16所示。

66.具体实施例八:

67.将重量为1kg、平均粒径为120nm的硅粉体加入至4kg的去离子水中,以直流搅拌机进行均匀搅拌,调配成20%固含量的含硅流体,接着将含硅流体滴至氮化镓表面后,以最高转速为1000rpm的旋转涂布方式在氮化镓表面进行涂布。之后,将涂布有含硅流体的样品放入真空高温炉中,抽真空至5x10-1

torr,加温至度900℃,持温30分钟,即可以产生硅薄膜于氮化镓(半导体基底)表面。相应的sem图如图17所示。

68.具体实施例九:

69.将重量为1kg、120nm的硅粉体加入至4kg的去离子水中,以直流搅拌机进行均匀搅拌,调配成20%固含量的含硅流体,接着将含硅流体滴至氮化铝表面后,以最高转速为1000rpm的旋转涂布方式在氮化铝表面进行涂布。之后,将涂布有含硅流体的样品放入真空高温炉中,放入真空高温炉中,抽真空至5x 10-1torr,加温至度900℃,持温30分钟,即可以产生硅薄膜于氮化铝(半导体基底)表面。相应的sem图如图18所示。

70.具体实施例十:

71.将重量为1kg、平均粒径为80nm的硅粉体加入至9kg的去离子水中,以直流搅拌机进行均匀搅拌,调配成10%固含量的含硅流体,接着将含硅流体滴至沟槽深宽比为二比一的图案化氧化铝基板表面后,进行抽真空至1x 10-1

torr,使含硅流体与图案化氧化铝基板间,因为高深宽比导致被含硅流体覆盖所产生的气泡能够消除,接着以最高转速为5000rpm的旋转涂布方式进行涂布于图案化氧化铝基板表面,在完成硅薄膜形成于图案化氧化铝基板表面及底部后,放入真空高温炉中,抽真空至5x 10-1

torr,加热至900℃,持温30分钟,即可产生硅薄膜于图案化氧化铝基板的底部。相应的sem图如图19所示。根据图19所示,硅薄膜可以完整被沉积在图案化氧化铝基板(绝缘体基底)的沟槽底部。

72.比较例一:

73.将沟槽深宽比为二比一的图案化氧化铝基板放入溅镀机内,抽真空至3x10-6

torr,射频功率300w,基板加热至600℃,旋转速率20rpm,溅镀30分钟。相应的sem图如图20所示。根据图20所示,硅薄膜无法完整被沉积在图案化氧化铝基板的沟槽底部。

74.以上所述仅为本发明的较佳实施例,凡依本发明申请专利范围所做的均等变化与修饰,皆应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1