电镀系统的制作方法

电镀系统

1.发明背景

2.微电子装置于晶片或工件上和/或中制造,微电子装置例如是半导体装置。一般的晶片电镀工艺包含通过气相沉积来于晶片的表面上沉积金属种晶层。光阻剂可被沉积和图案化,以暴露出种晶层。晶片接着移动至电镀处理器的容器(vessel)中,其中电流被导引通过电解质而到达晶片,以提供金属或其他导电材料的毯覆层(blanket layer)或图案层于种晶层上。导电材料的例子包括坡莫合金(permalloy)、金、银、铜、钴、锡、镍、和这些金属的合金。后续的处理步骤是于晶片上形成组件、接触件和/或导线。

3.在许多或大部分的应用中,金属的电镀膜或层在整个晶片或工件具有均匀的厚度是相当重要的。一些电镀处理器使用电流取样(current thief),电流取样是具有与于晶片相同的极性的电极。电流取样是借由从晶片的边缘汲取(drawing)电流来进行操作。此举有助于保持在晶片的边缘的电镀厚度以及晶片的剩余部分之上的电镀厚度更加均匀。电流取样可以是靠近晶片的边缘的实体电极。或者,电流取样可以是虚拟电流取样,其中实体电极远离晶片。在此设计中,来自远离的实体电极的电流是通过电解质传导至接近晶片的位置。

4.在晶片级封装和其他应用中的电镀工艺是根据工艺和晶片图案中的变化而有所不同。显著的电镀非均匀性时常沿着晶片图案的边缘发生。非均匀性可能因图案变化所导致的电场中的不规则性产生,或因接近晶片边缘的质量传递(mass-transfer)非均匀性产生。

5.一些电镀处理器是使用桨或搅拌器来搅拌电解质和增加电解质中的金属离子到晶片上的质量传递,而也能改善电镀均匀性。然而,容器中的电场屏蔽物可能于晶片和桨之间突出,而可能减少电解质的搅拌且降低接近晶片的边缘的电镀均匀性。电场屏蔽物可能也必须被移除和替换成代替的不同尺寸的场屏蔽物,以满足电镀不同类型的晶片的需求。此举是耗费时间且亦需要保有多种场屏蔽物的存货。

6.因此,在设计电镀处理器中仍存有工程挑战。

技术实现要素:

7.一种具有容置电解质的容器组件的电镀系统。位于容器组件中的堰取样电极组件包括气室,分成至少第一和第二虚拟取样电极部。气室具有数个分隔的开口,取样电流流过开口,以改善晶片的边缘附近的电场。堰取样电极组件上的堰环导引电流。第一和第二实体取样电极电连接于分别的电源,且分别与第一和第二虚拟取样电极部保有电连续性。

附图说明

8.在附图中,相同的附图标记在各示图中指示相同的元件。

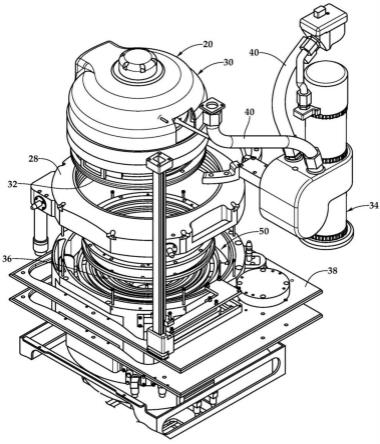

9.图1绘示电镀处理器的放大透视图。

10.图2绘示图1中所示的电镀处理器的容器组件的透视图。

11.图3绘示图2中所示的容器组件的透视剖面图。

12.图4绘示图2和图3中所示的容器组件的正交剖面图。

13.图5绘示图2-图4中所示的分段的堰取样电极组件的上透视图。

14.图6绘示图5中所示的分段的堰取样电极组件的透视剖面图。

15.图7绘示装设于图2-图5的容器组件中的另一个分段的堰取样电极组件的局部透视剖面图。

16.图8绘示装设于图2-图5的容器组件中的再另一个分段的堰取样电极组件的局部透视剖面图。

17.图9绘示图2-图5中所示的局部的桨的平面图。

具体实施方式

18.图1绘示出电镀系统20,具有头部30,头部30位于容器组件36的上方。单一的系统20可使用作为独立单元。或者,多个系统20可被提供于包封体中的阵列中,借由一个或多个机械手(robot)来装载晶片或工件至处理器中或卸除晶片或工件离开处理器。头部30可支撑于升举或升举/旋转单元34上,用以升举和/或反转头部以装载和卸除晶片至头部中的转子32中,和用以降低头部30而与容器组件36接合来进行处理。转子32具有接触环,接触环在处理期间与保持于转子中的晶片电性接触。连接至升举/旋转单元34与内部头部组件的电控制和电力缆线40从系统20向上导引到设施连接件,或导引到多处理器自动系统的连接件。具有层叠的排出环(drain rings)的清洗组件28可设置于容器框架50的上方。

19.如图2和图3中所示,分段的堰取样电极组件(weir thief electrode assembly)52是位于接近容器框架50的顶部的附近。桨54可设置于容器组件36中,且位在分段的堰取样电极组件52的水平的下方。亦参照图10,于绘示的例子中,桨54是桨插入件156。桨插入件156具有水平分隔的叶片160,延伸跨越桨环158。桨插入件156可附接于容器框架50中的桨框架55。这让桨插入件更加轻易地被移除和替换。容器固定板38上的桨致动器56移动桨。

20.转至图3和图4,容器组件36包括阳极组件64,阳极组件64具有下部杯68,下部杯68包括第一环70、第二环72和第三环74。这些环区分阳极组件成第一或内部阳极腔室76、第二或中间阳极腔室78和第三或外部阳极腔室80。第一、第二和第三阳极电极82、84和86是分别位于第一、第二和第三阳极腔室的底部。虽然可使用多种形式的阳极电极,于所示的例子中,各第一、第二和第三阳极电极可以是平面金属环。各第一、第二和第三阳极电极是连接于分别可控制的电源,或连接于图3中所示的多通道的电源98的分离通道,以允许独立控制各阳极电极所供应的电流。

21.仍参照图3和图4,在阳极组件64中,以介电材料制成的下部杯68可支撑于坚硬金属的底板66上。下部杯68上或底板66上的多个栓(latch)90卡合于容器框架50上或容器固定板38上的栓环92,以快速装设和移除阳极组件64。

22.也是以介电材料制成的上部杯60位于下部杯的顶部上。上部杯60具有环和腔室,对应于和对准于下部杯68的环和腔室之上。下部杯68和上部杯60之间的容器膜62传导电流,而避免电解质或粒子的移动。上部杯60和容器膜62是形成容器或碗件,用以保持电解质,特别是阴极电解质。下部杯68保持借由膜62与阴极电解质分离的第二电解质,特别是阳极电解质。

23.在处理期间,桨致动器56移动桨54,以搅拌包含于上部杯60中的阴极电解质。桨以摆动运动方式在桨行程尺寸中前后移动。对于一些应用来说,桨可使用其他运动方式,例如

开始/停止、交错等。在被使用的情况下,清洗组件28中的层叠的排出环是经由图2中所示的一个或多个排出件42和抽吸件44连接于排出和真空设施。容器组件36可固定在容器固定板38上,以支撑容器组件和其他组件和/或用以对准或定位容器组件。

24.参照图3和图4,容器组件36包括阳极组件64、上部杯60和分段的堰取样电极组件52,可直接或间接借由容器框架50附接或支撑。容器框架50中的堰溢流通道58连接于再循环口57,再循环口57连接于阴极电解质再循环线,在处理和/或闲置状态期间,阴极电解质再循环线可提供阴极电解质连续流动通过上部杯60。

25.转至图5和图6,分段的堰取样电极组件52可包括堰框架100。堰框架100附接于平面的堰环104,此两者皆以介电材料制成。在所示的例子,堰框架100是圆形环,圆形环具有径向分离的凸出部(lugs)102,用以附接分段的堰取样电极组件52至容器框架50。堰框架100上的柱状堰唇140向上延伸可决定上部杯60中的阴极电解质的液位。在特定工艺步骤期间,阴极电解质可越过堰唇140流出上部杯60和流入堰溢流通道58。如图6中所示,堰框架100可具有角形剖面142,角形剖面142从堰环104向上延伸而相邻于平剖面106。平剖面106可垂直于堰唇140。包含阴极电解质的气室146绕着堰框架100的内侧延伸。气室是借由图5中以虚线所绘示的内部壁148分成四个虚拟取样电极部(virtual thief electrode segments)。

26.仍参照图5,这四个虚拟取样电极部是以aa、bb、cc和dd标注。这四部因为不包括实体取样电极(physical thief electrode)而意指为数个虚拟取样电极部。与虚拟取样电极部相关的实体取样电极反而是位在远离虚拟取样电极部的位置。如下所述,容器组件中的电解质是提供从虚拟取样电极部到实体取样电极的电流路径。

27.部aa和cc可皆对着130至150度的扇形且标称为140度。部bb可对着70到90度的扇形且标称为80度。部dd是局部窄扇形,对着1至15度且标称为10度,且可安置(fit in)于两个相部aa和cc的端部之间。

28.穿过平剖面106的孔145是对齐于气室的直径上,此气室的直径大于堰环的内直径。开口145是借由提供从气室146中的阴极电解质至上部杯60中的电流路径,让虚拟取样电极部影响主要靠近晶片的边缘的容器组件中的电场。或者,如图6中的虚线所示的相邻于堰环104的槽(slot)147可被使用来取代孔145,虽然槽是更易受到气泡捕获的影响。气室146的剖面面积可最大化,以增加最小孔径或槽宽度,而简化分段的堰电极取样的制造。孔145或槽147可以角度15至25度的间隔分隔,或以角度20度的间隔分隔。孔径变化以在各部中提供均匀分布的取样电流。

29.对于以延伸至297或298mm(也就是在1或1.5mm的晶片边缘中)的电镀区域来处理300mm的晶片来说,堰环104可具有298mm的内侧直径。在所示的例子中,头部中的接触环上的密封件是距离晶片的边缘至少二毫米,且第一个电镀特征结构时常在离密封件更远的地方开始。因此,堰环104不放置在电镀膜的下方(beneath)。因而不干扰桨运动的范围或阻挡质量传递至电镀膜的边缘。堰环104是操作以引导流动,而非作为电场屏蔽物。对于较小的晶片来说,或对于所有的电镀区域更远离晶片边缘的晶片来说,可使用具有较小的内侧直径的堰环104。

30.参照图3至图5,四个实体取样电极110、111、112和113和被设置于四个取样电极杯125、127、129和131中、此四个取样电极杯125、127、129和131附接于容器框架50的底部,且

围绕阳极组件64的外侧。图3绘示出第一实体取样电极110和第三实体电极112,分别与第一和第三部aa和cc相关且在第一和第三部aa和cc的下方垂直地对齐。图示地绘示于图5中的第二和第四实体电极111和113是类似地与第二和第四部bb和dd相关,和于第二和第四部bb和dd的下方垂直地对齐。各实体取样电极是借由缆线115电连接于分离的电源通道。第一取样电解质(第一取样液(thiefolyte))是借由第一取样液膜130包含在第一取样电极杯125中的第一腔室124中。第一取样液是电性接触第一取样电极110。填充有阴极电解质的第一取样通道或通路(passageway)120是从第一取样液膜130向上延伸至分段的堰取样电极组件52的第一部aa的气室中。

31.亦如图3中所示,第三取样电解质(第三取样液)类似地借由第三取样液膜132包含在第三取样电极杯127中的第三腔室126中。第三取样液电性接触第三实体取样电极112。填充有阴极电解质的第三取样电极通道或出入口122是从第三取样液膜132向上延伸至分段的堰取样电极组件52的第三部cc的气室中。

32.如图5中所示,第二和第四取样电解质(第二和第四取样液)类似地借由第二和第四取样液膜133和135包含在第二和第四取样电极杯中的第二和第四腔室127和131中。第二和第四取样液是分别电性接触第二和第四实体取样电极111和113。填充有阴极电解质的第二和第四取样电极通道121和123是从第二和第四取样液膜向上延伸至分段的堰取样电极组件52的第二和第四部bb和dd的气室中。除了扇形角之外,如图5中所示的第二和第四虚拟取样电极部的设计可相同于图3中所示的第一和第三虚拟取样电极部。取样液化学性质可以是常见。在所示的例子中,通道120-123可在凸出部102的下方(underneath)居中对齐。根据这些部所对着的角度,各通道120-123可位在或不位在各通道120-123所对应的部的中间。

33.取样通道120-123的剖面也能基于各部的电流流动需求变化。如图7中所示,孔145的直径或槽147的尺寸可随着从提供电流的填充有阴极电解质的通道到部的距离而增加,使得所有的孔或槽对晶片200上的图案或电镀金属200a的边缘周围的电场有大致相同的影响。

34.所有四种取样液可相同。容器组件36接着包含三种电解质:阳极组件的下部杯68中的阳极电解质、上部杯60、气室和取样电极通道120-123中的阴极电解质、和取样液腔室124-127中的取样液。于一些实施例中,取样液可省略和利用阴极电解质取代。在此情况中,取样液腔室124-127和通道液膜130-133也能省略。于一些实施例中,取样液可利用阳极电解质取代。

35.图7绘示另一个分段的堰取样电极组件,其中填充有阴极电解质的通道形成虚拟取样电极部且具有径向部120r,径向部120r径向地向内延伸通过堰环104或在堰环104的下方延伸,使得径向部120r相对于图5中所示的分段的堰取样电极组件中的孔145更靠近晶片的边缘。这让虚拟取样对靠近晶片的边缘的电场有更大的影响。相对于图5的虚拟取样部aa、bb和cc,且虚拟取样的效应更分布在整个晶片边缘来说,虚拟取样电流需求亦减少,和虚拟取样的效应更窄。图7中的设计可作为局部虚拟取样电极(部dd)。径向部120r可使用来取代孔145。在图7中,交叉线区域表示结构,且白色区域是电解质填充空间。在替代的设计中,径向部120r可通向堰屏蔽物中的径向孔洞149。在所示的例子中,可使用两个或三个孔洞,具有0.7至1.2mm的孔径。

36.图8绘示另一个分段的堰取样电极组件,其中开口144直接地切至气室中,以提供局部取样电流的路径。相较于图7中的设计,制造被简化,因为开口144可利用立铣刀轻易地切削。此设计有利地使用于局部取样部(部dd)中,因为此设计具有窄集中(narrow focus)的效果而相当适合用以补偿晶片上的局部不规则性,例如划线区域(scribe area)或凹口。此设计可使用于接近不规则性的周向电流调整,但对晶片的剩余部分的周向电流分布或周向均匀性的效用低或没有任何效用。如果处理的晶片没有不规则性时,局部取样部可关掉或不使用。

37.除了绘示于图5中的这些部的数量和构造之外,可使用其他数量和构造。举例来说,分段的堰取样电极组件可替代地具有两个、三个、五个、六个或更多个部,各部连接于分开的电源通道。分段的堰取样电极组件的一个替代实施例可具有1至15度的两个局部部(local segments),由165至179度的两个部分隔或位于165至179度的两个部之间。

38.转至图9,桨54或桨插入件156可具有两个槽162a和162b,位于相邻的叶片160之间。桨54也能具有端开口164a和164b,位于桨的相反侧上,以减少行程范围的端部附近的遮挡。弦形端开口比槽宽。在所示的例子中,叶片高度是13至15mm或14mm,且叶片间距是29至33mm或31mm。

39.在使用时,具有金属种晶层的晶片是装载至头部30的转子中。升举/旋转单元34是翻转和降低晶片至容器组件36中,直到至少种晶层接触上部杯中的阴极电解质。头部30可旋转晶片,以使非均匀电镀因素均等。桨致动器56移动桨54到晶片的下方。根据适用于将特定晶片电镀的预排程时间表,电源98提供独立于第一、第二和第三阳极82、84和86的特定随时间变化的直流(正)电流。

40.电源98亦提供独立于第一、第二、第三和第四实体取样电极的特定随时间变化直流(负)电流,其中电流通过第一、第二、第三和第四虚拟取样电极的取样通道中的取样液和阴极电解质。各虚拟取样部周向地分布电流通过一组可变尺寸开口,此组可变尺寸开口可以是孔或槽(slot)144或145。从入口进入取样膜的上方的取样通道120-123中的阴极电解质流动到气室146中和从气室的顶部中的孔145离开。使用朝上的孔145是让阴极电解质中的捕获气泡从气室146脱离。

41.既然在整个晶片的电流密度可借由调整阳极的电流和虚拟电流取样来进行控制,系统20可通过范围的参数来较佳的处理晶片,而无需置换容器组件36中固定的屏蔽物,置换容器组件36中固定的屏蔽物是耗费时间的过程。电镀系统20也能通过电流控制来提供整体工艺的良好表现。

42.虚拟取样电极部的设计是迫使取样电流通过头部中的接触环的底表面和堰环104的顶表面之间。此致使部aa、bb、cc和dd的效应集中在图7中所示的晶片200的边缘200a附近。如此一来,所需的取样电流降低和更集中控制电场在所提供的晶片的边缘。既然取样电流不同于许多已知系统而相对较低,电镀系统20可连续地处理大数量的晶片,而不会造成实体取样电极被电镀且变得无法操作。

43.径向电流密度控制和周向电流密度控制可借由调整阳极和取样电流来达成。测量先前的晶片的电镀厚度可使用来调整这些电流。最初的电流可从使用工艺条件作为输入(举例为阳极电解质和阴极电解质的浴导电率(bath conductivity)、晶片电流、种晶阻抗(seed resistance)、图案开放区域、图案边缘去除、图案特征尺寸、和期望的电镀厚度)的

模型来设定。

44.由电源98所提供到各取样部的电流或电压是独立地控制,举例为利用10ma至5a的范围中的电流、100ms或更少的电流上升时间、和-0v至-60v的电压。电流和/或电压控制可(经由控制旋转转子的头部中的电机)同步于晶片位置,以准确周向均匀控制晶片的边缘的电镀。晶片位置可随着连续的晶片旋转改变。晶片位置可包括暂停在固定的晶片角度位置或包括改变晶片旋转速度。根据晶片位置和角度旋转速度,电流和/或电压可随着时间增加或减少。根据晶片位置和角度旋转速度与基于先前的晶片的沉积厚度测量(也就是反馈控制),电流和/或电压可随着时间增加或减少。根据晶片位置和角度旋转速度和基于局部边缘图案密度的模型或测量,电流和/或电压可随着时间增加或减少。

45.虚拟样机通道120、121、122和123延伸通过膜62,膜62从阴极电解质分离阳极电解质。此设计更能容忍通道之间的阳极电流泄漏,因为阳极电流针对预期的工艺条件是不接近零。这让膜62的下方的各分隔壁处采用缝隙(gap),以让气泡通过。缝隙是让电流通过这些通道之间,但这些电流泄漏够小,使得阳极电流可调整以进行补偿。

46.多个特定实施方式的具体细节可在不脱离本发明的多个实施方式的精神和范围下以任何适合的方式结合。然而,本发明的多个其他实施方式可针对有关各个别方面的多个特定实施方式,或这些个别方面的特定结合的多个特定实施方式。

47.本发明的多个范例实施方式的上述说明已经针对说明和描述的目的提出。此非意欲为详尽无疑或限制本发明成所述的精确形式,和许多调整和变化是有鉴于上述的教示而可行。数个细节是已经提出,以理解本技术的数种实施方式。然而,本领域技术人员将了解,特定实施方式可在无需一些细节或额外的细节的情况下实现。

48.在已经说明数个实施方式的情况下,本领域技术人员将承认,数种调整、替换构造、和等效物可在不脱离本发明的精神下使用。此外,许多众所周知的工艺和元件并未说明,以避免不必要的混淆本发明。再者,任何特定实施方式的细节可能并非总是呈现在该实施方式的变型中,或可加至其他多个实施方式。

49.当提出一数值范围时,除非文中有明确规范,应理解在该范围的上限和下限之间的各区间数值(intervening value)和至其下限的单位的十分的一亦是具体的公开。在一所述范围中的任何所述数值或区间数值之间的各较小范围以和该所述范围中的任何其他所述或区间数值是包含在内。就所述范围中的任何特定排除限制的情况下,这些较小范围的上限和下限可在范围中独立地包括或排除,且包括于较小范围中的具有这些限制的其中一者、不包括这些限制的任一者或包括这些限制的两者的各范围是亦包含于本发明中。当所述范围包括这些限制的其中一者或两者时,排除这些包括的限制的其中一者或两者的范围亦包含在内。

50.用语“晶片”包括硅晶片以及形成微尺度特征结构于其上的其他基板。如本文所使用和所附的权利要求中,除非内文另有规范,单数形式“一(a、an)”和“该(the)”包括复数指代。用语以上(above)或以下(bellow)是意指设备在其惯常方向中的重力方向。本发明目前已基于明确和理解的目的详细说明。然而,将理解的是,特定改变和调整可在所附的申请专利范围的范围中实现。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1