比例阀控制电路的制作方法

1.本实用新型涉及比例阀控制技术领域,尤其涉及一种比例阀控制电路。

背景技术:

2.比例阀中比例电磁铁的最大位移所需的电流值通常在600-3000ma之间不等,而工业控制标准信号通常是0v~5v或0v~10v或-5v~+5v或-10v~+10v的电压信号,或0-20ma或4-20ma电流信号,控制信号带负载能力很弱,不足以推动比例电磁铁。比例阀放大器起到一个信号匹配的作用,接收微弱的控制信号,输出比例电磁铁所需的电流。现有的比例阀控制器均采用纯硬件电路的搭建方式,导致比例阀控制器比较复杂、电流调节不够灵活、以及电流值精度较低的问题。无法灵活和精确输出比例阀控制器所需的电流信号。

技术实现要素:

3.基于此,有必要针对上述问题,提出了一种比例阀控制电路。

4.一种比例阀控制电路,包括:

5.主控电路,与隔离电路连接,用于向所述隔离电路输出电压信号;

6.所述隔离电路,与驱动电路连接,用于接收所述电压信号并进行隔离输出给所述驱动电路;

7.所述驱动电路,与比例阀连接,用于接收隔离后的电流信号,并输出所述电压信号对应的电流信号给所述比例阀以驱动所述比例阀动作;及

8.反馈电路,输入端与所述驱动电路连接,输出端与所述主控电路连接,用于获取所述驱动电路输出的所述电流信号,并反馈给所述主控电路。

9.在一个实施例中,所述的比例阀控制电路,还包括:

10.供电电路,与所述主控电路、所述隔离电路和所述驱动电路连接,用于为所述主控电路、所述隔离电路和所述驱动电路供电;和

11.通信电路,与所述主控电路连接,用于将外部设备输出的通讯信号传输给所述主控电路。

12.在一个实施例中,所述主控电路包括:主控芯片;

13.所述隔离电路包括:第一隔离芯片和第二隔离芯片;

14.所述主控芯片的通讯输入端与外部设备连接,所述主控芯片的使能脚与所述第二隔离芯片的第一输入脚连接;所述主控芯片的相位同步控制脚与所述第二隔离芯片的第二输入脚连接;所述主控芯片的输入脚与所述第一隔离芯片的第四输入脚连接;所述主控芯片的时钟脚与所述第一隔离芯片的第三输入脚连接;所述主控芯片的片选脚与所述第一隔离芯片的第二输入脚连接;所述主控芯片的错误状态反馈脚与所述第二隔离芯片的第二输出脚连接;所述主控芯片的输出脚与所述第二隔离芯片的第一输出脚连接;所述主控芯片的复位脚与所述第一隔离芯片的第一输入脚连接;所述第一隔离芯片和第二隔离芯片的输出端与所述驱动电路的输入端连接。

15.在一个实施例中,所述驱动电路包括:驱动芯片和端子;

16.所述驱动芯片的复位脚与所述第一隔离芯片的第一输出脚连接;所述驱动芯片的片选脚与所述第一隔离芯片的第二输出脚连接;所述驱动芯片的时钟脚与所述第一隔离芯片的第三输出脚连接;所述驱动芯片的输入脚与所述第一隔离芯片的第四输出脚连接;所述驱动芯片的输出脚与所述第二隔离芯片的第三输入脚连接;所述驱动芯片的错误状态反馈脚与所述第二隔离芯片的第四输入脚连接;所述端子的使能脚与所述第二隔离芯片的第三输出脚连接;所述驱动芯片的相位同步控制脚与所述第二隔离芯片的第四输出脚连接;

17.所述驱动芯片的输出端与所述端子的输入脚连接并接地,所述端子的输出脚与所述反馈电路的输入端连接。

18.在一个实施例中,所述反馈电路包括:第一反馈芯片、第二反馈芯片、第一三极管、第一电阻、第二电阻、第三电阻、第四电阻和第五电阻;

19.所述第一反馈芯片的正极输入端与所述端子的输出脚连接;所述第一电阻的一端与所述第一反馈芯片的正极输入端连接,另一端与所述端子的输出脚连接;所述第二电阻的一端与所述第一反馈芯片的正极输入端连接,另一端接地;所述第一三极管的一端与所述端子的输出脚连接,另一端接地;所述第三电阻的一端与所述第一反馈芯片的正极输入端连接,另一端与所述供电电路连接;所述第四电阻的一端与所述第一反馈芯片的负极输入端连接,另一端与所述第一反馈芯片的输出端连接;所述五电阻的一端与所述第一反馈芯片的输出端连接,另一端与所述第二反馈芯片的电源输入端连接;所述第二反馈芯片的第一输反馈出端与所述主控芯片的第一反馈输入端连接,所述第二反馈芯片的第二输反馈出端与所述主控芯片的第二反馈输入端连接。

20.在一个实施例中,所述供电电路包括:

21.第一供电电路,输入端与第一电源模块连接,输出端与所述主控电路连接,用于为所述主控电路供电;

22.第二供电电路,输入端与第二电源模块连接,输出端与所述隔离电路和所述驱动电路连接,用于为所述隔离电路和所述驱动电路供电;

23.第三供电电路,输入端与第三电源模块连接,输出端与所述主控电路连接,用于为所述主控电路供电;

24.第四供电电路,输入端与第四电源模块连接,输出端与所述通信电路连接,用于为所述通信电路供电。

25.在一个实施例中,所述第一供电电路包括:第五二极管、第六二极管和第四电容;

26.所述第五二极管的阴极与所述第一电源模块的负极连接,所述第五二极管的阳极与接地;所述第六二极管的阳极与所述第五二极管的阴极连接,所述第六二极管的阴极与所述主控电路连接;所述第四电容的一端与所述第五二极管的阳极连接,另一端接地。

27.在一个实施例中,所述第二供电电路包括:第二三极管、第七二极管、第一mos管、第二mos管、第五电容、第六电容、第七电容、第八电容、第九电容、第十电容、第十一电容、第十二电容、第一电感、第二电感、第一降压芯片和第二降压芯片;

28.所述第二三极管的一端与所述第二电源模块连接,另一端接地;所述第五电容与所述第二三极管并联;所述第二mos管的漏极与所述第二电源模块连接,源极与所述第七二极管的阴极连接,栅极与所述第七二极管的阳极连接;所述第二mos管的漏极与所述第一

mos管的漏极连接,源极与所述第一mos管的源极连接,栅极与所述第一mos管的栅极连接;所述第六电容的一端与所述第七二极管的阴极、所述第一降压芯片的电源输入端及所述第二降压芯片的电源输入端连接,另一端接地,所述第一降压芯片的输出端与所述隔离电路连接;所述第七电容的一端与所述第一降压芯片的输出端连接,另一端接地;所述第八电容与所述第七电容并联;

29.所述第二降压芯片的正极输出端与所述第一电感的一端连接,所述第二降压芯片的负极输出端与所述第二电感的一端连接,所述第二降压芯片的接地端接地;所述第一电感的另一端与所述比例阀的正极连接,所述第二电感的另一端与所述比例阀的负极连接;所述第九电容的一端与所述第二降压芯片的正极输出端连接,另一端接地;所述第十电容与所述第九电容并联;所述第十一电容的一端与所述第二降压芯片的负极输出端连接,另一端接地;所述第十二电容与所述第十一电容并联。

30.在一个实施例中,所述第三供电电路包括:第三降压芯片、第四降压芯片、第十三电容、第十四电容和第十五电容;所述第四供电电路包括:第五降压芯片;

31.所述第三降压芯片的电源输入端与所述第三电源模块连接,所述第十三电容的一端与所述第三降压芯片的输出端连接,所述第十三电容的另一端接地,所述第十四电容与所述第十三电容并联;所述第四降压芯片的电源输入端与所述第三降压芯片的输出端连接;所述第十五电容的一端与所述第四降压芯片的输出端连接,所述第十五电容的另一端接地;所述第四降压芯片的输出端与所述主控电路和所述隔离电路连接;

32.所述第五降压芯片的电源输入端与所述第四电源模块连接,输出端与所述通信电路连接。

33.在一个实施例中,所述通信电路包括:第六降压芯片、第十六电容、第十七电容、第十八电容、第六电阻、第三三极管和第四三极管;

34.所述第六降压芯片的电源输入端与所述第五降压芯片的输出端连接,所述第六降压芯片的高电平输出端与所述第三三极管的一端和所述第十六电容的一端连接,所述第十六电容的另一端接地,所述第三三极管的另一端与所述第十八电容的一端连接,所述第十八电容的另一端接地;所述第六降压芯片的低电平输出端与所述第四三极管的一端和所述第十七电容的一端连接,所述第十七电容的另一端接地,所述第四三极管的另一端接地;所述第六电阻的两端分别与所述第六降压芯片的高电平输出端和低电平输出端连接。

35.实施本实用新型实施例,将具有如下有益效果:

36.隔离电路将主控电路输出的电压信号进行隔离处理后再输出给驱动电路,再由驱动电路输出电压信号对应的电流信号给电磁阀以驱动电磁阀动作,反馈电路将隔离处理后的电流信号反馈给主控电路,主控电路进行再次调节输出给比例阀,灵活、精确输出比例阀控制器所需的电流信号对应的电压信号。

附图说明

37.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

38.其中:

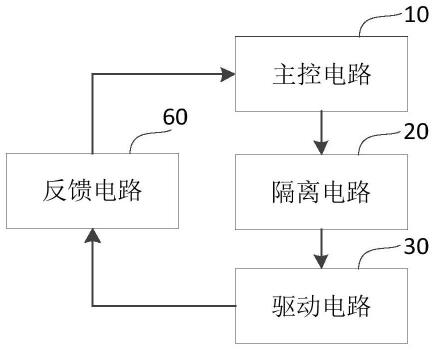

39.图1为一个实施例中比例阀控制电路的结构框图;

40.图2为另一个实施例中比例阀控制电路的结构框图;

41.图3为一个实施例中主控电路的电路图;

42.图4为一个实施例中第一隔离芯片的电路图;

43.图5为一个实施例中第二隔离芯片的电路图;

44.图6为一个实施例中驱动电路的电路图;

45.图7为一个实施例中第一供电电路的电路图;

46.图8为一个实施例中第二供电电路的电路图;

47.图9为一个实施例中第三供电电路的电路图;

48.图10为一个实施例中第四供电电路的电路图;

49.图11为一个实施例中滤波电路的电路图;

50.图12为一个实施例中通信电路的电路图;

51.图13为一个实施例中反馈电路的电路图;

52.图14为一个实施例中指示电路的电路图;

具体实施方式

53.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

54.图1为一个实施例中比例阀控制电路的结构框图,参照图1,比例阀控制电路包括:主控电路10、隔离电路20、驱动电路30和反馈电路60,其中,所述主控电路10与隔离电路20连接,用于向所述隔离电路20输出电压信号;所述隔离电路20与驱动电路30连接,用于接收所述电压信号并进行隔离输出给所述驱动电路30;所述驱动电路30与比例阀连接,用于接收隔离后的电压信号,并输出所述电压信号对应的电流信号给所述比例阀以驱动所述比例阀动作;所述反馈电路60的输入端与所述驱动电路30连接,输出端与所述主控电路10连接,用于获取所述驱动电路30输出的所述电流信号,并反馈给所述主控电路10。隔离电路将主控电路输出的电压信号进行隔离处理后再输出给驱动电路,再由驱动电路输出电压信号对应的电流信号给电磁阀以驱动电磁阀动作,反馈电路将隔离处理后的电流信号反馈给主控电路,主控电路进行再次调节输出给比例阀,灵活、精确输出比例阀控制器所需的电流信号对应的电压信号。

55.在一个实施例中,如图2所示,所述的比例阀控制电路,还包括:供电电路40和通信电路50;其中,所述供电电路40与所述主控电路10、所述隔离电路20和所述驱动电路30连接,用于为所述主控电路10、所述隔离电路20和所述驱动电路30供电;所述通信电路50与所述主控电路10连接,用于将外部设备输出的通讯信号传输给所述主控电路10这里的通讯信号指代外部设备的状态参数。

56.在一个实施例中,如图3所示,所述主控电路10包括:主控芯片u11;如图4和图5所示,所述隔离电路20包括:第一隔离芯片u16和第二隔离芯片u20;其中,所述主控芯片u11的

型号为stm32f407vet6,第一隔离芯片u16的型号为adum1400crwz,第二隔离芯片u20的型号为adum1402crwz-rl;所述主控芯片u11的通讯输入端与外部设备连接,所述主控芯片u11的使能脚pd11与所述第二隔离芯片u20的第一输入脚via连接;所述主控芯片u11的相位同步控制脚pd10与所述第二隔离芯片u20的第二输入脚vib连接;所述主控芯片u11的输入脚pb12与所述第一隔离芯片u16的第四输入脚vid连接;所述主控芯片u11的时钟脚pb13与所述第一隔离芯片u16的第三输入脚vic连接;所述主控芯片u11的片选脚pb14与所述第一隔离芯片u16的第二输入脚vib连接;所述主控芯片u11的错误状态反馈脚pd8与所述第二隔离芯片u20的第二输出脚vod连接;所述主控芯片u11的输出脚pd9与所述第二隔离芯片u20的第一输出脚voc连接;所述主控芯片u11的复位脚pd0与所述第一隔离芯片u16的第一输入脚via连接;所述第一隔离芯片u16和第二隔离芯片u20的输出端与所述驱动电路30的输入端连接。所述第一隔离芯片u16和第二隔离芯片u20为数字隔离芯片,能够将其连接的外部电路与内部电路进行隔离,可以有效的保护内部电路的安全。

57.在一个实施例中,如图6所示,所述驱动电路30包括:驱动芯片u18和端子cn5;其中,所述驱动芯片u18的型号为ad5758,所述驱动芯片u18的复位脚rest与所述第一隔离芯片u16的第一输出脚voa连接;所述驱动芯片u18的片选脚ldac与所述第一隔离芯片u16的第二输出脚vob连接;所述驱动芯片u18的时钟脚sclk与所述第一隔离芯片u16的第三输出脚voc连接;所述驱动芯片u18的输入脚sdi与所述第一隔离芯片u16的第四输出脚vod连接;所述驱动芯片u18的输出脚sdo与所述第二隔离芯片u20的第三输入脚vic连接;所述驱动芯片u18的错误状态反馈脚fault与所述第二隔离芯片u20的第四输入脚vid连接;所述端子cn5的使能脚6与所述第二隔离芯片u20的第三输出脚voa连接;所述驱动芯片u18的相位同步控制脚sync与所述第二隔离芯片u20的第四输出脚vob连接;所述驱动芯片u18的输出端viout与所述端子cn5的输入脚5连接并接地,所述端子cn5的输出脚2与所述反馈电路60的输入端连接。

58.在一个实施例中,如图13所示,所述反馈电路60包括:第一反馈芯片u19、第二反馈芯片u21、第一三极管d14、第一电阻r45、第二电阻r46、第三电阻r38、第四电阻r48和第五电阻r47;其中,所述第一反馈芯片u19的型号为ad8531artz-reel,所述第二反馈芯片u21的型号为adc121s051cimf/nopb;所述第一反馈芯片u19的正极输入端+ina与所述端子cn5的输出脚2连接;所述第一电阻r45的一端与所述第一反馈芯片u19的正极输入端+ina连接,另一端与所述端子cn5的输出脚2连接;所述第二电阻r46的一端与所述第一反馈芯片u19的正极输入端+ina连接,另一端接地;所述第一三极管d14的一端与所述端子cn5的输出脚2连接,另一端接地;所述第三电阻r38的一端与所述第一反馈芯片u19的正极输入端+ina连接,另一端与所述供电电路40连接;所述第四电阻r48的一端与所述第一反馈芯片u19的负极输入端-ina连接,另一端与所述第一反馈芯片u19的输出端outa连接;所述五电阻r47的一端与所述第一反馈芯片u19的输出端outa连接,另一端与所述第二反馈芯片u21的电源输入端vin连接;所述第二反馈芯片u21的第一输反馈出端sclk与所述主控芯片u11的第一反馈输入端pd7连接,所述第二反馈芯片u21的第二输反馈出端cs与所述主控芯片u11的第二反馈输入端pb5连接。

59.在一个实施例中,所述供电电路40包括:第一供电电路401、第二供电电路402、第三供电电路403和第四供电电路404;其中,所述第一供电电路401的输入端与第一电源模块

连接,输出端与所述主控电路10连接,用于为所述主控电路10供电;所述第二供电电路402的输入端与第二电源模块连接,输出端与所述隔离电路20和所述驱动电路30连接,用于为所述隔离电路20和所述驱动电路30供电;所述第三供电电路403的输入端与第三电源模块连接,输出端与所述主控电路10连接,用于为所述主控电路10供电;所述第四供电电路404的输入端与第四电源模块连接,输出端与所述通信电路50连接,用于为所述通信电路50供电。所述第一供电电路401、第二供电电路402、第三供电电路403和第四供电电路404分别与独立的24v电源模块连接,互补干扰及影响,可以保证在其他部分出现问题时,只有该问题电路故障,其他保持正常。

60.在上述实施例的基础上,如图7所示,所述第一供电电路401包括:第五二极管d2、第六二极管d1和第四电容c3;其中,所述第五二极管d2的阴极与所述第一电源模块的负极连接,所述第五二极管d2的阳极与接地;所述第六二极管d1的阳极与所述第五二极管d2的阴极连接,所述第六二极管d1的阴极与所述主控电路10连接;所述第四电容c3的一端与所述第五二极管d2的阳极连接,另一端接地。

61.如图8所示,所述第二供电电路402包括:第二三极管d3、第七二极管d4、第一mos管q1、第二mos管q2、第五电容c4、第六电容c6、第七电容c1、第八电容c2、第九电容c10、第十电容11、第十一电容c12、第十二电容c13、第一电感l1、第二电感l2、第一降压芯片u1和第二降压芯片u4;其中,所述第一降压芯片u1的型号为b2405s-2wr3,所述第二降压芯片u4的型号为wra2415s-3wr2;所述第二三极管d3的一端与所述第二电源模块连接,另一端接地;所述第五电容c4与所述第二三极管d3并联;所述第二mos管q2的漏极与所述第二电源模块连接,源极与所述第七二极管d4的阴极连接,栅极与所述第七二极管d4的阳极连接;所述第二mos管q2的漏极与所述第一mos管q1的漏极连接,源极与所述第一mos管q1的源极连接,栅极与所述第一mos管q1的栅极连接;所述第六电容c6的一端与所述第七二极管d4的阴极、所述第一降压芯片u1的电源输入端vin及所述第二降压芯片u4的电源输入端vin连接,另一端接地,所述第一降压芯片u1的输出端+vo与所述隔离电路20连接;所述第七电容c1的一端与所述第一降压芯片u1的输出端+vo连接,另一端接地;所述第八电容c2与所述第七电容c1并联;所述第二降压芯片u4的正极输出端+vo与所述第一电感l1的一端连接,所述第二降压芯片u4的负极输出端-vo与所述第二电感l2的一端连接,所述第二降压芯片u4的接地端接地;所述第一电感l1的另一端与所述比例阀的正极连接,所述第二电感l2的另一端与所述比例阀的负极连接;所述第九电容c10的一端与所述第二降压芯片u4的正极输出端+vo连接,另一端接地;所述第十电容11与所述第九电容c10并联;所述第十一电容c12的一端与所述第二降压芯片u4的负极输出端-vo连接,另一端接地;所述第十二电容c13与所述第十一电容c12并联。

62.如图9所示,所述第三供电电路403包括:第三降压芯片u2、第四降压芯片u5、第十三电容c14、第十四电容c15和第十五电容c16,其中,所述第三降压芯片u2的型号为b2405s-2wr3,第四降压芯片u5的型号为ams1117-3.3;如图10所示,所述第四供电电路404包括:第五降压芯片u3,其中,所述第五降压芯片u3的型号为b2405s-2wr3;其中,所述第三降压芯片u2的电源输入端与所述第三电源模块连接,所述第十三电容c14的一端与所述第三降压芯片u2的输出端连接,所述第十三电容c14的另一端接地,所述第十四电容c15与所述第十三电容c14并联;所述第四降压芯片u5的电源输入端vin与所述第三降压芯片u2的输出端+vo

连接;所述第十五电容c16的一端与所述第四降压芯片u5的输出端vout连接,所述第十五电容c16的另一端接地;所述第四降压芯片u5的输出端vout与所述主控电路10和所述隔离电路20连接;所述第五降压芯片u3的电源输入端vin与所述第四电源模块连接,输出端vo与所述通信电路50连接。

63.在一个实施例中,如图12所示,所述通信电路50包括:第六降压芯片u6、第十六电容c17、第十七电容c18、第十八电容c19、第六电阻r8、第三三极管d5和第四三极管d6;其中,所述第六降压芯片u6的电源输入端与所述第五降压芯片u3的输出端vo连接,所述第六降压芯片u6的高电平输出端canh与所述第三三极管d5的一端和所述第十六电容c17的一端连接,所述第十六电容c17的另一端接地,所述第三三极管d5的另一端与所述第十八电容c19的一端连接,所述第十八电容c19的另一端接地;所述第六降压芯片u6的低电平输出端canl与所述第四三极管d6的一端和所述第十七电容c18的一端连接,所述第十七电容c18的另一端接地,所述第四三极管d6的另一端接地;所述第六电阻r8的两端分别与所述第六降压芯片u6的高电平输出端canh和低电平输出端canl连接。

64.如图11所示,在上述实施例的基础上,本技术还包括用于将所述主控芯片u12所需的电压进行滤波的滤波电路405,所述滤波电路405包括:第十九电容c39、第二十电容c40、第二十一电容c41、第二十二电容c42、第二十三电容c43和第二十四电容c44;其中,所述第十九电容c39的一端与所述第四降压芯片u5的输出端vout连接,另一端接地;所述第二十电容c40、第二十一电容c41、第二十二电容c42、第二十三电容c43和第二十四电容c44均与所述第十九电容c39并联。

65.如图14所示,在上述实施例的基础上,本技术还包括用于检测比例阀端供电状态的指示电路70,所述指示电路50包括:光耦u8、第七电阻r82和第二十五电容c88;其中,所述光耦u8的型号为tlp521-1xsm,所述光耦u8的正极1与所述第七电阻r82的一端连接,所述光耦u8的负极2接地;所述光耦u8的发射极3接地;所述光耦u8的集电极4与所述第四降压芯片u5的输出端vout级所述主控芯片u11的输入脚pa2连接;所述第七电阻r82的另一端与所述第一降压芯片u1的输出端+vo连接;第二十五电容c88的一端与所述光耦u8的正极1连接,另一端与所述光耦u8的负极2连接。

66.以上所揭露的仅为本实用新型较佳实施例而已,当然不能以此来限定本实用新型之权利范围,因此依本实用新型权利要求所作的等同变化,仍属本实用新型所涵盖的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1