一种膝点检测和采样保持电路

1.本发明属于电源管理技术领域,具体涉及一种膝点检测和采样保持电路。

背景技术:

2.近年来,随着电子设备的发展,电子设备要求电源具有更高的功率密度,更高的效率以及更小的体积。早期主要的电源类型,线性稳压电源已经不能满足这些日益提高的要求,因此,开关电源成为主流的趋势。其中反激式变换器作为隔离式开关变换器的一种,在能够进行电气隔离的同时,具有结构简单,成本低,外围元件少的特点,被广泛地应用在低功率消费类电子产品中。原边反馈反激式变换器相较于副边反馈反激式变换器,原理更加简单,成本更低,同时省去了光耦元件而具有高可靠性的优点,而受到市场青睐。

3.对于原边反馈反激式变换器而言,如图1所示,输出电压信息在副边导通原边关断的时候,通过原边绕组反激到原边体现在功率管漏端电压v

sw

上,再通过vin钳位电路使得反馈电阻r

fb

两端的电压仅包含反激电压信息,再通过参考电阻v

ref

产生反馈电压v

fb

,反馈电压v

fb

传递到膝点检测和采样保持电路中,系统通过采样得到的输出电压信息对占空比进行调节,从而实现恒定电压输出。因此,输出电压的准确检测才能够保证系统的输出电压有较高的精度。如图2所示,膝点电压为副边电感电流为零的时刻的功率管漏端v

sw

电压值,即为a点。在膝点处,副边的寄生阻抗产生的压降由于副边电感电流为零而不对v

sw

产生影响,此时的v

sw

能够更加精确地描述输出电压的信息。因此,准确的膝点检测对高精度的原边反馈反激式变换器来说尤为重要。

4.现有的膝点检测和采样保持方案中,有使用多路电路进行依次采样,得到多个采样值,通过上一个采样点的电压减去固定的电压值与当前采样电压值进行对比,得到真实采样值,再将最真实的采样值送到后续模块的采样方法,然而这种方法需要使用多个电容来对采样值进行存储,不利于片内集成,而且对多路电路依次采样的控制电路也较为复杂,且采样的精确度不高。数字辅助利用模数转换器adc和数模转换器dac也常被用于精确膝点检测,但是成本通常过于高昂。

技术实现要素:

5.本发明主要设计实现了一种高精度的膝点检测和采样保持电路,利用电阻和电容对反馈信号进行延时,将延时后的信号与反馈信号输入到比较器中进行比较。在反馈信号达到膝点时,会急剧下降,此时反馈信号的电压值会小于经过延时的反馈信号,从而使得比较器翻转,得到膝点到达的信号,检测到膝点的信号控制采样开关打开,采样电容存储的膝点电压值传输的保持电容,完成膝点采样工作,得到精确的膝点电压值。

6.为实现上述目的,本发明的技术方案为:

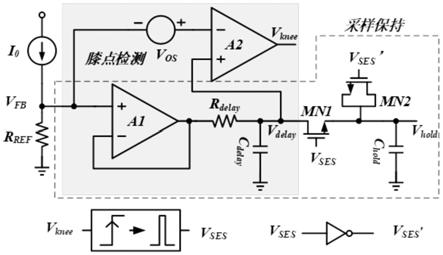

7.一种膝点检测和采样保持电路,用于检测原边反馈反激式变换器在副边电感电流为零时的膝点电压,包括第一运算放大器、第二运算放大器、第一nmos管、第二nmos管、电阻、第一电容、第二电容和电压源;

8.所述第一运算放大器的同相输入端接反馈电压,其反相输入端接其输出端,第一运算放大器的输出端依次通过电阻和第一电容后接地,将电阻和第一电容的连接点输出的电压信号定义为延迟电压;

9.所述第二运算放大器的同相输入端接延迟电压,其反相输入端接电压源的正端,电压源的负端接反馈电压,将第二运算放大器的输出电压定义为判断电压,所述电压源产生固定失调电压;

10.所述第一nmos管的漏极接延迟电压,其栅极接第一使能信号;

11.所述第二nmos管的源极和漏极接第一nmos管的源极,第二nmos管的栅极接第一使能信号的反向信号,第一nmos管源极与第二nmos管源漏极的连接点通过第二电容后接地,将第一nmos管源极、第二nmos管源漏极、第二电容的连接点输出定义为膝点电压保持电压;

12.当检测到所述判断电压从低电平翻高,表示第一电容采集到膝点电压,并触发高电平窄脉冲信号作为第一使能信号,使第一nmos管导通,将第一电容上的膝点电压转移到第二电容上,从而得到膝点电压保持电压;

13.所述第二nmos管保持与第一nmos管相反的开关动作,用于削减第一nmos管在开关动作中的沟道电荷注入效应和时钟馈通效应对膝点电压的采样造成的误差。

14.本发明的有益效果为:能得到精确的膝点电压值。

附图说明

15.图1原边反馈反激式变换器原理图。

16.图2功率管漏端电压和电感电流的波形图。

17.图3本发明提出的膝点检测和采样保持电路框架图。

18.图4本发明提出的膝点检测波形图。

具体实施方式

19.下面结合附图,对本发明技术方案进行详细描述:

20.应用本发明提出的原边反激式变换器的原理图如图1所示。功率管漏端电压和电感电流的波形如图2所示,在副边开启的toff时间段内,t0‑

t1受到漏感和功率管寄生电容的影响,v

sw

会出现振铃从而使得v

fb

也会出现振铃,系统为了避免误触发,一般会选择屏蔽这段时间。振铃结束之后,t1‑

t2内,由于副边寄生阻抗和副边电流下降的影响,导致v

sw

会有下降到趋势,在t2时刻,副边电流降为0,到达膝点。膝点之后,v

sw

会迅速衰减,膝点前后,v

sw

的电压有明显变化。因此在toff时间段内,功率管m

n

的漏端电压v

sw

可以表示为:

21.v

sw

(t)=v

in

+n

ps

(v

out

+v

f

+i

s

(t)r

s

)

22.其中,vin为输入电压,n

ps

为原边和副边变压器的匝比,v

f

为副边二极管的导通压降,r

s

为副边等效阻抗,i

s

为副边电感电流,i

s

随时间的变化可以表示为:

[0023][0024]

其中,i

peak

为原边峰值电感电流,v

out

为输出电压,l

p

为原边电感,t

sw

为一个开关周期,t

on

为原边导通时间,t

dcm

为副边导通结束到下一个开关周期的时间。

[0025]

在t2‑

t4时间段内,受到功率管漏端寄生电容c

p

和原边电感l

p

的影响,v

sw

会发生谐

振,这个时间段内v

sw

可以表示为:

[0026][0027]

需要注意的是,实际上退磁时间t

off

时间后,v

sw

的振荡并非围绕v

in

等辐振荡,而是阻尼振荡。在膝点之后,v

sw

第一个下降沿t2‑

t3内的变化斜率为:

[0028][0029]

图3为本发明根据v

sw

电压波形设计的膝点检测和采样保持电路。电路的主体由两个运放a1和a2以及电阻r

delay

和电容c

delay

构成。运放a1接成buffer结构,将电压v

fb

传递到由电阻r

delay

和电容c

delay

构成的一节低通滤波器中,低筒滤波器输出信号v

delay

。a2用作比较器,在其负向输入端引入固定失调v

os

,然后连接反馈电压v

fb

,正向输入端接v

delay

信号,比较器输出信号v

knee

从低电平翻高,表征电容c

delay

采集到膝点电压。

[0030]

由图1所示,系统通过vin钳位电路将反馈电阻r

fb

左端的电压钳位到v

in

,因此反馈电压可以表示为:

[0031][0032]

其中r

ref

为参考电阻。

[0033]

则v

delay

可表示为:

[0034][0035]

膝点检测的波形图如图4所示,在t0

‑

t1时间段,由于v

sw

变化缓慢,v

fb

的变化也会比较缓慢,所以经过低通滤波器几乎没有相位衰减和幅度衰减,v

delay

能够很好地跟踪v

fb

。但是,在此期间v

fb

随着副边电感电流的减小而缓慢向下衰减,为了防止在这段时间内,比较器a2误触发使得信号v

knee

错误翻转,所以在比较器a2的负向输入端引入失调电压v

os

,比较器a2的翻转条件为:

[0036]

v

delay

‑

v

fb

=v

os

[0037]

在图4的t1时刻,v

fb

开始高频振荡,v

delay

相比于v

fb

出现相位衰减,v

fb

波形中t1时刻的膝点在v

delay

波形中滞后到t1’

时刻,衰减的相位为:

[0038][0039]

则v

delay

滞后于v

fb

的时间为:

[0040][0041]

为了保证比较器a2能在t1’

时刻翻转,上述的延时间需要满足关系:

[0042]

t

′1‑

t1=δt1+δt2[0043]

其中δt1是从t1时刻v

fb

开始谐振到触发比较器翻转的时间差,满足关系:

[0044][0045]

即:

[0046][0047]

δt2表示触发比较器翻转到比较器输出翻转信号之间的延时。

[0048]

因此,需要对比较器的失调电压vos和低通滤波器rdelay和cdelay进行折中选择。首先需要保证在图4的t0‑

t1阶段,比较器a2不会发生翻转且不宜过大,然后在这个基础上对低通滤波器进行设计,保证

[0049][0050]

需要说明的是,为了防止谐振的第二个峰值点误触发比较器,当v

knee

翻转后,需要将比较器锁住,直到下一个开关周期,功率管m

n

断开,进入退磁阶段,再解锁比较器a2。

[0051]

当v

knee

的信号从低翻高时,意味着膝点的电压已经储存在c

delay

中,此时,只要完成对膝点电压的采样保持,也就完成了对输出电压的采样。如图3所示,v

knee

信号翻转,触发一段高电平窄脉冲信号v

sen

。当v

sen

处于高电平的窄脉冲时间段内,开关管mn1导通,将电容c

delay

上存储的膝点电压信息转移到保持电容c

hold

上。且由于此时v

fb

电位在振荡,而c

delay

已经采集到了膝点电压的信息,buffer的输出不再对输入进行追踪,若buffer的输出继续追踪输入,会引入误差。高电平窄脉冲结束后,mn1开关断开,采样保持结束。由于mn1管导通后,开关管mn1等效为一个小电阻,会延缓保持电容c

hold

上的电压建立速度,因此需要v

sen

维持一段时间的高电平,保证c

hold

电容上的电压建立。mn2管作为虚拟开关管,保持与mn1相反的开关动作,削减mn1管在开关动作中的沟道电荷注入效应和时钟馈通效应对膝点电压的采样造成的误差。在设计过程中,需要保证mn1和mn2在尺寸上有2:1的匹配关系。

[0052]

采样保持的过程是一个电荷分享的过程,因此当采样保持结束后,c

delay

和c

hold

电容上的v

hold

电压值比实际的膝点电压值低。根据电荷守恒可得,采样保持结束后的v

hold

为:

[0053][0054]

c

delay

越大,c

hold

越小,v

hold

与膝点电压的误差越小,通常需要让c

delay

的容值是c

hold

容值的十倍及以上。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1