芯片的测试垫结构的制作方法

1.本发明是关于一种芯片的测试垫结构,尤其指一种能确保探针接触测试垫的结构。

背景技术:

2.随着时代的发展,芯片设计公司依照客户的需求及产品的功能,设计相关的电路与电路布局,并提供给晶圆厂以生产芯片。芯片被制造而尚未从晶圆被切割下来前,为了确定晶圆上的芯片的电路的功能是否可以正常运作而进行预期的功能,晶圆须进行芯片针测(chip probing,cp)以确保每一芯片的质量。

3.接续上述,测试晶圆的检测装置具有探针卡(probe card),探针卡具有多个探针,该些探针会接触芯片的测试垫,以传递讯号或者电源至芯片,以测试芯片是否可以正常运作。

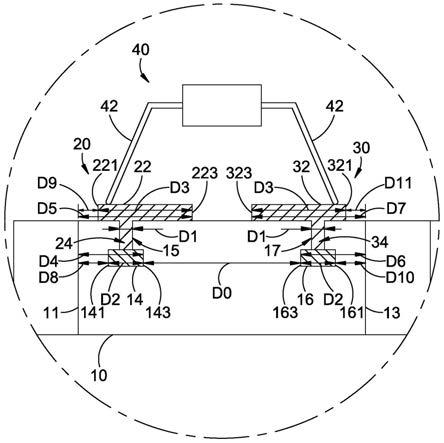

4.请参阅图1,其为习知测试垫结构的剖视示意图。如图所示,一晶圆70包含有多个芯片80,每一个芯片80包含多个测试垫82与多个开孔84,该多个测试垫82位于芯片80内,该多个开孔84对应于该多个测试垫82,并连通于该多个测试垫82与芯片80的表面。一检测装置40的两探针42会进入该多个开孔84,而接触该多个测试垫82,以传递讯号或者电源至芯片80,而测试芯片80。然而,基于制程误差,例如蚀刻误差、光罩对位误差等,可能会导致开孔84的截面积接近等于探针42的截面积,如此探针42不易进入开孔84,而不易接触测试垫82或者没有确实接触测试垫82,如此会降低测试质量。此外,甚至开孔84的截面积小于探针42的截面积,如此探针42无法进入开孔84,而无法接触测试垫82,即无法测试芯片80。此外,若开孔84所在位置有所偏离,左右相邻的两开孔84间的距离会偏离一预定距离,如此两探针42即无法同时对位到左右相邻的两开孔84,而无法进入开孔84,即无法测试芯片80。

5.基于上述可知,习知测试垫结构会影响检测装置的测试质量,甚至导致检测装置无法测试芯片。因此,产业界需要一种确保探针能确实接触芯片的测试垫的结构,以提高测试质量。

技术实现要素:

6.本发明的一目的在于提供一种芯片的测试垫结构,其包含多个内测试垫与多个延伸测试垫,该多个延伸测试垫连接该多个内测试垫,以增加可被探针接触的面积,如此探针可以确实接触延伸测试垫,透过延伸测试垫传输讯号或者电源至内测试垫,以测试芯片,如此即可提高测试质量。

7.本发明的一目的在于提供一种芯片的测试垫结构,其可被探针接触的面积增加,探针因磨损而截面积变大时,探针仍可接触到测试垫结构,而不需要更换探针,如此可增加探针的使用寿命,可以降低测试成本。

8.本发明的一目的在于提供一种芯片的测试垫结构,其可被探针接触的面积增加而具有较大的对位范围,便于探针对位,可以改善探针不易对位情况。

9.本发明提供一种芯片的测试垫结构,其包含多个第一内测试垫、多个第二内测试垫、多个第一延伸测试垫、多个第二延伸测试垫。该多个第一内测试垫与该多个第二内测试垫设置于一芯片,且该多个第二内测试垫与该多个第一内测试垫之间具有一距离。该多个第一延伸测试垫与该多个第二延伸测试垫设置于芯片,该多个第一延伸测试垫连接该多个第一内测试垫,且位于该多个第一内测试垫上方,该多个第二延伸测试垫连接该多个第二内测试垫,且位于该多个第二内测试垫上方。该多个第一延伸测试垫与该多个第二延伸测试垫增加可被探针接触的面积,探针可以确实接触该多个第一延伸测试垫与该多个第二延伸测试垫,而透过该多个第一延伸测试垫与该多个第二延伸测试垫传输讯号或者电源至该多个第一内测试垫与该多个第二内测试垫,以测试芯片。

附图说明

图1:其为习知测试垫结构的剖视示意图;图2:其为本发明的芯片的测试垫结构的第一实施例的俯视示意图;图3:其为本发明的芯片的测试垫结构的第一实施例的剖视示意图;图4a及图4b:其为图3的局部放大示意图;图5:其为本发明的芯片的测试垫结构的第二实施例的俯视示意图;图6:其为本发明的芯片的测试垫结构的第二实施例的剖视示意图;图7:其为图6的局部放大示意图;以及图8:其为本发明的芯片的测试垫结构被移除部分延伸测试垫的一实施例的剖视示意图。【图号对照说明】1

ꢀꢀꢀꢀ

晶圆10

ꢀꢀꢀ

芯片11

ꢀꢀꢀ

第一侧面13

ꢀꢀꢀ

第二侧面14

ꢀꢀꢀ

第一内测试垫141

ꢀꢀ

第一侧面143

ꢀꢀ

第二侧面15

ꢀꢀꢀ

第一穿孔16

ꢀꢀꢀ

第二内测试垫161

ꢀꢀ

第一侧面163

ꢀꢀ

第二侧面17

ꢀꢀꢀ

第二穿孔20

ꢀꢀꢀ

第一延伸测试垫22

ꢀꢀꢀ

第一本体221

ꢀꢀ

第一侧面223

ꢀꢀ

第二侧面24

ꢀꢀꢀ

第一连接件30

ꢀꢀꢀ

第二延伸测试垫

32

ꢀꢀꢀ

第二本体321

ꢀꢀ

第一侧面323

ꢀꢀ

第二侧面34

ꢀꢀꢀ

第二连接件40

ꢀꢀꢀ

检测装置42

ꢀꢀꢀ

探针50

ꢀꢀꢀ

切割道70

ꢀꢀꢀ

晶圆80

ꢀꢀꢀ

芯片82

ꢀꢀꢀ

测试垫84

ꢀꢀꢀ

开孔d0

ꢀꢀꢀ

距离d1

ꢀꢀꢀ

孔径d2

ꢀꢀꢀ

长度d3

ꢀꢀ

长度d4

ꢀꢀ

距离d5

ꢀꢀ

距离d6

ꢀꢀ

距离d7 距离d8

ꢀꢀ

距离d9

ꢀꢀ

距离d10 距离d11 距离d12 距离d13 第一测试距离d14 第二测试距离d15 探针距离w1

ꢀꢀ

宽度w2

ꢀꢀ

宽度

具体实施方式

10.为了使本发明的结构特征及所达成的功效有更进一步的了解与认识,特用较佳的实施例及配合详细的说明,说明如下:

11.请参阅图2及图3,图2与图3分别为本发明的芯片的测试垫结构的第一实施例的俯视示意图与剖视示意图。如图所示,一晶圆1包含多个芯片10与多条切割道50,该些条切割道50位于该多个芯片10之间。切割装置可沿着切割道50切割晶圆1,以取得该多个芯片10。

12.再次参阅图2及图3,以及请参阅图4a,图4a为图3的局部放大示意图。本发明的测试垫结构包含多个第一内测试垫14、多个第二内测试垫16、多个第一延伸测试垫20以及多个第二延伸测试垫30,其皆设置于芯片10。于一实施例中,该多个第一内测试垫14与该多个

第二内测试垫16位于芯片10内,该多个第一内测试垫14位于芯片10的一第一侧,该多个第二内测试垫16位于芯片10的一第二侧。该多个第一内测试垫14具有一第一侧面141与一第二侧面143,该多个第二内测试垫16具有一第一侧面161与一第二侧面163,第二侧面143与第二侧面163相对,且两者之间具有一距离d0,其表示该多个第一内测试垫14与该多个第二内测试垫16之间具有距离d0。该多个第一延伸测试垫20分别连接该多个第一内测试垫14,并位于该多个第一内测试垫14上方。该多个第二延伸测试垫30分别连接该多个第二内测试垫16,并位于该多个第二内测试垫16上方。

13.再次参阅图2及图4a。于本实施例中,芯片10包含多个第一穿孔15与多个第二穿孔17,该多个第一穿孔15对应该多个第一内测试垫14,且位于该多个第一内测试垫14的上方,该多个第二穿孔17对应该多个第二内测试垫16,且位于其上方。该多个第一延伸测试垫20各别包含一第一本体22以及一第一连接件24,第一本体22位于芯片10的表面,第一连接件24插设于第一穿孔15,且第一连接件24连接第一本体22与第一内测试垫14。该多个第二延伸测试垫30与该多个第一延伸测试垫20之间具有一距离,该多个第二延伸测试垫30各别包含一第二本体32以及一第二连接件34,第二本体32位于芯片10的表面,第二连接件34插设于第二穿孔17,且第二连接件34连接第二本体32与第二内测试垫16。

14.于本实施例中,第一本体22往靠近第二本体32的方向延伸,其表示第一延伸测试垫20往靠近第二延伸测试垫30的方向延伸。第二本体32往靠近第一本体22的方向延伸,其表示第二延伸测试垫30往靠近第一延伸测试垫20的方向延伸。如图4a所示,第一内测试垫14的第二侧面143相较于第一内测试垫14的第一侧面141较远离芯片10的第一侧面11。第一延伸测试垫20的第一本体22具有一第一侧面221与一第二侧面223,第二侧面223相较于第一侧面221较远离芯片10的第一侧面11。第一内测试垫14的第二侧面143与芯片10的第一侧面11之间具有一距离d4,第一延伸测试垫20的第二侧面223与芯片10的第一侧面11之间具有一距离d5,且距离d5大于距离d4。第二内测试垫16的第二侧面163相较于第二内测试垫16的第一侧面161较远离芯片10的第二侧面13。第二延伸测试垫30的第二本体32具有一第一侧面321与一第二侧面323,第二侧面323相较于第一侧面321较远离芯片10的第二侧面13,且第二侧面323相对于第二侧面223。第二内测试垫16的第二侧面163与芯片10的第二侧面13之间具有一距离d6,第二延伸测试垫30的第二侧面323与芯片10的第二侧面13之间具有一距离d7,且距离d7大于距离d6。

15.再次参阅图4a,第一内测试垫14的第一侧面141与芯片10的第一侧面11之间具有一距离d8,第一延伸测试垫20的第一侧面221与芯片10的第一侧面11之间具有一距离d9,且距离d9小于距离d8,其表示第一延伸测试垫20亦往远离第二延伸测试垫30的方向延伸。第二内测试垫16的第一侧面161与芯片10的第二侧面13之间具有一距离d10,第二延伸测试垫30的第一侧面321与芯片10的第二侧面13之间具有一距离d11,且距离d11小于距离d10,其表示第二延伸测试垫30亦往远离第一延伸测试垫20的方向延伸。

16.如图4a所示,第一穿孔15以及第二穿孔17各别具有一孔径d1,代表第一穿孔15以及第二穿孔17的开口大小。第一内测试垫14与第二内测试垫16各别具有一长度d2,第一内测试垫14的长度与第二内测试垫16的长度亦可不同。第一本体22以及第二本体32各别具有一长度d3,且长度d3大于孔径d1与长度d2,其表示第一本体22的上表面的面积,也就是第一延伸测试垫20的表面的面积,大于第一穿孔15的开口面积以及第一内测试垫14的表面的面

积(如图3所示);同样地,第二本体32的上表面的面积,也就是第二延伸测试垫30的表面的面积,大于第二穿孔17的开口面积以及第二内测试垫16的表面的面积(如图3所示)。于一实施例中,第一本体22的长度与第二本体32的长度亦可不同。此外,如图2所示,第一内测试垫14与第二内测试垫16各别具有一宽度w1。第一内测试垫14的宽度与第二内测试垫16的宽度亦可不同。第一本体22以及第二本体32各别具有一宽度w2,且宽度w2大于宽度w1。于一实施例中,宽度w2可等于宽度w1,且第一本体22的宽度与第二本体32的宽度亦可不同。

17.再次参阅图2及参阅图4b,图4b同于图4a为图3的局部放大示意图。如图所示,一检测装置40用于检测芯片10,检测装置40包含二探针42,二探针42可接触第一延伸测试垫20的第一本体22及第二延伸测试垫30的第二本体32。第一穿孔15及第二穿孔17之间具有一距离d12,第一延伸测试垫20的第一侧面221与第二延伸测试垫30的第一侧面321之间具有一第一测试距离d13,第一延伸测试垫20的第二侧面223与第二延伸测试垫30的第二侧面323之间具有一第二测试距离d14,第一测试距离d13大于第二测试距离d14。二探针42之间具有一探针距离d15。本实施例中,距离d12及第二测试距离d14小于探针距离d15,第一测试距离d13大于探针距离d15。二探针42能接触第一延伸测试垫20及第二延伸测试垫30的表面,而透过第一延伸测试垫20与第二延伸测试垫30传输讯号或者电源至第一内测试垫14与第二内测试垫16,以检测芯片10。

18.由上述说明可知,探针42不需进入穿孔15、17,仅接触第一延伸测试垫20与第二延伸测试垫30,即可测试芯片10,其相当于增加可被探针42接触的面积。此外,第一延伸测试垫20与第二延伸测试垫30的面积可大于第一内测试垫14与第二内测试垫16的面积,如此更提高可被探针42接触的面积。另外,第一延伸测试垫20与第二延伸测试垫30可被探针42接触的面积大,相当于具有较大的对位范围,如此便于探针42对位,纵使探针42长时间使用下,两探针42间的探针距离d15变大或者变小仍可对位第一延伸测试垫20与第二延伸测试垫30,而可不需要更换探针42,又探针42因磨损而截面积变大时,探针42仍可确实接触第一延伸测试垫20与第二延伸测试垫30,不需要更换探针42,如此可增加探针42的使用寿命,可以降低测试成本。

19.请参阅图5、图6及图7,图5与图6分别为本发明的芯片的测试垫结构的第二实施例的俯视示意图与剖视示意图;图7为图6的局部放大示意图。如图所示,第一延伸测试垫20的第一本体22往远离第二延伸测试垫30的方向延伸,且可延伸出芯片10至切割道50,进一步增加第一本体22的面积,同理第二延伸测试垫30的第二本体32往远离第一延伸测试垫20的方向延伸,且可延伸出芯片10至切割道50,增加第二本体32的面积。

20.请参阅图8,其为本发明的芯片的测试垫结构被移除部分延伸测试垫的一实施例的剖视示意图。检测装置检测完位于晶圆1的该多个芯片10后,可移除第一延伸测试垫20的第一本体22的一部分与第二延伸测试垫30的第二本体32的一部分。如此,从晶圆1被切割下来的该多个芯片10仍保留第一延伸测试垫20与第二延伸测试垫30,而可进行测试。于另一实施例中,可完全移除第一延伸测试垫20与第二延伸测试垫30,即完全移除第一本体22、第一连接件24、第二本体32及第二连接件34。于一实施例中,第一延伸测试垫20与第二延伸测试垫30的材料可不同于第一内测试垫14与第二内测试垫16的材料,如此可利用特定蚀刻剂移除第一延伸测试垫20与第二延伸测试垫30而不会移除第一内测试垫14与第二内测试垫16。

21.综上所述,本发明提供一种芯片的测试垫结构,其包含延伸测试垫,而连接内测试垫,如此探针接触延伸测试垫就可透过延伸测试垫传输讯号或电源至内测试垫,以测试芯片。

22.上文仅为本发明的较佳实施例而已,并非用来限定本发明实施的范围,凡依本发明权利要求范围所述的形状、构造、特征及精神所为的均等变化与修饰,均应包括于本发明的权利要求范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1