检测源漏间漏电的电压衬度方法与流程

检测源漏间漏电的电压衬度方法

1.技术领域

2.本发明涉及集成电路设计及失效分析领域,特别是指一种集成电路失效分析中,检测源漏漏电的电压衬度方法。

背景技术:

3.在集成电路制造过程中,由于工艺缺陷、设备误差甚至是人为等原因,可能会在芯片内部造成短路。这种短路可以是多晶硅与多晶硅、多晶硅与金属、金属与金属、金属与有源区、有源区与有源区及有源区与多晶硅之间发生。而这种异常短接却可以引起芯片功耗增大、功能异常、数据丢失等严重问题。能够及时监测发现集成电路制造过程中发生的缺陷对于良率的提升非常重要,由于制造工艺的特征尺寸不断的缩小,发生异常短接的位置可能会比较微小,在不确定具体短接位置的情况下,查找这些异常可能会非常困难,容易被忽略。

4.目前业内普遍采用的检测方法是用聚焦离子束(fib:focus ion beam)切割设备,步进式推进,对问题芯片怀疑区域进行大面积断面观察,从而找到异常短接的位置。这种方法操作时由于缺陷位置不确定,目的性不强,需要耗费大量的人力及设备机时资源,效果却不佳。而且,由于分辨率的问题,很可能弱短接在切割的过程中被遗忘或忽略。

5.因此,需要一种更高效的电压衬度方法来检测分析这些异常问题。电压衬度(vc:voltage contrast)是sem中由于试样表面电位差别而形成的衬度。当电子束(离子束)扫描样品表面时,会与表面产生非弹性碰撞,并放射出一些低能(≤50ev)的二次电子。这些电子一般仅能离开表面30nm以内,利用侦测器前端外加几百伏特的电压将这些二次电子吸收并成像。样品表面的电位会影响二次电子的产率,电位越高放射二次电子量越少,电位越低放射量越多,利用此电压衬度像(vc:voltage contrast)可以判断连接线(包括金属、多晶、接触孔等)的短路与断路。

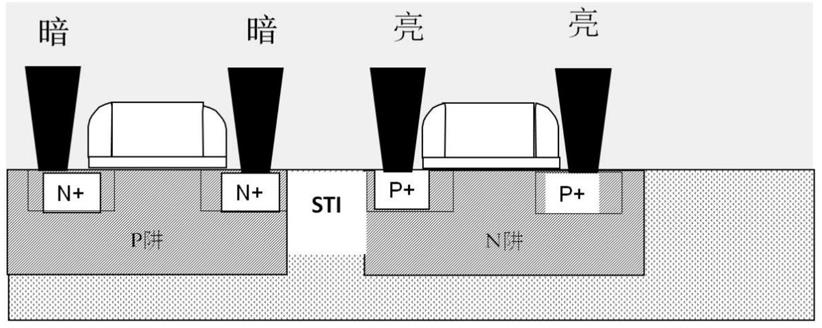

6.实际应用中,一般采用低压电子束或者高压离子束进行电压衬度实验,此时浮栅以及其连接孔显示为暗。利用对样品表面电位状态敏感的信号,如二次电子,作为显像管的调制信号,可得到分辨率较高的、明暗对比明显的电压衬度像,能有效地显示试样表面的微观形貌。由于nmos s&d 均是暗的,此时若源漏之间有漏电,通过contact 电压衬度,无法确认是否异常。如图1所示。若s & d之间存在短路,因为两者在电压衬度下均表现为暗,所以电压衬度无法发现异常。

技术实现要素:

7.本发明所要解决的技术问题在于提供一种检测源漏间漏电的电压衬度方法,确认mos管的源漏间是否漏电。

8.为解决上述问题,本发明所述的检测源漏间漏电的电压衬度方法,包含如下的步

骤:第一步,对芯片样品进行研磨,研磨至第一层金属m1露出。

9.第二步,对芯片样品怀疑区域进行初始的电压衬度像,进行初步判断;对于nmos和pmos之间有互联情况的,则nmos的源漏端的电压衬度像分两种情况:仅有与pmos连接的一端的电压衬度像为亮,或者是nmos的源端和漏端的衬度像均为亮。

10.第三步,进一步研磨至接触孔层次,再次进行电压衬度,此时若nmos源端和漏端的电压衬度像均为暗,则证明nmos的源端和漏端之间存在漏电;若nmos仅有与pmos相连的一端为亮,则证明原nmos的源端和漏端之间不漏电。

11.对于nmos和pmos之间没有互联情况时,上述步骤无法验证,则再进行第四步。

12.第四步,寻找距离怀疑区域最近的电压衬度像为亮的接触孔层,将pmos的的源、漏端与nmos的源端或者漏端中的任意一端进行人工的电性连接,再次进行电压衬度像进行判定。

13.进一步地改进是,所述第二步中,初始电压衬度像采用低压电子束或者是高压离子束形成。

14.进一步地改进是,所述第二步中,由于pmos与nmos之间有互联,则电压衬度时,nmos与pmos连接的一端的电压衬度像会被pmos的电压衬度像带亮;当nmos的源漏端之间存在漏电时,则nmos的源漏端的电压衬度像均为亮;当nmos的源漏端之间不存在漏电时,则只有与pmos连接的一端的电压衬度像为亮。

15.进一步地改进是,所述第四步中,通过生长铂金属条将怀疑区域与最近的发亮的金属进行连接,再次进行第二步中的判断。

16.进一步地改进是,所述的生长铂金属条的方式包括电镀。

17.进一步地改进是,所述第四步中,如果nmos未与pmos直接连接的剩余一端电压衬度像显示为亮,则证明nmos的源漏端之间存在漏电,若nmos的剩余一端的电压衬度显示为暗,则表明nmos的源漏端之间不存在漏电。

18.进一步地改进是,对于pmos和nmos之间没有互联的,能简化步骤,直接研磨到接触孔层次,然后进行人工互联,进行电压衬度。

19.进一步地改进是,若nmos管中源极或者漏极被任意一方的电压衬度像带亮,则可判断源漏之间漏电。

20.本发明所述的检测源漏间漏电的电压衬度方法,通过生长铂金属条进行手动建立连接,改变nmos器件电压衬度的明暗,达到检测源漏间是否漏电的目的。

附图说明

21.图1 是cmos研磨至接触孔层次的正常状态下的电压衬度像。

22.图2 是研磨至第一金属层后的正常状态下的电压衬度像。

23.图3 是研磨至第一金属层后的异常状态下的电压衬度像。

24.图4 是nmos源漏之间有漏电,研磨至接触孔层次的电压衬度像,和正常状态下电压衬度像是相同的。

25.图5 是研磨至接触孔层次且生长金属条手动连接后的电压衬度像。

26.图6 是第一金属层的俯视平面电压衬度示意图。

27.图7 是接触孔层的俯视平面电压衬度示意图。

28.图8 是接触孔层的俯视平面tem(透镜电子显微镜)验证示意图。

29.图9 是本发明方法步骤流程图。

具体实施方式

30.以下结合附图给出本发明的具体实施方式,对本发明中的技术方案进行清楚、完整的描述,但本发明不限于以下的实施方式。显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比率,仅用于方便、明晰地辅助说明本发明实施例的目的。本领域普通技术人员在不做出创造性劳动的前提下所获得的所有其它实施例,都属于本发明保护的范围。

31.应当理解,本发明能够以不同形式实施,而不应当解释为局限于这里提出的实施例。相反地,提供这些实施例将使公开彻底和完全,并且将本发明的范围完全地传递给本领域技术人员。在附图中,为了清楚,层和区的尺寸以及相对尺寸可能被夸大,自始至终相同附图标记表示相同的元件。应当明白,当元件或层被称为“在

…

上”、“与

…

相邻”、“连接到”或“耦合到”其它元件或层时,其可以直接地在其它元件或层上、与之相邻、连接或耦合到其它元件或层,或者可以存在居间的元件或层。相反,当元件被称为“直接在

…

上”、“与

…

直接相邻”、“直接连接到”或“直接耦合到”其它元件或层时,则不存在居间的元件或层。应当明白,尽管可使用术语第一、第二、第三等描述各种元件、部件、区、层和/或部分,这些元件、部件、区、层和/或部分不应当被这些术语限制。这些术语仅仅用来区分一个元件、部件、区、层或部分与另一个元件、部件、区、层或部分。因此,在不脱离本发明教导之下,下面讨论的第一元件、部件、区、层或部分可表示为第二元件、部件、区、层或部分。

32.为了使本发明实现的技术手段、创作特征、达成目的与功效易于明白了解,下面结合具体图示,进一步阐述本发明。

33.本发明所述的检测源漏间漏电的电压衬度方法,包含如下的步骤:第一步,对芯片样品进行研磨,研磨至第一层金属m1露出。

34.第二步,进行初始的电压衬度像,进行初步判断,初始电压衬度像采用低压电子束或者是高压离子束形成。如图2及图3所示,图2中是对芯片样品研磨至第一层金属m1之后形成的电压衬度,在正常情况下的电压衬度像是pmos的源端和漏端亮,nmos的源端和漏端是暗,但由于图2中所示的结构,pmos与nmos之间有金属连接,假定pmos的源端与nmos的漏端由一段金属相连,那么nmos的漏端由于与pmos连接所以其电压衬度也会被pmos带亮,这是该连接结构下的正常情况的电压衬度像。而如果nmos的源漏之间再存在漏电的情况下,如图3所示,则nmos的源端也会由于源漏之间漏电而被漏端带亮,使得整个电压衬度像全部显示为亮。因此可以反推在这种情况下原nmos的源漏端均为亮则其源漏之间漏电,若源漏之间不漏电,则仅有与pmos相连的漏端电压衬度像为亮。

35.第三步,继续研磨至接触孔层次,进行电压衬度像,再次进行判断。如果到接触孔层次,电压衬度像如图4所示,此时连接nmos和pmos之间的金属层被去除,nmos与pmos之间的连接解除。此时进行电压衬度,如果其电压衬度像和图1所示相同,也就是和正常情况相同,则可以确定图3中的异常是nmos源漏端之间在漏电导致的。

36.如果芯片上本来没有nmos和pmos源漏互联的则进行如下判定。

37.由于nmos和pmos器件之间没有连接,各自独立,在进行初始的如图1所示的电压衬度之后,直接研磨至接触孔层次,电压衬度vc 结果正常,寻找距离怀疑区域最近的电压衬度像发亮的接触孔层,将pmos端的源漏以及nmos的源端或者是漏端中的任一端生长金属条形成连接,如铂金属条进行人工连接如图5所示,再次进行电压衬度像,如果nmos剩余一端电压衬度显示为亮,则证明nmos的源漏端之间存在漏电,若nmos的剩余一端的电压衬度显示为暗,这表明nmos的源漏端之间不存在漏电。

38.如图6 所示,第一金属层上看到nmos的源端电压衬度像,被和pmos 源相连的漏端带亮,并且接触孔层次的电压衬度像如图7所示,推测是nmos 源漏之间有漏电,进过平面tem 验证有贯穿源漏之间的位错(如图8所示)导致其源漏漏电,证明前述的电压衬度判断准确。

39.以上仅为本发明的优选实施例,并不用于限定本发明。对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1