一种基于DDS拟合的宽频率单相功率源的制作方法

一种基于dds拟合的宽频率单相功率源

技术领域

1.本实用新型涉及一种基于dds拟合的宽频率单相功率源,属于智能电能表检测领域。

背景技术:

2.随着新一代智能电能表的功能和技术的发展,智能电能表及其检测标准都产生了相应的变化。基于新标准的智能电能表检测方法与现行检测相比提出了更高的要求。现行的gb/t 17215系列标准已经无法满足面向未来的智能电能表的技术要求。现行的标准包括gb/t 17215.211-2006《交流电测量设备通用要求、试验和试验条件第11部分测量设备》,gb/t 17215.321-2008《1级、2级静止式有功电能表特殊要求》和gb/t 17215.322-2008《0.2s级、0.5s级静止式有功电能表特殊要求》。根据《r46有功电能表国际建议》以及中国电能表新形势下的新要求,现已生成新标准送审稿:gb/t 17215.211-202x《电测量设备(交流)通用要求、试验和试验条件第11部分:测量设备》和gb/t 17215.321-202x《电测量设备(交流)特殊要求第21部分:静止式有功电能表(a级、b级、c级、d级和e级)》。新的标准增加了软件要求:结合我国电能表的技术特点和管理要求对电能表提出软件要求,并给出验证方法。增加和修改了计量和技术要求:增加尖顶波和方波试验项目,增加高次谐波试验、无负载试验(潜动试验)等,这些试验项目的增加是对智能电能表性能的提升,同时对其检测设备的要求也有所增加。

3.传统的单相功率源,一般只能输出2-22、2-32次谐波,基于spwm调制输出,通过回采调整输出的幅值和相位,确保输出的精度;对于spwm调制输出方案,其输出频率受到spwm载波频率的限制,目前一般载波的频率为几十khz,由于受到开关速率、后级lc滤波电路及环路稳定性的影响,难以提升载波频率,因此难以输出高次谐波,同时输出稳定度较差,比线性功放差一个数量级以上;同时现有的功率源的波形拟合点数少,其信号发生一般是嵌入式cpu+高速da直接发生的方式,其嵌入式cpu主频一般小于72mhz,因此一般工频每周拟合波点数不超过3600,在高频谐波的失真度较大,谐波准确度较差,谐波稳定性差。

4.现有检测设备已经不能满足对新一代智能电能表的检测要求,尤其是现有功率源的功能无法实现新检测标准中增加的试验要求。

5.因此,亟需研制适用于新一代智能电能表检测的宽频率ir46检测用单相功率源,提升单相功率源对ir46功能被检电能表的检测能力。

技术实现要素:

6.在下文中给出了关于本实用新型的简要概述,以便提供关于本实用新型的某些方面的基本理解。应当理解,这个概述并不是关于本实用新型的穷举性概述。它并不是意图确定本实用新型的关键或重要部分,也不是意图限定本实用新型的范围。其目的仅仅是以简化的形式给出某些概念,以此作为稍后论述的更详细描述的前序。

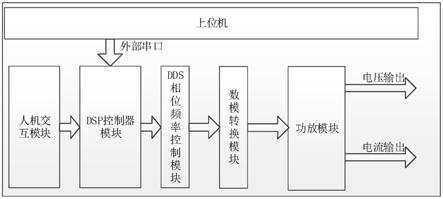

7.本实用新型提供了一种基于dds拟合的宽频率单相功率源,包括:人机交互模块、

dsp控制器模块、dds相位频率控制模块、数模转换模块和功放模块;所述人机交互模块的输出端与dsp控制器模块的输入端连接;所述dsp控制器模块的输出端与dds相位频率控制模块的输入端连接;所述dds相位频率控制模块的输出端与数模转换模块的输入端连接;所述数模模块的输出端与所述功放模块的输入端连接;所述功放模块的输出端输出电流和电压。

8.优选的,所述dsp控制器模块包括通讯模块、档位控制逻辑单元、信号发生器模块和保护单元;所述通讯模块的输入端连接人机交互模块的输出端;所述通讯模块的输出端连接所述档位控制逻辑单元输入端、dds相位频率控制模块输入端和保护单元的输入端;所述dds相位频率控制模块的输出端连接所述数模转换模块的输入端;所述信号发生器模块的输出端连接所述dds相位频率控制模块的输入端。

9.优选的,所述信号发生器模块包括通讯接口、波形拟合算法模块、波形数据缓冲区模块、dma控制器、波形dac拟合数字信号模块、幅值控制逻辑模块、幅值dac拟合数字信号模块;所述通讯接口的输出端连接所述波形拟合算法模块、幅值控制逻辑模块的输入端;所述波形拟合算法模块的输出端输出波形数据至所述波形数据缓冲区模块输入端;所述波形数据缓冲区模块的输出端连接所述dma控制器的输入端;所述dma控制器的输出端连接所述波形dac拟合数字信号模块的输入端;幅值控制逻辑模块的输出端连接所述幅值dac拟合数字信号模块的输入端;所述幅值dac拟合数字信号模块的输出端、波形dac拟合数字信号模块的输出端连接所述dds相位频率控制模块的输入端。

10.优选的,所述数模转换模块具体是双da转换模块,所述双da转换模块一路da控制信号的幅值,一路da控制信号的波形;用于将dds相位频率控制模块输出的数字信号转换成模拟信号输出至功放模块。

11.优选的,所述功放模块包括功放电路和变压器;所述功放电路的输入端连接所述dds相位频率控制模块的输出端;所述功放电路的输出端连接所述变压器的输入端。

12.本实用新型的有益效果如下:本实用新型采用dds拟合数字信号的方式,可以实现频率的高准确度、相位的高分辨率,同时结合线性功放技术,实现高频谐波的信号的低失真、高准确度、高稳定度的输出,解决现有检测设备已经不能满足对新一代智能电能表的检测要求,尤其是现有标准功率源的功能无法实现新检测标准中增加的试验要求。

附图说明

13.此处所说明的附图用来提供对本技术的进一步理解,构成本技术的一部分,本技术的示意性实施例及其说明用于解释本技术,并不构成对本技术的不当限定。在附图中:

14.图1为本实用新型实施例所述的结构示意图;

15.图2为本实用新型实施例所述的信号发生器结构示意图;

16.图3为本实用新型实施例所述的信号发生器连接结构示意图;

17.图4为本实用新型实施例所述的dds相位频率控制模块连接结构示意图;

18.图5为本实用新型实施例所述的数模转换模块连接结构示意图;

19.图6为本实用新型实施例所述的功放模块原理示意图;

20.图7为本实用新型实施例所述的功放模块保护原理示意图。

具体实施方式

21.为了使本技术实施例中的技术方案及优点更加清楚明白,以下结合附图对本技术的示例性实施例进行进一步详细的说明,显然,所描述的实施例仅是本技术的一部分实施例,而不是所有实施例的穷举。需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。

22.实施例一、参照图1-图7说明本实施例,一种基于dds拟合的宽频率单相功率源,包括:人机交互模块、dsp控制器模块、dds相位频率控制模块、数模转换模块和功放模块;所述人机交互模块的输出端与dsp控制器模块的输入端连接;所述dsp控制器模块的输出端与dds相位频率控制模块的输入端连接;所述dds相位频率控制模块的输出端与数模转换模块的输入端连接;所述数模模块的输出端与所述功放模块的输入端连接;所述功放模块的输出端输出电流和电压。

23.dsp控制器模块包括通讯模块、档位控制逻辑单元、信号发生器模块和保护单元;所述通讯模块的输入端连接人机交互模块的输出端;所述通讯模块的输出端连接所述档位控制逻辑单元输入端、dds相位频率控制模块输入端和保护单元的输入端;所述dds相位频率控制模块的输出端连接所述数模转换模块的输入端;所述信号发生器模块的输出端连接所述dds相位频率控制模块的输入端。

24.所述信号发生器模块包括通讯接口、波形拟合算法模块、波形数据缓冲区模块、dma控制器、波形dac拟合数字信号模块、幅值控制逻辑模块、幅值dac拟合数字信号模块;

25.所述通讯接口的输出端连接所述波形拟合算法模块的输入端;波形拟合算法模块接收上位机的控制信号,拟合输出正弦波、方波、直流、三角波、谐波叠加等波形数据;

26.所述幅值控制逻辑模块的输入端;控制动态信号波形的幅值输出;

27.所述波形拟合算法模块的输出端输出波形数据至所述波形数据缓冲区模块输入端;

28.所述波形数据缓冲区模块的输出端连接所述dma控制器的输入端;dma控制器从输出波形缓冲区读取数据并输出;

29.所述dma控制器的输出端连接所述波形dac拟合数字信号模块的输入端;波形dac接收dma传送的波形数据,控制输出波形的形状;

30.所述幅值控制逻辑模块的输出端连接所述幅值dac拟合数字信号模块的输入端;控制输出波形的幅值大小;

31.所述幅值dac拟合数字信号模块的输出端、波形dac拟合数字信号模块的输出端连接所述dds相位频率控制模块的输入端。

32.波形拟合算法模块控制启动缓存器,缓存器中的波形数据通过dsp控制器的sport口dma控制器传输到da数模转换模块,即完成一个周波信号的输出,通过dma控制器中断重复一个周波信号的输出获得周期连续信号。通过dma控制器传输方式可以使得每两个d/a转换值之间的延时极小,信号失真度极小,最高可达到50hz频率信号每周波5万点,如此高的精度使得在信号频率比较高的时候仍能够获得每周波较高的点数,保证了信号的稳定度、精度,使得信号失真度小。

33.档位控制逻辑单元根据用户输出的设定值和档位控制逻辑值表完成档位控制功能。档位控制逻辑值表是一个6x15的16进制二维表格,6表示系统有6相输出,15表示每相最

多可以有15个档位。输出时通过在档位配置表里面搜索当前驱动值并发送到档位控制逻辑单元完成档位控制功能。

34.档位控制逻辑值表

[0035][0036]

保护单元完成对dsp控制器的保护,主要有电压过载、电流过载以及系统过热。当保护发生时系统将停止输出并给出提示音,并通过通讯单元往上位机的人机界面发送告警信号,从而提醒用户。

[0037]

所述幅值dac拟合数字信号模块的输出端、波形dac拟合数字信号模块的输出端连接所述dds相位频率控制模块的输入端,波形dac拟合数字信号模块输出数字波形信号,通过dds相位频率控制模块完成对输出数字波形信号的相位、频率进行精准控制,所述dds相位频率控制模块和双da转换模块连接,经过dds相位频率控制模块精准调节后的数字信号经过da转换器输出对应模拟信号,完成数字信号的准确拟合到模拟信号的精确发生。

[0038]

所述数模转换模块具体是双da转换模块,所述双da转换模块一路da控制信号的幅值,一路da控制信号的波形;用于将dds相位频率控制模块输出的数字信号转换成模拟信号输出至功放模块。

[0039]

由于v/i变换功放模块输出电流的大小、精度、稳定度都和信号有着直接的关系,所以数模转换模块采用双da实现信号的输出,一路da控制信号的幅值,一路da控制信号的波形,两者结合可以集中两个da的精度,使得信号da转换的精度相比于单da提升一倍。

[0040]

dds相位频率控制模块将幅值数据和波形数据严格同步传输至幅值dac和波形dac,幅值dac的输出作为波形dac的参考,波形dac基于幅值dac输出模拟量信号。

[0041]

adc基本都是16位以下的,除了adi、ti有少量18位型号,而高精度的信号发生的关键,除了波形拟合技术以外,就是dac转换技术,因为我们最终需要使用的是模拟量信号,而dsp控制器模块输出的是数字波形数据,因此需要在数字量和模拟量之间建设一道桥梁,这个桥梁就是dac转换器,其好坏直接影响最终输出。本技术方案采用的双da信号发生技术,可通过双da级联的方式提升da的位数,最高可提升一倍,比如说16位dac,通过双da级联,可

以提供最高32位的信号解析度。

[0042]

所述功放模块包括功放电路和变压器;所述功放电路的输入端连接所述dds相位频率控制模块的输出端;所述功放电路的输出端连接所述变压器的输入端。

[0043]

功放模块采用高精度集成功放加mos管结构,并且由双电源供电,采用匹配的多对mos管对管,可以实现交流输出驱动后级变压器做大电流输出,最大电流可输出120a,电压输出可达264v,输出带宽高,谐波输出最高可到50次。

[0044]

通过变压器做功率变换级,通过电压反馈实现高压输出,通过电流反馈实现v/i变换,输出大电流,功放模块通过变压器升压来达到高压输出的目的,功放模块电路结构简单,输出负载能力强,结合双环负反馈技术,输出精度高、稳定性好,支持工频2-50次谐波叠加输出。

[0045]

选取功率放大驱动芯片lme49830,lme49830具有低噪声、极高的电源抑制比、极低的失真度和功率带宽大,具有56ma的驱动电流,最大16v的驱动电压,几乎可以驱动所有mos。lme49830集成电路可支持1kw的输出功率,1khz频率典型总谐波失真加噪声仅7ppm。

[0046]

采用精度为万分之一、温漂仅1ppm的精密电阻,提升放大器的精度和准确度。

[0047]

功放模块具备过热、过载告警功能。当功放上面的温度过高时可以通过停止信号输出,切断电流输出。正常状态下软件对输出电流值有限制,不会输出过载,但当故障发生时,可能出现输出电流过大情况,为保护功放电路,需要过载电路限制电流的大小,限流电路是通过限制mos管的驱动电压大小来实现限流的。

[0048]

功放在实际使用中由于被测负载是经常变化的,因此很容易由于误接线或负载的原因导致输出过载,电压功放的过载情况主要有:负载阻抗太小,功率超出了功放的输出能力、输出对地短路。

[0049]

这其中最严酷的是输出对地短路的情况,因为电压高冲击大,非常容易导致功放烧毁。

[0050]

电流功放的过载主要有:

[0051]

(1)被试装置的电流回路的输入阻抗过大,导致超出功放的输出能力;

[0052]

(2)输出开路。

[0053]

对于电流功放而言,这两种情况都不会对功放本身的安全造成威胁。由于电流功放的输出端口电压有限(一般只有几伏的端口电压),因此开路对使用者的人身安全也不会造成威胁。这一点不同于电流互感器,电流互感器本质是一个变压器,由于非常高的次级绕组数量(相对于初级绕组),如果开路的话将变成一个很高电压输出的升压变压器,对人身威胁较大。因此电流互感器是严禁开路的。

[0054]

功率源的电压过载保护采用限流方式,并在检测到过流后迅速停止输出,从而保护功放的安全。

[0055]

具体的,参照图7,电压过载保护由电阻r9、电阻r110和mos管t6构成限流电路,当输出过载时,流过电阻r9的电流将激增并在电阻r9上产生电压降,电压降加载在mos管t6的基极上从而引起t6管导通,随着mos管t6开通的增加mos管t6将把mos管t5基极的电压拉低,因此mos管t5上的电流将被限制。

[0056]

电阻r10的作用在于保护mos管t6,在瞬间的电压尖峰加载到mos管t6上时不至于造成损坏。

[0057]

对于电流功放来说,因为过载时大部分电压将加载在负载上,这对于输出功率管来说反而是负担最轻的情况,因此电流功放本身不怕过载。

[0058]

电流功放的过载保护对于功放本身的可靠性来说没有意义,但是对于提醒用户功放的状态有用的。电流功放过载时驱动输出将达到最大值,严重时呈现方波形式,根据这个特点一般在驱动级设置比较器来判断是否过载。

[0059]

人机交互模块,通过嵌入式屏幕实现人机交互,结构简单,稳定可靠,开机速度快,即开即用。dsp还可以通过串口连接,该接口用于和外部上位机通信,通过串口通信可以方便外部上位机直接可以控制源。

[0060]

dsp控制器模块使用双核dsp处理器,并扩展128m的ddr同步内存和和32m的异步存取flash,信号处理能力非常强大。

[0061]

本实用新型的工作原理:

[0062]

输入参数(幅值、相位及频率等)至波形拟合算法模块,实时计算信号波形的拟合数据点,存储到dsp缓存器中。

[0063]

dsp控制器模块采用adi的高速双核dsp(bf609)+ddr+大容量flash构成,通过高速dsp进行大数据量的波形数据拟合,dsp内置几百兆的sdram,拟合好的波形可以直接存储在系统的内存(sdram)中,并通过dma控制器模块控制,在cpu不干涉的情况下按照固定的速率送给dds相位频率控制模块的,通过dds相位频率控制模块的的精确调节输出至数模转换模块,本实用新型使用adi的高速高精度dac,数据传输率高达50mbit/s,通过幅值dac和波形dac级联构成双da,接收上位机设置的参数,通过波形拟合算法模块输出数字波形数据,数字波形数据信号经过dds相位频率控制模块进行相位及频率控制,通过幅值dac、波形dac还原为模拟信号,因此其数字波形数据直接决定还原出的模拟信号波形,波形拟合算法模块是信号发生器的关键。

[0064]

本实用新型可以实现在50hz时每周波高达3-5万点的波形拟合能力,因此可以输出高精度的高次谐波,且拥有极低的波形失真度。本实用新型采用了支持乘法参考输入功能的dac,因此可以支持动态的参考电压输入,从而实现双dac架构:波形dac和幅值dac。波形dac用于输出波形信号,幅值大小通过幅值dac控制,两个dac都为16位,从而在不牺牲速度的前提下提供了最高32位的信号解析度。

[0065]

尽管根据有限数量的实施例描述了本实用新型,但是受益于上面的描述,本技术领域内的技术人员明白,在由此描述的本实用新型的范围内,可以设想其它实施例。此外,应当注意,本说明书中使用的语言主要是为了可读性和教导的目的而选择的,而不是为了解释或者限定本实用新型的主题而选择的。因此,在不偏离所附权利要求书的范围和精神的情况下,对于本技术领域的普通技术人员来说许多修改和变更都是显而易见的。对于本实用新型的范围,对本实用新型所做的公开是说明性的,而非限制性的,本实用新型的范围由所附权利要求书限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1