针对触觉负载的阻抗测量的制作方法

针对触觉负载的阻抗测量

1.相关申请的交叉引用

2.本专利申请要求于2021年1月13日提交的题为“impedance measurement for a haptic load(针对触觉负载的阻抗测量)”的美国非临时专利申请no.17/148,100的优先权,该申请由此通过援引被明确纳入于此。

3.公开领域

4.本公开的各方面一般涉及触觉振动,并且例如涉及针对触觉负载的阻抗测量。

5.背景

6.用户装备(ue)(诸如智能电话、平板、以及其他移动计算设备)可使用触觉振动来与用户通信。例如,ue可使用触觉系统来产生向用户提供触觉确认、警报或其他消息的一个或多个振动模式。

7.概述

8.在一些实现中,一种测量电路包括:第一晶体管,该第一晶体管被配置成驱动触觉负载的第一节点;第二晶体管,该第二晶体管具有连接到该第一晶体管的栅极的栅极以及连接到第一参考电流的漏极;以及第一比较器,该第一比较器具有并联连接到该第二晶体管的漏极的第一节点并具有连接到该触觉负载的第一节点的第二节点,其中当驱动该触觉负载的电压满足第一条件时该第一比较器触发。

9.在一些实现中,一种测量电路包括:第一晶体管,该第一晶体管被配置成驱动触觉负载的第一节点;第二晶体管,该第二晶体管具有连接到该第一晶体管的栅极的栅极以及连接到第一参考电流的漏极;以及第一模数转换器,该第一模数转换器具有并联连接到该第二晶体管的漏极的第一节点并具有连接到该触觉负载的第一节点的第二节点,其中该第一模数转换器输出与该触觉负载的阻抗相关联的第一比率。

10.在一些实现中,一种由测量电路执行的方法包括:使用第一晶体管来驱动触觉负载的第一节点;以及当驱动该触觉负载的电压满足第一条件时触发第一比较器,其中该第一比较器具有并联连接到第二晶体管的漏极的第一节点并具有连接到该触觉负载的第一节点的第二节点,并且其中该第二晶体管具有连接到该第一晶体管的栅极的栅极并具有连接到第一参考电流的漏极。

11.在一些实现中,一种由测量电路执行的方法包括:使用第一晶体管来驱动触觉负载的第一节点;以及使用第一模数转换器来输出与该触觉负载的阻抗相关联的第一比率,其中该第一模数转换器具有并联连接到第二晶体管的漏极的第一节点并具有连接到该触觉负载的第一节点的第二节点,并且其中该第二晶体管具有连接到该第一晶体管的栅极的栅极并具有连接到第一参考电流的漏极。

12.在一些实现中,一种存储指令集的非瞬态计算机可读介质包括:在由一个或多个微处理器执行时使得该一个或多个微处理器进行以下操作的一条或多条指令:传送用以使用第一晶体管来驱动触觉负载的第一节点的指令;以及当驱动该触觉负载的电压满足第一条件时接收来自第一比较器的输出,其中该第一比较器具有并联连接到第二晶体管的漏极的第一节点并具有连接到该触觉负载的第一节点的第二节点,并且其中该第二晶体管具有

连接到该第一晶体管的栅极的栅极并具有连接到第一参考电流的漏极。

13.在一些实现中,一种存储指令集的非瞬态计算机可读介质包括:在由一个或多个微处理器执行时使得该一个或多个微处理器进行以下操作的一条或多条指令:传送用以使用第一晶体管来驱动触觉负载的第一节点的指令;以及接收使用第一模数转换器的与该触觉负载的阻抗相关联的第一比率,其中该第一模数转换器具有并联连接到第二晶体管的漏极的第一节点并具有连接到该触觉负载的第一节点的第二节点,并且其中该第二晶体管具有连接到该第一晶体管的栅极的栅极并具有连接到第一参考电流的漏极。

14.在一些实现中,一种装备包括:用于使用第一晶体管来驱动触觉负载的第一节点的装置;以及用于当驱动该触觉负载的电压满足第一条件时触发第一比较器的装置,其中该第一比较器具有并联连接到第二晶体管的漏极的第一节点并具有连接到该触觉负载的第一节点的第二节点,并且其中该第二晶体管具有连接到该第一晶体管的栅极的栅极并具有连接到第一参考电流的漏极。

15.在一些实现中,一种装备包括:用于使用第一晶体管来驱动触觉负载的第一节点的装置;以及用于使用第一模数转换器来输出与该触觉负载的阻抗相关联的第一比率的装置,其中该第一模数转换器具有并联连接到第二晶体管的漏极的第一节点并具有连接到该触觉负载的第一节点的第二节点,并且其中该第二晶体管具有连接到该第一晶体管的栅极的栅极并具有连接到第一参考电流的漏极。

16.各方面一般包括如基本上参照附图和说明书描述并且如附图和说明书所解说的方法、装备、系统、计算机程序产品、非瞬态计算机可读介质、用户设备、用户装备、无线通信设备、和/或处理系统。

17.前述内容已较宽泛地勾勒出根据本公开的示例的特征和技术优势以力图使下面的详细描述可被更好地理解。附加的特征和优势将在此后描述。所公开的概念和具体示例可容易地被用作修改或设计用于实施与本公开相同目的的其他结构的基础。此类等效构造并不背离所附权利要求书的范围。本文所公开的概念的特性在其组织和操作方法两方面以及相关联的优势将因结合附图来考虑以下描述而被更好地理解。每一附图是出于解说和描述目的来提供的,而非定义对权利要求的限定。

18.附图简述

19.为了能详细理解本公开的以上陈述的特征,可参照各方面来对以上简要概述的内容进行更具体的描述,其中一些方面在附图中解说。然而应注意,附图仅解说了本公开的某些典型方面,故不应被认为限定其范围,因为本描述可允许有其他等同有效的方面。不同附图中的相同附图标记可标识相同或相似的元素。

20.图1是解说根据本公开的各个方面的在其中可以实现本文中所描述的触觉系统的示例环境的示图。

21.图2是解说根据本公开的各个方面的在图1中所示的一个或多个设备(诸如触觉系统)的示例组件的示图。

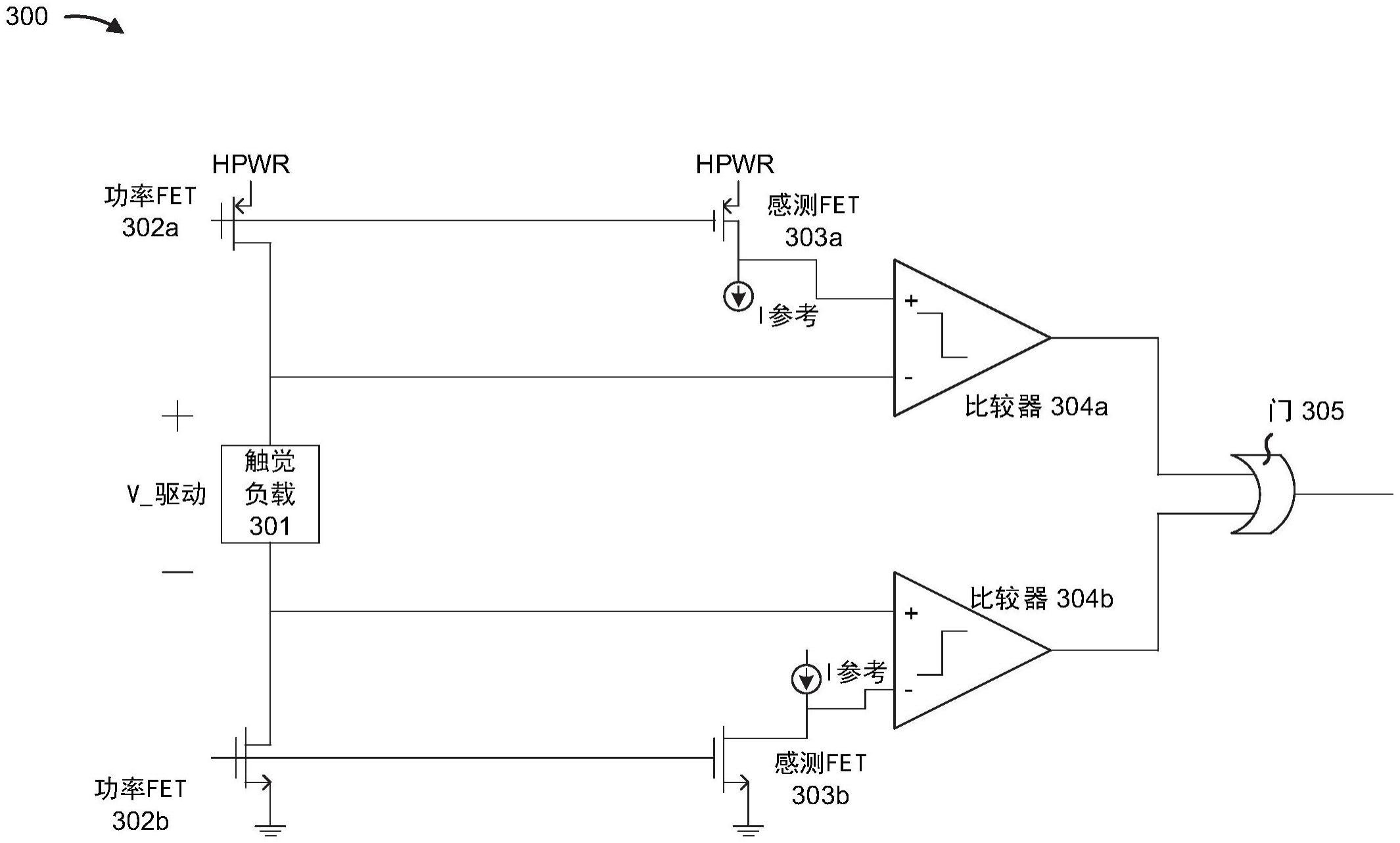

22.图3a、3b和3c是解说根据本公开的各个方面的与静态地检测触觉负载的阻抗相关联的示例的示图。

23.图4a、4b和4c是解说根据本公开的各个方面的与动态地检测触觉负载的阻抗相关联的示例的示图。

1,并且ue 120-2可进一步包括触觉系统130-2。触觉系统130-1和130-2可分别向ue 120-1和120-2的用户触觉地传达信息。在一些实现中,触觉系统130-1和/或触觉系统130-2可包括用于确定跨触觉负载的阻抗的机制,如本文中他处所描述的。

33.基站110可包括能够与ue 120-1和120-2进行通信的一个或多个设备并且还可被称为新无线电(nr)bs、b节点、gnb、5g b节点(nb)、接入点、传送接收点(trp)、或其他类似术语。附加地,基站110可包括能够经由回程从核心网140接收协调和控制信号的一个或多个设备。基站110可为特定地理区域提供通信覆盖。在由第三代伙伴项目(3gpp)颁布的标准中,术语“蜂窝小区”可以指bs的覆盖区域和/或服务该覆盖区域的bs子系统,这取决于使用该术语的上下文。在一些实现中,基站110可提供对宏蜂窝小区、微微蜂窝小区、毫微微蜂窝小区、和/或另一类型的蜂窝小区的通信覆盖。宏蜂窝小区可覆盖相对较大的地理区域(例如,半径为数千米),并且可允许由具有服务订阅的ue无约束地接入。微微蜂窝小区可覆盖相对较小的地理区域,并且可允许由具有服务订阅的ue无约束地接入。毫微微蜂窝小区可覆盖相对较小的地理区域(例如,住宅),并且可允许由与该毫微微蜂窝小区有关联的ue(例如,封闭订户群(csg)中的ue)有约束地接入。用于宏蜂窝小区的bs可被称为宏bs。用于微微蜂窝小区的bs可被称为微微bs。用于毫微微蜂窝小区的bs可被称为毫微微bs或家用bs。

34.核心网140可包括电信核心网,诸如5g下一代核心网(ng核心)、长期演进(lte)演进型分组核心(epc)和/或其他类似的电信核心网。核心网140可包括能够执行移动性功能142(例如,接入和移动性功能(amf))、策略功能144(例如,策略控制功能(pcf))、会话功能146(例如,会话管理功能(smf))、用户面功能148(例如,upf)、和/或其他类似核心网功能的一个或多个设备。移动性功能142可提供对ue(例如,ue 120-1和120-2)的认证和授权,并为那些ue提供移动性管理。策略功能144可提供纳入网络切片、漫游、分组处理、移动性管理和/或其他核心网操作的策略框架。会话功能146可提供由核心网140支持的无线电信系统中的通信会话的建立、修改和释放。例如,会话功能146可配置用户面功能148处的话务引导策略和/或实施网际协议(ip)地址分配和策略。在一些实现中,移动性功能142和会话功能146可以是非接入阶层(nas)信令(例如,来自ue 120-1和120-2)的终接点。用户面功能148可以是无线电接入技术(rat)内/间移动性的锚点。例如,用户面功能148可向分组应用规则,诸如与分组路由、话务报告和/或处置用户面qos有关的规则,并且可确定在通信会话中传达(例如,传达至ue 120-1和120-2)的因应用而异的数据的属性。

35.图1中所示的设备和网络的数目和布置是作为示例提供的。在实践中,可以存在与图1中所示的那些设备和/或网络相比附加的设备和/或网络、较少的设备和/或网络、不同的设备和/或网络、或不同地布置的设备和/或网络。此外,图1中所示的两个或更多个设备可被实现在单个设备内,或者图1中所示的单个设备可被实现为多个分布式设备。附加地或替换地,环境100的设备集(例如,一个或多个设备)可以执行被描述为由环境100的另一设备集执行的一个或多个功能。

36.图2是解说根据本公开的各个方面的设备200的示例组件的示图。设备200可对应于ue 120-1和/或ue 120-2。在一些方面,ue 120-1和/或ue 120-2可包括一个或多个设备200和/或设备200的一个或多个组件。如图2中所示,设备200可包括总线205、处理器210、存储器215、存储组件220、输入组件225、输出组件230、通信接口235、触觉系统240、和/或其他类似组件。

37.总线205包括准许设备200的各组件之间的通信的组件。处理器210在硬件、固件、或硬件与软件的组合中实现。处理器210是中央处理单元(cpu)、图形处理单元(gpu)、加速处理单元(apu)、微处理器、微控制器、数字信号处理器(dsp)、现场可编程门阵列(fpga)、专用集成电路(asic)或另一类型的处理组件。在一些方面,处理器210包括一个或多个能够被编程以执行功能的处理器。存储器215包括存储供处理器210使用的信息和/或指令的随机存取存储器(ram)、只读存储器(rom)和/或另一类型的动态或静态存储设备(例如,闪存、磁存储器和/或光存储器)。

38.存储组件220存储与设备200的操作和使用有关的信息和/或软件。例如,存储组件220可包括硬盘(例如,固态硬盘)、闪存、随机存取存储器(ram)和/或另一类型的非瞬态计算机可读介质、以及对应的驱动器。

39.输入组件225包括准许设备200接收信息(诸如经由用户输入)的组件(例如,触摸屏显示器、键盘、按键板、鼠标、按钮、开关、和/或话筒)。附加地或替换地,输入组件225可以包括用于确定设备200的定位或位置的组件(例如,全球定位系统(gps)组件、全球导航卫星系统(gnss)组件等)、用于感测信息的传感器(例如,加速度计、陀螺仪、致动器、另一类型的定位或环境传感器等)。输出组件230包括提供来自设备200的输出信息的组件(例如,显示器、扬声器、触觉反馈组件、音频或视觉指示器等)。

40.通信接口235包括类收发机组件(例如,收发机和/或单独的接收机和发射机),其使得设备200能够与其他设备进行通信(诸如经由有线连接、无线连接、或有线连接和无线连接的组合)。通信接口235可以准许设备200接收来自另一设备的信息和/或向另一设备提供信息。例如,通信接口235可包括以太网接口、光接口、同轴接口、红外接口、射频接口、通用串行总线(usb)接口、无线局域接口(例如,wi-fi接口)、蜂窝网络接口等。

41.触觉系统240可对应于触觉系统130-1和/或触觉系统130-2。在一些方面,触觉系统130-1和/或触觉系统130-2可包括一个或多个触觉系统240和/或触觉系统240的一个或多个组件。触觉系统240可包括模式源245,该模式源245生成对指示要传达给用户的振动模式的数据进行编码的模拟和/或数字信号。附加地,触觉系统240可包括参考时钟250,诸如石英压电振荡器、储能电路和/或被配置成生成时钟信号的另一电路。相应地,数字控制器255可生成对用于根据振动模式来驱动触觉块(m)的指令进行编码的模拟和/或数字信号。驱动器260可生成用于驱动lra 265的触觉块m或其他类似触觉引擎的一个或多个电压。在一些实现中,触觉系统240可进一步包括用于确定跨触觉负载(例如,触觉块m)的阻抗的机制270,如本文中他处所描述的。

42.设备200可以执行本文所描述的一个或多个过程。设备200可以基于处理器210执行由非瞬态计算机可读介质(诸如存储器215和/或存储组件220)存储的软件指令来执行这些过程。计算机可读介质在本文中被定义为非瞬态存储器设备。存储器设备包括单个物理存储设备内的存储器空间或跨多个物理存储设备分布的存储器空间。

43.可以经由通信接口235将软件指令从另一计算机可读介质或另一设备读取到存储器215和/或存储组件220中。存储器215和/或存储组件220中所存储的软件指令在被执行时可以使处理器210执行本文所描述的一个或多个过程。附加地或替换地,可使用硬连线电路系统代替软件指令或与软件指令相结合来执行本文所描述的一个或多个过程。由此,本文所描述的各方面不限于硬件电路系统和软件的任何特定组合。

44.在一些方面,设备200包括用于执行本文所描述的一个或多个过程的装置和/或用于执行本文所描述的过程的一个或多个操作的装置。例如,设备200可包括:用于驱动触觉负载的第一节点的装置;和/或用于当驱动触觉负载的电压满足第一条件时触发第一比较器的装置。在一些方面,此类装置可包括结合图2所描述的设备200的一个或多个组件,诸如总线205、处理器210、存储器215、存储组件220、输入组件225、输出组件230、通信接口235、触觉系统240、和/或其他类似组件。附加地或替换地,设备200可包括:用于驱动触觉负载的第一节点的装置;和/或用于使用第一模数转换器来输出与触觉负载的阻抗相关联的第一比率的装置。在一些方面,此类装置可包括结合图2所描述的设备200的一个或多个组件,诸如总线205、处理器210、存储器215、存储组件220、输入组件225、输出组件230、通信接口235、触觉系统240、和/或其他类似组件。

45.图2中所示的组件的数目和布置是作为示例提供的。在实践中,设备200可包括与图2中所示的那些组件相比附加的组件、较少的组件、不同的组件、或不同地布置的组件。附加地或替换地,设备200的组件集合(例如,一个或多个组件)可以执行被描述为由设备200的另一组件集合执行的一个或多个功能。

46.图3a是解说根据本公开的各个方面的与静态地检测触觉负载的阻抗相关联的示例测量电路300的示图。如图3a中所示,示例300包括由电压v_drive(v_驱动)驱动的触觉负载301(例如,如结合图2所描述的触觉块m)。相应地,触觉负载301与将跨其施加v_drive的第一节点(如图3a中所示的“+”节点)和第二节点(如图3a中所示的

“‑”

节点)相关联。在一些实现中,触觉负载可包括lra,如上面结合图2所描述的。

47.在示例300中,至少一个第一晶体管302a可被配置成驱动触觉负载301的第一节点。相应地,至少一个第一晶体管302a的漏极可连接到触觉负载301的第一节点。在一些实现中,至少一个第一晶体管302a可包括功率场效应晶体管(fet)。如图3a中所示,至少一个第一晶体管302a的源极可连接到电源(例如,保持电源(hpwr)电压和/或另一电压)。附加地,示例300包括至少一个第二晶体管303a,该至少一个第二晶体管303a具有连接到至少一个第一晶体管302a的栅极的栅极以及连接到第一参考电流(图3a中示为“iref(i参考)”)的漏极。在一些实现中,至少一个第二晶体管303a可包括感测场效应晶体管(fet)。例如,感测fet可将负载电流(例如,通过至少一个第一晶体管302a的电流)镜像到感测电流(例如,通过至少一个第二晶体管303a的电流)以供测量。如图3a中所示,至少一个第二晶体管303a的源极可连接到电源(例如,hpwr电压和/或另一电压)。至少一个第二晶体管303a可连接到与至少一个第一晶体管302a相同的电源或者可连接到不同的电源。

48.示例300进一步包括第一比较器304a,该第一比较器304a具有并联连接到至少一个第二晶体管303a的漏极的第一节点以及连接到触觉负载301的第一节点的第二节点。第一比较器304a可被配置成当驱动触觉负载301的电压满足第一条件时触发。例如,当驱动触觉负载301的电压大于或等于与触觉负载301相关联的阻抗、第一参考电流、以及与至少一个第一晶体管302a和至少一个第二晶体管303a相关联的感测比率的乘积时,第一比较器304a可输出信号。例如,感测比率可至少部分地基于通过至少一个第一晶体管302a的电路与通过至少一个第二晶体管303a的电流之间的比率。在一些实现中,感测比率可以在1000:1的量级上。

49.如图3a中进一步所示,示例300可包括至少一个第三晶体管302b,其被配置成驱动

触觉负载301的第二节点。相应地,至少一个第三晶体管302b的漏极可连接到触觉负载301的第二节点。在一些实现中,至少一个第三晶体管302b可包括功率fet。如图3a中所示,至少一个第三晶体管302b的源极可连接到接地。附加地,示例300可包括至少一个第四晶体管303b,该至少一个第四晶体管303b具有连接到至少一个第三晶体管302b的栅极的栅极以及连接到第二参考电流(如图3a中示为“iref”)的漏极。第二参考电流可等于第一参考电流或者可以不同。在一些实现中,至少一个第四晶体管303b可包括感测fet。如图3a中所示,至少一个第四晶体管303b的源极可连接到接地。至少一个第四晶体管303a可连接到与至少一个第二晶体管303a相同的接地或者可连接到不同的接地。

50.示例300可进一步包括第二比较器304b,该第二比较器304b具有并联连接到至少一个第四晶体管303b的漏极的第一节点以及连接到触觉负载301的第二节点的第二节点。第二比较器304b可被配置成当驱动触觉负载301的电压满足第二条件时触发。例如,当驱动触觉负载301的电压大于或等于与触觉负载301相关联的阻抗、第二参考电流、以及与至少一个第三晶体管302b和至少一个第四晶体管303b相关联的感测比率的乘积时,第二比较器304b可输出信号。例如,感测比率可至少部分地基于通过至少一个第三晶体管302b的电流与通过至少一个第四晶体管303b的电流之间的比率。在一些实现中,感测比率可以在1000:1的量级上。

51.在一些实现中,如图3a中所示,示例300可包括连接到第一比较器304a和第二比较器304b的门305。门305可被配置成将来自第一比较器304a的输出与来自第二比较器304b的输出进行组合。例如,门305可包括or(或)门,以使得来自示例300的输出指示第一比较器304a和/或第二比较器304b是否被触发。作为替换,门305可包括and(与)门,以使得来自示例300的输出指示第一比较器304a和第二比较器304b是否被触发。

52.在一些实现中,示例300可进一步包括微处理器,其被配置(例如,编程和/或以其他方式配置)成:至少部分地基于驱动触觉负载301的电压、来自第一比较器304a的输出、第一参考电流、以及与至少一个第二晶体管303a相关联的感测比率来确定与触觉负载301相关联的阻抗。例如,当第一比较器304a触发(例如,至少部分地基于来自门305的输出来确定)时,微处理器可将阻抗计算为小于或等于以下形式的表达式:

[0053][0054]

其中v_drive表示驱动触觉负载301的电压,iref(i参考)表示第一参考电流、并且n表示与至少一个第二晶体管303a相关联的感测比率。

[0055]

附加地或替换地,微处理器可被配置(例如,编程和/或以其他方式配置)成:至少部分地基于驱动触觉负载301的电压、来自第二比较器304b的输出、第二参考电流、以及与至少一个第四晶体管303b相关联的感测比率来确定与触觉负载301相关联的阻抗。例如,当第二比较器306b触发(例如,至少部分地基于来自门305的输出来确定)时,微处理器可将阻抗计算为小于或等于以下形式的表达式:

[0056][0057]

其中v_drive表示驱动触觉负载301的电压,iref表示第二参考电流,并且n表示与

至少一个第四晶体管303b相关联的感测比率。

[0058]

在一些实现中,微处理器可进一步比较来自第一比较器304a和第二比较器304b的输出,并至少部分地基于该比较来确定第一比较器304a或第二比较器304b是否有缺陷。例如,当来自第一比较器304a的输出不对应于来自第二比较器304b的输出(例如,比来自第二比较器304b的输出更频繁或更不频繁)时,微处理器可确定第一比较器304a有缺陷。类似地,当来自第二比较器304b的输出不对应于来自第一比较器304a的输出(例如,比来自第一比较器304a的输出更频繁或更不频繁)时,微处理器可确定第二比较器304b有缺陷。

[0059]

在一些实现中,微处理器可将与触觉负载301相关联的阻抗与至少一个阈值进行比较。例如,该至少一个阈值可包括与短路相关联的一个阈值(例如,2ω)以及与开路相关联的另一阈值(例如,40ω)。当阻抗满足该至少一个阈值时,微处理器可生成误差信号。例如,微处理器可输出指示短路、开路和/或另一问题的信号。

[0060]

为了确定第一比较器304a和/或第二比较器304b在不同的驱动电压下是否触发,微处理器可被配置成扫掠驱动触觉负载301的多个电压。例如,微处理器可生成一个或多个控制信号,该一个或多个控制信号使得与触觉负载301相关联的控制器和/或驱动器(例如,图2的控制器255和/或驱动器260)生成不同的驱动电压(图3a中示为v_drive)。相应地,微处理器可至少部分地基于使用该多个电压的二分搜索来确定与触觉负载301相关联的阻抗。例如,微处理器可检测到第一比较器304a和/或第二比较器304b在50%占空比下触发以使得阻抗小于或等于20ω,随后检测到第一比较器304a和/或第二比较器304b在25%占空比下触发以使得阻抗小于或等于10ω,随后检测到第一比较器304a和/或第二比较器304b在12.5%占空比下没有触发以使得阻抗大于或等于5ω,并且随后检测到第一比较器304a和/或第二比较器304b在18.75%占空比下没有触发以使得阻抗大于或等于7.5ω。在另一示例中,微处理器可进一步检测到第一比较器304a和/或第二比较器304b在21.875%占空比下没有触发以使得阻抗大于或等于8.75ω。相应地,微处理器可使用二分搜索来标识与触觉负载301相关联的阻抗范围。

[0061]

附加地或替换地,微处理器可被配置成扫掠至少一个第二晶体管303a的多个第一参考电流和/或至少一个第四晶体管303b的多个第二参考电流。例如,微处理器可生成一个或多个控制信号,该一个或多个控制信号使得与至少一个第二晶体管303a相关联的电流源和/或与至少一个第四晶体管303b相关联的电流源分别生成不同的第一参考电流和/或第二参考电流(图3a中示为iref)。相应地,微处理器可至少部分地基于使用多个参考电流的二分搜索来确定与触觉负载301相关联的阻抗。因此,类似于上面结合v_drive所描述的二分搜索,微处理器可使用对参考电流的二分搜索来标识与触觉负载301相关联的阻抗范围。

[0062]

附加地或替换地,微处理器可被配置成扫掠与至少一个第二晶体管303a相关联的多个感测比率和/或与至少一个第四晶体管303b相关联的多个感测比率。例如,微控制器可生成一个或多个控制信号,该一个或多个控制信号使得至少一个第二晶体管303a和/或至少一个第四晶体管303b分别相对于至少一个第一晶体管302a和/或至少一个第三晶体管302b生成不同的镜像电流以及由此不同的感测比率。相应地,微处理器可至少部分地基于使用多个感测比率的二分搜索来确定与触觉负载301相关联的阻抗。因此,类似于上面结合v_drive所描述的二分搜索,微处理器可使用对感测比率的二分搜索来标识与触觉负载301相关联的阻抗范围。

[0063]

作为替换,在一些实现中,微处理器可被配置成使用电压波形来驱动触觉负载301。例如,微处理器可生成一个或多个控制信号,该一个或多个控制信号使得与触觉负载301相关联的控制器和/或驱动器(例如,图2的控制器255和/或驱动器260)生成电压波形。在一些实现中,电压波形可包括正弦波或三角波。相应地,微处理器可至少部分地基于触发点来确定与触觉负载301相关联的阻抗,该触发点与电压波形相关联并且是至少部分地基于第一比较器304a和/或第二比较器304b的输出来确定的。例如,第一比较器304a和/或第二比较器304b可首先在v_drive的值对应于与触觉负载301相关联的阻抗时在电压波形的上升部分期间输出信号。相应地,微处理器可将第一比较器304a和/或第二比较器304b的输出映射到电压波形在该时间的值,以使得微处理器可以在没有二分搜索的情况下确定阻抗(如上所述)。在一些实现中,电压波形可具有大约200hz的频率(例如,在200hz的10%以内),以使得第一比较器304a和/或第二比较器304b可能较慢,同时仍然提供用于确定与触觉负载301相关联的阻抗的准确输出。

[0064]

结合图3a所描述的机制可以以比现有机制显著更小的功耗和电路系统面积来测量与触觉负载301相关联的阻抗。附加地,结合图3a所描述的机制可比现有机制更准确也更不易出现校准误差。

[0065]

如上所指示的,图3a是作为示例来提供的。其他示例可以不同于关于图3a所描述的示例。

[0066]

图3b是解说根据本公开的各个方面的与静态地检测触觉负载的阻抗相关联的另一示例测量电路300

′

的示图。示例300

′

类似于示例300并且包括触觉负载301(例如,如结合图2所描述的触觉块m),该触觉负载301由电压v_drive驱动并与第一节点(图3b中示为“+”节点)和第二节点(图3b中示为

“‑”

节点)相关联。在一些实现中,触觉负载可包括lra,如上面结合图2所描述的。

[0067]

示例300

′

还包括至少一个第一晶体管302a、至少一个第二晶体管303a、以及第一比较器304a,如上面结合图3a所描述的。示例300

′

进一步包括驱动触觉负载301的第二节点的至少一个第三晶体管302b,但不包括连接到至少一个第三晶体管302b的至少一个第四晶体管(例如,另一感测fet)。相应地,示例300

′

不包括门,并且取而代之地,微处理器可直接使用第一比较器304a的输出。例如,微处理器可使用二分搜索和/或电压波形(例如,如上面结合图3a所描述的)来确定与触觉块301相关联的阻抗(或阻抗范围)。然而,微处理器将使用来自第一比较器304a而不是来自门的输出。

[0068]

结合图3b所描述的机制可以以比现有机制显著更小的功耗和电路系统面积来测量与触觉负载301相关联的阻抗。附加地,结合图3b所描述的机制可使用比结合图3a所描述的机制更小的电路系统面积。

[0069]

如上所指示的,图3b是作为示例来提供的。其他示例可以不同于关于图3b所描述的示例。

[0070]

图3c是解说根据本公开的各个方面的与静态地检测触觉负载的阻抗相关联的另一示例测量电路300

″

的示图。示例300

′

类似于示例300并且包括触觉负载301(例如,如结合图2所描述的触觉块m),该触觉负载301由电压v_drive驱动并与第一节点(图3c中示为“+”节点)和第二节点(图3c中示为

“‑”

节点)相关联。在一些实现中,触觉负载可包括lra,如上面结合图2所描述的。

[0071]

示例300

″

还包括至少一个第三晶体管302b、至少一个第四晶体管303b、以及第二比较器304b,如上面结合图3a所描述的。示例300

″

进一步包括驱动触觉负载301的第一节点的至少一个第一晶体管302a,但不包括连接到至少一个第一晶体管302a的至少一个第二晶体管(例如,另一感测fet)。相应地,示例300

″

不包括门,并且取而代之地,微处理器可直接使用第二比较器304b的输出。例如,微处理器可使用二分搜索和/或电压波形(例如,如上面结合图3a所描述的)来确定与触觉块301相关联的阻抗(或阻抗范围)。然而,微处理器将使用来自第二比较器304b而不是来自门的输出。

[0072]

结合图3c所描述的机制可以以比现有机制显著更小的功耗和电路系统面积来测量与触觉负载301相关联的阻抗。附加地,结合图3c所描述的机制可使用比结合图3a所描述的机制更小的电路系统面积。

[0073]

如上所指示的,图3c是作为示例来提供的。其他示例可以不同于关于图3c所描述的示例。

[0074]

图4a是解说根据本公开的各个方面的与动态地检测触觉负载的阻抗相关联的示例测量电路400的示图。如图4a中所示,示例400包括由电压v_drive驱动的触觉负载301(例如,如结合图2所描述的触觉块m)。相应地,触觉负载401与跨其将施加v_drive的第一节点(图4a中示为“+”节点)和第二节点(图4a中示为

“‑”

节点)相关联。在一些实现中,触觉负载可包括lra,如上面结合图2所描述的。

[0075]

在示例400中,至少一个第一晶体管402a可被配置成驱动触觉负载401的第一节点。相应地,至少一个第一晶体管402a的漏极可连接到触觉负载401的第一节点。在一些实现中,至少一个第一晶体管402a可包括功率fet。如图4a中所示,至少一个第一晶体管402a的源极可连接到电源(例如,hpwr电压和/或另一电压)。附加地,示例400包括至少一个第二晶体管403a,该至少一个第二晶体管403a具有连接到至少一个第一晶体管402a的栅极的栅极以及连接到第一参考电流(图4a中示为“iref”)的漏极。在一些实现中,至少一个第二晶体管403b可包括感测fet。如图4a中所示,至少一个第二晶体管403a的源极可连接到电源(例如,hpwr电压和/或另一电压)。至少一个第二晶体管403a可连接到与至少一个第一晶体管402a相同的电源或者可连接到不同的电源。

[0076]

示例400进一步包括第一模数转换器(adc)404a,该第一adc 404a具有并联连接到至少一个第二晶体管403a的漏极的第一节点以及连接到触觉负载401的第一节点的第二节点。第一adc 404a可被配置成输出与触觉负载401的阻抗相关联的第一比率。例如,adc 404a可输出以下形式的信号:

[0077][0078]

其中afc_ratio(adc_比率)表示第一比率,i

lra

表示通过触觉负载401的电流,iref表示第一参考电流,n表示与至少一个第二晶体管403a相关联的感测比率(例如,类似于如上面结合图3a所描述的与至少一个第二晶体管303a相关联的感测比率),v_signal(v_信号)表示与去往如图4a中所示的第一adc 404a的第一输入相关联的电压幅度,并且v_full_(v_满量程)表示与去往如图4a中所示的第一adc 404a的第二输入相关联的电压幅度。

[0079]

如图4a中进一步所示,示例400可包括被配置成驱动触觉负载401的第二节点的至少一个第三晶体管402b。相应地,至少一个第三晶体管402b的漏极可连接到触觉负载401的

第二节点。在一些实现中,至少一个第三晶体管402b可包括功率fet。如图4a中所示,至少一个第三晶体管402b的源极可连接到接地。附加地,示例400可包括至少一个第四晶体管403b,该至少一个第四晶体管403b具有连接到至少一个第三晶体管402b的栅极的栅极以及连接到第二参考电流(图4a中示为“iref”)的漏极。第二参考电流可等于第一参考电流或者可以不同。在一些实现中,至少一个第四晶体管403b可包括感测fet。如图4a中所示,至少一个第四晶体管403b的源极可连接到接地。至少一个第四晶体管403b可连接到与至少一个第二晶体管403a相同的接地或者可连接到不同的接地。

[0080]

示例400可进一步包括第二adc 404b,该第二adc 404b具有并联连接到至少一个第四晶体管403b的漏极的第一节点以及连接到触觉负载401的第二节点的第二节点。第二adc 404b可被配置成输出与触觉负载401的阻抗相关联的第二比率。例如,adc 404b可输出以下形式的信号:

[0081][0082]

其中adc_ratio表示第二比率,i

lra

表示通过触觉负载401的电流,iref表示第二参考电流,n表示与至少一个第四晶体管403b相关联的感测比率(例如,类似于如上面结合图3a所描述的与至少一个第四晶体管303b相关联的感测比率),v_signal表示与去往如图4a中所示的第二adc 404b的第一输入相关联的电压幅度,并且v_full_scale表示与去往如图4a中所示的第二adc 404b的第二输入相关联的电压幅度。与至少一个第四晶体管403b相关联的感测比率可以同与至少一个第二晶体管403a相关联的感测比率相同或不同,并且第二参考电流可等于或不等于第一参考电流。然而,一般而言,与去往第二adc 404b的第二输入相关联的电压幅度将同与去往第一adc 404a的第二输入相关联的电压幅度相同。

[0083]

在一些实现中,示例400可进一步包括微处理器,该微处理器被配置(例如,编程和/或以其他方式配置)成:至少部分地基于驱动触觉负载401的电压(图4a中示为v_drive)、第一比率、第一参考电流、以及与至少一个第二晶体管403a相关联的感测比率来确定触觉负载401的阻抗。例如,感测比率可至少部分地基于通过至少一个第一晶体管402a的电流与通过至少一个第二晶体管403a的电流之间的比率。在一些实现中,感测比率可以在1000:1的量级上。微处理器可至少部分地基于以下形式的表达式来计算阻抗:

[0084][0085]

其中v_drive表示驱动触觉负载401的电压,iref表示第一参考电流,n表示与至少一个第二晶体管403a相关联的感测比率,并且adc_ratio表示第一比率。

[0086]

附加地或替换地,微处理器可被配置(例如,编程和/或以其他方式配置)成:至少部分地基于驱动触觉负载401的电压(图4a中示为v_drive)、第二比率、第二参考电流、以及与至少一个第四晶体管403b相关联的感测比率来确定触觉负载401的阻抗。例如,感测比率可至少部分地基于通过至少一个第三晶体管402b的电流与通过至少一个第四晶体管403b的电流之间的比率。在一些实现中,感测比率可以在1000:1的量级上。微处理器可至少部分地基于以下形式的表达式来计算阻抗:

[0087][0088]

其中v_drive表示驱动触觉负载401的电压,iref表示第二参考电流,n表示与至少一个第四晶体管403b相关联的感测比率,并且adc_ratio表示第二比率。

[0089]

在一些实现中,微处理器可进一步比较来自第一adc 404a和第二adc 404b的输出,并至少部分地基于该比较来确定第一adc 404a或第二adc 404b是否有缺陷。例如,当来自第一adc 404a的输出不对应于来自第二adc 404b的输出(例如,与来自第二adc 404b的输出相差大于或小于阈值量)时,微处理器可确定第一adc 404a有缺陷。类似地,当来自第二adc 404b的输出不对应于来自第一adc 404a的输出(例如,与来自第一adc 404a的输出相差大于或小于阈值量)时,微处理器可确定第二adc 404b有缺陷。

[0090]

在一些实现中,微处理器可将触觉负载401的阻抗与至少一个阈值进行比较。例如,该至少一个阈值可包括与短路相关联的一个阈值(例如,2ω)以及与开路相关联的另一阈值(例如,40ω)。当阻抗满足该至少一个阈值时,微处理器可生成误差信号。例如,微处理器可输出指示短路、开路和/或另一问题的信号。

[0091]

结合图4a所描述的机制可以以与现有机制相比显著更小的功耗和电路系统面积来测量与触觉负载301相关联的阻抗。附加地,结合图4a所描述的机制可以比结合图3a-3c所描述的机制更快且更准确,但同时使用更多电路系统面积。

[0092]

如上所指示的,图4a是作为示例来提供的。其他示例可以不同于关于图4a所描述的示例。

[0093]

图4b是解说根据本公开的各个方面的与动态地检测触觉负载的阻抗相关联的另一示例测量电路400

′

的示图。示例400

′

类似于示例400并且包括触觉负载401(例如,如结合图2所描述的触觉块m),该触觉负载401由电压v_drive驱动并与第一节点(图4b中示为“+”节点)和第二节点(图4b中示为

“‑”

节点)相关联。在一些实现中,触觉负载可包括lra,如上面结合图2所描述的。

[0094]

示例400

′

还包括至少一个第一晶体管402a、至少一个第二晶体管403a、以及第一adc 404a,如上面结合图4a所描述的。示例400

′

进一步包括驱动触觉负载401的第二节点的至少一个第三晶体管402b,但不包括连接到至少一个第三晶体管402b的至少一个第四晶体管(例如,另一感测fet)。相应地,示例400

′

不包括第二adc 404b,并且取而代之地,微处理器可仅接收由第一adc 404a输出的第一比率。例如,微处理器可使用第一比率来确定触觉块401的阻抗,如上面结合图4a所描述的。

[0095]

结合图4b所描述的机制可以以与现有机制相比显著更小的功耗和电路系统面积来测量与触觉负载401相关联的阻抗。附加地,结合图4b所描述的机制可使用比结合图4a所描述的机制更小的电路系统面积。

[0096]

如上所指示的,图4b是作为示例来提供的。其他示例可以不同于关于图4b所描述的示例。

[0097]

图4b是解说根据本公开的各个方面的与动态地检测触觉负载的阻抗相关联的另一示例测量电路400

″

的示图。示例400

″

类似于示例400并且包括触觉负载401(例如,如结合图2所描述的触觉块m),该触觉负载401由电压v_drive驱动并与第一节点(图4c中示为“+”节点)和第二节点(图4c中示为

“‑”

节点)相关联。在一些实现中,触觉负载可包括lra,如上

面结合图2所描述的。

[0098]

示例400

″

还包括至少一个第三晶体管402b、至少一个第四晶体管403b、以及第二adc 404b,如上面结合图4a所描述的。示例400

″

进一步包括驱动触觉负载401的第一节点的至少一个第一晶体管402a,但不包括连接到至少一个第一晶体管402a的至少一个第二晶体管(例如,另一感测fet)。相应地,示例400

″

不包括第一adc 404a,并且取而代之地,微处理器可仅接收由第二adc 404b输出的第二比率。例如,微处理器可使用第二比率来确定触觉块401的阻抗,如上面结合图4a所描述的。

[0099]

结合图4c所描述的机制可以以与现有机制相比显著更小的功耗和电路系统面积来测量与触觉负载401相关联的阻抗。附加地,结合图4c所描述的机制可使用比结合图4a所描述的机制更小的电路系统面积。

[0100]

如上所指示的,图4c是作为示例来提供的。其他示例可不同于关于图4c所描述的示例。

[0101]

图5是与针对触觉负载的阻抗测量相关联的示例过程500的流程图。在一些实现中,图5的一个或多个过程框可由测量电路(例如,测量电路300、测量电路300

′

和/或测量电路300

″

)来执行。在一些实现中,图5的一个或多个过程框可以由另一设备或者与测量电路(诸如触觉系统(例如,触觉系统240))分开或包括测量电路的设备群来执行。附加地或替换地,图5的一个或多个过程框可由设备200的一个或多个组件(诸如处理器210、存储器215、存储组件220、输入组件225、输出组件230、和/或通信接口235)来执行。

[0102]

如图5中所示,过程500可包括:使用第一晶体管来驱动触觉负载的第一节点(框510)。例如,测量电路可(例如,使用至少一个第一晶体管302a)驱动触觉负载的第一节点,如上所述。

[0103]

如图5中进一步所示,过程500可包括:当驱动触觉负载的电压满足第一条件时触发第一比较器(框520)。例如,测量电路可在驱动触觉负载的电压满足第一条件时(例如,使用第一比较器304a)触发,如上所述。在一些实现中,第一比较器可具有并联连接到第二晶体管(例如,至少一个第二晶体管303a)的漏极的第一节点并且可具有连接到触觉负载的第一节点的第二节点。附加地,第二晶体管可具有连接到第一晶体管的栅极的栅极并且可具有连接到第一参考电流的漏极。

[0104]

如图5中进一步所示,过程500可包括:使用微处理器至少部分地基于驱动触觉负载的电压、来自第一比较器的输出、第一参考电流、以及与第二晶体管相关联的感测比率来确定与触觉负载相关联的阻抗(框530)。例如,测量电路可(例如,使用微处理器)确定与触觉负载相关联的阻抗,如上所述。

[0105]

过程500可包括附加实现,诸如下文和/或结合在本文中他处所描述的一个或多个其他过程所描述的任何单个实现或各实现的任何组合。

[0106]

在第一实现中,触觉负载包括lra。

[0107]

在第二实现中,单独地或与第一实现结合地,过程500进一步包括:(例如,使用至少一个第三晶体管302b)驱动触觉负载的第二节点,并且当驱动触觉负载的电压满足第二条件时(例如,使用第二比较器304b)触发。第二比较器可具有并联连接到第四晶体管(例如,至少一个第四晶体管303b)的漏极的第一节点并且可具有连接到触觉负载的第二节点的第二节点。附加地,第四晶体管可具有连接到第三晶体管的栅极的栅极并且可具有连接

到第二参考电流的漏极。

[0108]

在第三实现中,单独地或与第一和第二实现中的一者或多者结合地,过程500进一步包括:(例如,使用门305)将来自第一比较器的输出与来自第二比较器的输出进行组合。门可连接到第一比较器和第二比较器。

[0109]

在第四实现中,单独地或与第一到第三实现中的一者或多者结合地,过程500进一步包括:(例如,使用微处理器)将与触觉负载相关联的阻抗与阈值进行比较,并且当阻抗满足该阈值时(例如,使用微处理器)生成误差信号。

[0110]

在第五实现中,单独地或与第一到第四实现中的一者或多者结合地,过程500进一步包括:(例如,使用微处理器)扫掠驱动触觉负载的多个电压,并(例如,使用微处理器)至少部分地基于使用该多个电压的二分搜索来确定与触觉负载相关联的阻抗。

[0111]

在第六实现中,单独地或与第一、第五、第六实现中的一者或多者结合地,过程500进一步包括:(例如,使用微处理器)扫掠第二晶体管的多个参考电流,并(例如,使用微处理器)至少部分地基于使用该多个参考电流的二分搜索来确定与触觉负载相关联的阻抗。

[0112]

在第七实现中,单独地或与第一到第六实现中的一者或多者结合地,过程500进一步包括:(例如,使用微处理器)扫掠与第二晶体管相关联的多个感测比率,并(例如,使用微处理器)至少部分地基于使用该多个感测比率的二分搜索来确定与触觉负载相关联的阻抗。

[0113]

在第八实现中,单独地或与第一到第七实现中的一者或多者结合地,第一晶体管的源极和第二晶体管的源极连接到电源。

[0114]

在第九实现中,单独地或与第一到第八实现中的一者或多者结合地,第一晶体管的源极和第二晶体管的源极连接到接地。

[0115]

在第十实现中,单独地或与第一到第九实现中的一者或多者结合地,过程500进一步包括:(例如,使用微处理器)使用电压波形来驱动触觉负载,并(例如,使用微处理器)至少部分地基于触发点来确定与触觉负载相关联的阻抗,该触发点与电压波形相关联并且是至少部分地基于第一比较器的输出来确定的。

[0116]

在第十一实现中,单独地或与第一到第十实现中的一者或多者结合地,电压波形包括正弦波或三角波。

[0117]

尽管图5示出了过程500的示例框,但在一些实现中,过程500可包括与图5中所描绘的框相比附加的框、较少的框、不同的框或不同地布置的框。附加地或替换地,过程500的两个或更多个框可以并行执行。

[0118]

图6是与针对触觉负载的阻抗测量相关联的示例过程600的流程图。在一些实现中,图6的一个或多个过程框可由测量电路(例如,测量电路400、测量电路400

′

和/或测量电路400

″

)来执行。在一些实现中,图6的一个或多个过程框可以由另一设备或者与测量电路(诸如触觉系统(例如,触觉系统240))分开或包括测量电路的设备群来执行。附加地或替换地,图6的一个或多个过程框可由设备200的一个或多个组件(诸如处理器210、存储器215、存储组件220、输入组件225、输出组件230、和/或通信接口235)来执行。

[0119]

如图6中所示,过程600可包括:使用第一晶体管来驱动触觉负载的第一节点(框610)。例如,测量电路可(例如,使用至少一个第一晶体管402a)驱动触觉负载的第一节点,如上所述。

[0120]

如图6中进一步所示,过程600可包括:使用第一adc来输出与触觉负载的阻抗相关联的第一比率(框620)。例如,测量电路可(例如,使用第一adc 404a)输出与触觉负载的阻抗相关联的第一比率,如上所述。在一些实现中,第一adc可具有并联连接到第二晶体管(例如,至少一个第二晶体管403a)的漏极的第一节点并且可具有连接到触觉负载的第一节点的第二节点。附加地,第二晶体管可具有连接到第一晶体管的栅极的栅极并且可具有连接到第一参考电流的漏极。

[0121]

如图6中进一步所示,过程600可包括:使用微处理器至少部分地基于驱动触觉负载的电压、第一比率、第一参考电流、以及与第二晶体管相关联的感测比率来确定触觉负载的阻抗(框630)。例如,测量电路可(例如,使用微处理器)确定与触觉负载相关联的阻抗,如上所述。

[0122]

过程600可包括附加实现,诸如下文和/或结合在本文中他处所描述的一个或多个其他过程所描述的任何单个实现或各实现的任何组合。

[0123]

在第一实现中,触觉负载包括lra。

[0124]

在第二实现中,单独地或与第一实现结合地,过程600进一步包括:(例如,使用至少一个第三晶体管403b)驱动触觉负载的第二节点,并(例如,使用第二adc 404b)输出与触觉负载的阻抗相关联的第二比率。第二adc可具有并联连接到第四晶体管(例如,至少一个第二晶体管404b)的漏极的第一节点并且可具有连接到触觉负载的第二节点的第二节点。附加地,第四晶体管可具有连接到第三晶体管的栅极的栅极并且可具有连接到第二参考电流的漏极。

[0125]

在第三实现中,单独地或与第一和第二实现中的一者或多者结合地,过程600进一步包括:(例如,使用微处理器)将触觉负载的阻抗与阈值进行比较,并且当阻抗满足阈值时(例如,使用微处理器)生成误差信号。

[0126]

在第四实现中,单独地或与第一到第三实现中的一者或多者结合地,第一晶体管的源极和第二晶体管的源极连接到电源。

[0127]

在第五实现中,单独地或与第一到第四实现中的一者或多者结合地,第一晶体管的源极和第二晶体管的源极连接到接地。

[0128]

尽管图6示出了过程600的示例框,但在一些实现中,过程600可包括与图6中所描绘的框相比附加的框、较少的框、不同的框或不同地布置的框。附加地或替换地,过程600的两个或更多个框可以并行执行。

[0129]

以下提供了本公开的一些方面的概览:

[0130]

方面1:一种由测量电路执行的方法,包括:使用第一晶体管来驱动触觉负载的第一节点;以及当驱动该触觉负载的电压满足第一条件时触发第一比较器,其中该第一比较器具有并联连接到第二晶体管的漏极的第一节点并具有连接到该触觉负载的第一节点的第二节点,并且其中该第二晶体管具有连接到该第一晶体管的栅极的栅极并具有连接到第一参考电流的漏极。

[0131]

方面2:如方面1的方法,其中,该触觉负载包括线性谐振致动器。

[0132]

方面3:如方面1至2中任一者的方法,进一步包括:使用第三晶体管来驱动该触觉负载的第二节点;以及当驱动该触觉负载的该电压满足第二条件时触发第二比较器,其中该第二比较器具有并联连接到第四晶体管的漏极的第一节点并具有连接到该触觉负载的

第二节点的第二节点,并且其中该第四晶体管具有连接到该第三晶体管的栅极的栅极并具有连接到第二参考电流的漏极。

[0133]

方面4:如方面3的方法,进一步包括:在门处将来自该第一比较器的输出与来自该第二比较器的输出进行组合,其中该门连接到该第一比较器和该第二比较器。

[0134]

方面5:如方面1至4中任一者的方法,进一步包括:使用微处理器至少部分地基于驱动该触觉负载的该电压、来自该第一比较器的输出、该第一参考电流、以及与该第二晶体管相关联的感测比率来确定与该触觉负载相关联的阻抗。

[0135]

方面6:如方面5的方法,进一步包括:使用该微处理器来将与该触觉负载相关联的该阻抗与阈值进行比较;以及当该阻抗满足该阈值时使用该微处理器生成误差信号。

[0136]

方面7:如方面1至6中任一者的方法,进一步包括:使用微处理器来扫掠驱动该触觉负载的多个电压;以及使用该微处理器至少部分地基于使用该多个电压的二分搜索来确定与该触觉负载相关联的阻抗。

[0137]

方面8:如方面1至7中任一者的方法,进一步包括:使用微处理器来扫掠该第二晶体管的多个参考电流;以及使用该微处理器至少部分地基于使用该多个参考电流的二分搜索来确定与该触觉负载相关联的阻抗。

[0138]

方面9:如方面1至8中任一者的方法,进一步包括:使用微处理器来扫掠与该第二晶体管相关联的多个感测比率;以及使用该微处理器至少部分地基于使用该多个感测比率的二分搜索来确定与该触觉负载相关联的阻抗。

[0139]

方面10:如方面1至9中任一者的方法,其中,该第一晶体管的源极和该第二晶体管的源极连接到电源。

[0140]

方面11:如方面1至9中任一者的方法,其中,该第一晶体管的源极和该第二晶体管的源极连接到接地。

[0141]

方面12:如方面1至11中任一者的方法,进一步包括:利用微处理器使用电压波形来驱动该触觉负载;以及使用该微处理器至少部分地基于触发点来确定与该触觉负载相关联的阻抗,该触发点与该电压波形相关联并且是至少部分地基于该第一比较器的输出来确定的。

[0142]

方面13:如方面12的方法,其中,该电压波形包括正弦波或三角波。

[0143]

方面14:一种由测量电路执行的方法,包括:使用第一晶体管来驱动触觉负载的第一节点;以及使用第一模数转换器来输出与该触觉负载的阻抗相关联的第一比率,其中该第一模数转换器具有并联连接到第二晶体管的漏极的第一节点并具有连接到该触觉负载的第一节点的第二节点,并且其中该第二晶体管具有连接到该第一晶体管的栅极的栅极并具有连接到第一参考电流的漏极。

[0144]

方面15:如方面14的方法,其中,该触觉负载包括线性谐振致动器。

[0145]

方面16:如方面14至15中任一者的方法,进一步包括:使用第三晶体管来驱动该触觉负载的第二节点;以及使用第二模数转换器来输出与该触觉负载的阻抗相关联的第二比率,其中该第二模数转换器具有并联连接到第四晶体管的漏极的第一节点并具有连接到该触觉负载的第二节点的第二节点,并且其中该第四晶体管具有连接到该第三晶体管的栅极的栅极并具有连接到第二参考电流的漏极。

[0146]

方面17:如方面14至16中任一者的方法,进一步包括:使用微处理器至少部分地基

于驱动该触觉负载的电压、该第一比率、该第一参考电流、以及与该第二晶体管相关联的感测比率来确定该触觉负载的该阻抗。

[0147]

方面18:如方面17的方法,进一步包括:使用该微处理器来将该触觉负载的该阻抗与阈值进行比较;以及当该阻抗满足该阈值时使用该微处理器生成误差信号。

[0148]

方面19:如方面14至18中任一者的方法,其中,该第一晶体管的源极和该第二晶体管的源极连接到电源。

[0149]

方面20:如方面14至18中任一者的方法,其中,该第一晶体管的源极和该第二晶体管的源极连接到接地。

[0150]

方面21:一种用于执行如方面1-13中的一个或多个方面的方法的测量电路。

[0151]

方面22:一种设备,包括:存储器和耦合到该存储器的一个或多个处理器,该存储器和该一个或多个处理器被配置成执行如方面1-13中的一个或多个方面的方法。

[0152]

方面23:一种装备,包括:用于执行如方面1-13中的一个或多个方面的方法的至少一个装置。

[0153]

方面24:一种存储代码的非瞬态计算机可读介质,该代码包括可由一个或多个微处理器执行以执行如方面1-13中的一个或多个方面的方法的指令。

[0154]

方面25:一种存储指令集的非瞬态计算机可读介质,该指令集包括在由一个或多个微处理器执行时使该一个或多个微处理器执行如方面1-13中的一个或多个方面的方法的一条或多条指令。

[0155]

方面26:一种用于执行如方面14-20中的一个或多个方面的方法的测量电路。

[0156]

方面27:一种设备,包括:存储器和耦合到该存储器的一个或多个处理器,该存储器和该一个或多个处理器被配置成执行如方面14-20中的一个或多个方面的方法。

[0157]

方面28:一种装备,包括:用于执行如方面14-20中的一个或多个方面的方法的至少一个装置。

[0158]

方面29:一种存储代码的非瞬态计算机可读介质,该代码包括可由一个或多个微处理器执行以执行如方面14-20中的一个或多个方面的方法的指令。

[0159]

方面30:一种存储指令集的非瞬态计算机可读介质,该指令集包括在由一个或多个微处理器执行时使该一个或多个微处理器执行如方面14-20中的一个或多个方面的方法的一条或多条指令。

[0160]

前述公开提供了解说和描述,但不旨在穷举或将各方面限于所公开的精确形式。修改和变体可以鉴于以上公开内容来作出或者可通过实践各方面来获得。

[0161]

如本文所使用的,术语“组件”旨在被宽泛地解释为硬件、固件和/或硬件与软件的组合。如本文所使用的,处理器用硬件、固件、和/或硬件与软件的组合来实现。本文所描述的系统和/或方法可以按硬件、固件、和/或硬件与软件的组合的不同形式来实现将会是显而易见的。用于实现这些系统和/或方法的实际的专用控制硬件或软件代码不限制各方面。由此,这些系统和/或方法的操作和行为在本文中在不参照特定软件代码的情况下描述——理解到,软件和硬件可被设计成至少部分地基于本文的描述来实现这些系统和/或方法。

[0162]

如本文中所使用的,取决于上下文,满足阈值可指值大于阈值、大于或等于阈值、小于阈值、小于或等于阈值、等于阈值、不等于阈值、等等。

[0163]

尽管在权利要求书中叙述和/或在说明书中公开了特定特征组合,但这些组合不旨在限制各个方面的公开。事实上,许多这些特征可以按权利要求书中未专门叙述和/或说明书中未公开的方式组合。尽管以下列出的每一项从属权利要求可以直接从属于仅仅一项权利要求,但各个方面的公开包括每一项从属权利要求与这组权利要求中的每一项其他权利要求相组合。如本文中所使用的,引述一列项目“中的至少一者”的短语是指这些项目的任何组合,包括单个成员。作为示例,“a、b或c中的至少一者”旨在涵盖:a、b、c、a-b、a-c、b-c、和a-b-c,以及具有多个相同元素的任何组合(例如,a-a、a-a-a、a-a-b、a-a-c、a-b-b、a-c-c、b-b、b-b-b、b-b-c、c-c、和c-c-c,或者a、b和c的任何其他排序)。

[0164]

本文所使用的元素、动作或指令不应被解释为关键或必要的,除非被明确描述为这样。而且,如本文所使用的,冠词“一”和“某一”旨在包括一个或多个项目,并且可以与“一个或多个”互换地使用。此外,如本文所使用的,冠词“该”旨在包括结合冠词“该”来引用的一个或多个项目,并且可与“一个或多个”可互换地使用。此外,如本文中使用的,术语“集(集合)”和“群”旨在包括一个或多个项目(例如,相关项、非相关项、或者相关项和非相关项的组合),并且可以与“一个或多个”可互换地使用。在旨在仅有一个项目的场合,使用短语“仅一个”或类似语言。而且,如本文所使用的,术语“具有”、“含有”、“包含”等旨在是开放性术语。此外,短语“基于”旨在意指“至少部分地基于”,除非另外明确陈述。而且,如本文中所使用的,术语“或”在序列中使用时旨在是包括性的,并且可与“和/或”互换地使用,除非另外明确陈述(例如,在与“中的任一者”或“中的仅一者”结合使用的情况下)。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1