芯片的信号测试方法、系统、设备、存储介质及程序产品与流程

1.本公开涉及但不限于半导体技术领域,尤其涉及一种芯片的信号测试方法、系统、设备、存储介质及程序产品。

背景技术:

2.随着半导体技术的不断发展,芯片中的集成电路的功能日益复杂,其规模也日益庞大。为保证集成电路符合设计要求,对集成电路进行仿真测试是必不可少的一环。仿真测试通常包括前仿真测试和后仿真测试,前仿真测试是针对寄存器传输级(register transfer lever,简称rtl)的仿真测试,用于分析集成电路的逻辑关系的正确性。后仿真测试涉及集成电路的门延迟参数,以及集成电路中的各电子元件的寄生电容,用于判断集成电路的时序是否正确。

3.然而,在仿真测试中,芯片具有多个输入信号,每个输入信号通常需要人工搭建不同的测试电路,测试效率较低。

技术实现要素:

4.鉴于上述问题,本公开实施例提供一种芯片的信号测试方法、系统、设备、存储介质及程序产品,用于提高芯片的测试效率。

5.本公开实施例的第一方面提供一种芯片的信号测试方法,所述芯片具有多个输入信号,所述信号测试方法包括:获取所述芯片的所有所述输入信号;获得每个所述输入信号的时间参数;将所有所述输入信号的时间参数生成结果表格。

6.本公开实施例提供的芯片的信号测试方法至少具有如下优点:

7.本公开实施例中的芯片的信号测试方法中,通过对芯片的所有输入信号进行获取,并获得各输入信号的上升时间和下降时间,得到所有输入信号的结果表格,实现芯片的输入信号的批量获取和测试,从而提高电路设计者的设计效率,便于设计测试电路,提高测试效率。

8.如上所述的芯片的信号测试方法中,每个所述输入信号对应一组电路单元,每组所述电路单元包括一个驱动电路和至少一个负载电路。

9.如上所述的芯片的信号测试方法中,获得每个所述输入信号的时间参数包括:提取每个所述输入信号对应的一组电路单元中的寄生电阻电容网络电路;根据相对应的所述电路单元和所述寄生电阻电容网络电路,生成每个所述输入信号的测试电路;利用所述测试电路测试对应的所述输入信号,获得所述输入信号的所述时间参数。

10.如上所述的芯片的信号测试方法中,根据相对应的所述电路单元和所述寄生电阻电容网络电路,生成每个所述输入信号的测试电路,包括:确定所述驱动电路对应的第一替换单元;确定各所述负载电路对应的第二替换单元;根据所述第一替换单元、所述至少一个第二替换单元和所述寄生电阻电容网络电路,生成所述测试电路。

11.如上所述的芯片的信号测试方法中,确定所述驱动电路对应的第一替换单元,包

括:在所述驱动电路中提取一级驱动单元,所述一级驱动单元包括所述驱动电路中的第一级逻辑单元;将所述驱动电路中的第一级逻辑单元确定为所述第一替换单元。

12.如上所述的芯片的信号测试方法中,所述驱动电路中的第一级逻辑单元为反相器。

13.如上所述的芯片的信号测试方法中,针对所述至少一个负载电路中的任意一个负载电路,确定所述负载电路对应的第二替换单元,包括:在所述负载电路中提取一级负载单元,所述一级负载单元包括所述负载电路中的第一级逻辑单元;将所述负载电路中的第一级逻辑单元确定为所述第二替换单元。

14.如上所述的芯片的信号测试方法中,所述负载电路中的第一级逻辑单元为标准逻辑单元,包括反相器、与门、或门、非门、与非门、或非门。

15.如上所述的芯片的信号测试方法中,根据所述第一替换单元、所述至少一个第二替换单元和所述寄生电阻电容网络电路,生成所述测试电路,包括:通过第一端口,连接所述第一替换单元和所述寄生电阻电容网络电路;以及,通过至少一个第二端口,连接所述至少一个第二替换单元和所述寄生电阻电容网络电路,得到所述测试电路。

16.如上所述的芯片的信号测试方法中,利用所述测试电路测试相对应的所述输入信号,获得所述输入信号的所述时间参数,包括:通过所述第一替换单元的输入端向所述测试电路输入所述输入信号;获取所述测试电路的至少一个第二替换单元的输入端的至少一个结果信号;根据所述至少一个结果信号,确定所述输入信号的所述时间参数。

17.如上所述的芯片的信号测试方法中,根据所述至少一个结果信号,确定所述输入信号的所述时间参数,包括:获取每个结果信号的时间参数;将所述至少一个结果信号的时间参数中的最大值确定为所述输入信号的时间参数。

18.如上所述的芯片的信号测试方法中,提取每个所述输入信号对应的一组电路单元中的寄生电阻电容网络电路,包括:确定标准寄生参数格式文件;根据所述标准寄生参数格式文件,建立所述寄生电阻电容网络电路。

19.本公开实施例的第二方面提供一种芯片的信号测试系统,所述芯片具有多个输入信号,所述信号测试系统包括:第一获取模块,用于获取所述芯片的所有的所述输入信号;第二获取模块,用于获得每个所述输入信号的时间参数;处理模块,用于将所有的所述输入信号的时间参数生成结果表格。

20.本公开实施例提供的芯片的信号测试系统至少具有如下优点:

21.本公开实施例中的芯片的信号测试系统中,通过第一获取模块获取所有的输入信号,并通过第二获取模块获得各输入信号的上时间参数,处理模块将获得的各输入信号的时间参数生成结果表格,实现芯片的输入信号的批量测试,提高电路设计者的设计效率,便于设计测试电路,提高芯片的测试效率,从而提高测试效率。

22.如上所述的芯片的信号测试系统,每个所述输入信号对应一组电路单元,每组所述电路单元包括一个驱动电路和至少一个负载电路。

23.如上所述的芯片的信号测试系统,所述第二获取模块包括:第一获取子模块,用于提取每个所述输入信号对应的一组电路单元中寄生电阻电容网络电路;生成模块,用于根据相对应的所述电路单元和所述寄生电阻电容网络电路,生成每个所述输入信号的测试电路;测试模块,用于利用所述测试电路测试相对应的所述输入信号,获得所述输入信号的所

述时间参数。

24.本公开实施例的第三方面提供一种设备,包括:至少一个处理器和存储器,所述存储器存储计算机执行指令;所述至少一个处理器执行所述存储器存储的计算机执行指令,使得所述至少一个处理器执行如上所述的信号测试方法。本公开实施例中的设备用于执行上述信号测试方法,因而至少具有上述信号测试方法的优点,具体效果参照上文所述,在此不再赘述。

25.本公开实施例的第四方面提供一种存储介质,所述存储介质中存储有计算机执行指令,当处理器执行所述计算机执行指令时,实现如上所述的信号测试方法。本公开实施例中的存储介质用实现上述信号测试方法,因而至少具有上述信号测试方法的优点,具体效果参照上文所述,在此不再赘述。

26.本公开实施例的第五方面提供一种程序产品,包括计算机程序,该计算机程序被处理器执行时实现如上所述的信号测试方法。本公开实施例中的程序产品实现上述信号测试方法,因而至少具有上述信号测试方法的优点,具体效果参照上文所述,在此不再赘述。

附图说明

27.为了更清楚地说明本公开实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

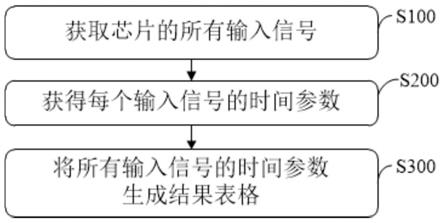

28.图1为本公开实施例中的信号测试方法的流程图;

29.图2为本公开实施例中的输入信号的一种示意图;

30.图3为本公开实施例中的输入信号的另一种示意图;

31.图4为本公开实施例中的寄生电阻电容网络电路的示意图;

32.图5为本公开实施例中的测试电路的示意图;

33.图6为本公开实施例中的一个结果信号的示意图;

34.图7为本公开实施例中的另一个结果信号的示意图。

35.附图标记说明:

36.10-驱动电路;

37.11-驱动电路中的第一级逻辑单元;

38.20-负载电路;

39.21-负载电路中的第一级逻辑单元;

40.30-寄生电阻电容网络电路;

41.40-第一端口;

42.50-第二端口。

具体实施方式

43.针对芯片的测试效率较低的问题,本公开实施例提供的信号测试方法中,通过对芯片的所有输入信号进行获取,并获得各输入信号的时间参数,得到所有输入信号的时间参数的结果表格,实现芯片的输入信号的批量获取和测试,提高电路设计者的设计效率,便

于设计测试电路,从而提高芯片的测试效率。

44.为了使本公开实施例的上述目的、特征和优点能够更加明显易懂,下面将结合本公开实施例中的附图,对本公开实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本公开的一部分实施例,而不是全部的实施例。基于本公开中的实施例,本领域普通技术人员在没有作出创造性劳动的前提下所获得的所有其它实施例,均属于本公开保护的范围。

45.芯片(chip)包括封装在内部的集成电路(integrated circuit,简称ic),以及与该集成电路电连接的引脚(pin),通过引脚输入和输出所需的各种信号。对于芯片不同的输入信号,其在集成电路中的传输路径以及输入、输出芯片时的引脚可以不同。通过测试芯片的输入信号的时间参数,例如上升时间、下降时间、正占空比、负占空比、周期、频率等,可以评估芯片的响应速度。本公开实施例中以时间参数为上升时间和下降时间为例进行阐述。

46.参考图1,图1为本公开实施例中的信号测试方法的流程图,该信号测试方法包括以下步骤:

47.步骤s100:获取芯片的所有输入信号。

48.芯片包括多个输入信号,通过脚本获取芯片的所有的输入信号。这些输入信号可以通过不同的信号名称来进行区分,例如,信号名称可以为signal_1、signal_2、signal_3等。各输入信号的输入引脚和输出引脚不同,输入引脚是指输入信号输入芯片时的引脚,输出引脚是指该输入信号由芯片输出时的引脚。

49.每个输入信号可以为方波信号,理想的波形的如图2所示,该波形的上升沿和下降沿均非常陡峭,由低电平上升至高电平以及由高电平下降至低电平的时间均为零。输入信号往往难以达到理想的波形,由于输入信号往往通过上升沿触发动作。如图3所示,实际的波形中由高电平的10%上升到高电平的90%所经历的时间小于或者等于10皮秒,以使实际的波形接近理想的波形,减少输入信号本身的波形对测试结果的影响。当然,本公开实施例中的输入信号的种类并不是限定的,例如,输入信号还可以为交流(ac)缓变信号。

50.步骤s200:获得每个输入信号的时间参数。

51.每个输入信号所经过的电路可以不同。示例性的,每个输入信号对应一组电路单元,每组电路单元包括一个驱动电路10和至少一个负载电路20,输入信号由相对应的驱动电路10经内部电路传输至负载电路20。由于每组电路单元中的上拉电阻、下拉电阻以及寄生电阻、电容的影响,反应为每组电路单元的驱动能力的不同,导致输入信号的波形产生变化。

52.具体的,输入信号的波形的上升沿平缓上升,下降沿平缓下降,使得输入信号产生较大的延时。通过获取每个输入信号的时间参数,可以评估输入信号的延时,进而评估芯片的响应速度。其中,时间参数可以包括上升时间和下降时间中的至少一个。

53.上升时间可以是指信号从高电平的10%上升到90%所经历的时间,或者信号从高电平的20%上升到80%所经历的时间。下降时间是指信号从高电平的90%下降到10%所经历的时间,或者信号从高电平的80%下降到20%所经历的时间。本公开实施例中,以上升时间为信号从高电平的10%上升到90%所经历的时间,下降时间为信号从高电平的90%下降到10%所经历的时间为例,进行阐述。

54.步骤s300:将所有输入信号的时间参数生成结果表格。

55.示例性的,将所有的输入信号的上升时间和下降时间生成结果表格,结果表格包括每个输入信号的信号名称(signal name)、上升时间(tr)和下降时间(tf)。当然,结果表格中还可以包括其他信息,例如,每个输入信号所对应的输入引脚(start pin)、输出引脚(end pin)、输入端(force node)、输出端(measure node)、驱动电路中的第一级逻辑单元(driven)等。

56.生成结果表格后,显示结果表格,或者,将结果表格发送到预设设备,以进行存储或者显示,供电路设计者参考,如果输入信号的上升时间和下降时间过大,影响电路性能,则重新设计驱动电路。

57.示例性的,结果表格汇总了各输入信号的所有信息。参考表1,输入信号signal_1的上升时间为2.065ns,下降时间为1.856ns,输入引脚为in_1,输出引脚为out_1,一级驱动单元为ddinvf8,输入端为gate_in_1,输出端为gate_out_1。

58.输入信号signal_2的上升时间为1.873ns,下降时间为1.735ns,输入引脚为in_2,输出引脚为out_2,一级驱动单元为ddinvf8,输入端为gate_in_2,输出端为gate_out_2。

59.输入信号signal_3的上升时间为1.849ns,下降时间为1.589ns,输入引脚为in_3,输出引脚为out_3,一级驱动单元为gdinvf8,输入端为gate_in_3,输出端为gate_out_3。

60.输入信号signal_4的上升时间为1.837ns,下降时间为1.5ns,输入引脚为in_4,输出引脚为out_4,一级驱动单元为kdinvf8,输入端为gate_in_4,输出端为gate_out_4。

61.其中,ddinvf8、gdinvf8与kdinvf8分别表示三种不同的反相器,这三种反相器的尺寸不同,其驱动能力不同。具体的,f8表征反相器的finger数目,dd、gd和kd为反相器的代号。

62.表1结果表格

63.signal namestart pinend pindriventr(ns)tf(ns)force nodemeasure nodesignal_1in_1out_1ddinvf82.0651.856gate_in_1gate_out_1signal_2in_2out_2ddinvf81.8731.735gate_in_2gate_out_2signal_3in_3out_3gdinvf81.8491.589gate_in_3gate_out_3signal_4in_4out_4kdinvf81.8371.5gate_in_4gate_out_4

64.综上,本公开实施例中的芯片的信号测试方法中,通过对芯片的所有输入信号进行获取,并获得各输入信号的时间参数,得到结果表格,该结果表格中包含所有输入信号的时间参数,实现芯片的输入信号的批量获取和测试,提高电路设计者的设计效率,便于优化电路,从而提高芯片的测试效率。

65.在一种可能的实施例中,获得每个输入信号的上升时间和下降时间(步骤200)可以包括以下步骤:

66.步骤s210:提取每个输入信号对应的一组电路单元中的寄生电阻电容网络电路。

67.在一些可能的实施例中,提取每个输入信号对应的一组电路单元中的寄生电阻电容网络电路可以包括:

68.步骤s211:确定电路单元的标准寄生参数格式(standard parasitic forma,简称spf)文件,标准寄生参数格式文件可以为标准寄生参数格式网表(netlist)。

69.其中,每个输入信号对应一组电路单元,每组电路单元包括一个驱动电路10和至少一个负载电路20。输入信号依次经过驱动电路10、驱动电路10与负载电路20之间的信号

传输线,以及负载电路20。如图4所示,a处所示的区域为驱动电路10,b处和c处所示的区域为负载电路20,即该输入信号对应一个驱动电路10和两个负载电路20,驱动电路10与负载电路20的具体结构没有画出,当然一个输入信号也可能对应一个负载电路或者多个负载电路,本实施例对此不做限定。

70.为方便描述,本实施例及以下各实施例均以输入信号对应一个驱动电路10和两个负载电路20为例进行描述。

71.确定与每个输入信号相对应的第一端口40和第二端口50,从而确定第一端口40和第二端口50之间的电路单元。其中,第一端口40是指驱动电路10中用于输出该输入信号的端口,第一端口40如图4中p1处所示,第二端口50是指负载电路20中用于接收该输入信号的端口,第二端口50如图4中p2和p3处所示。

72.具体的,通过获取第一端口40和第二端口50之间的电路和对应的版图,通过对电路和版图进行lvs(layout vs schematic)抽取,获取标准寄生参数格式网表,其中lvs抽取寄生参数一般是通过寄生参数提取工具或者eda软件工具,例如synopsys的star_rc来提取电路版图的寄生参数,提取结果为标准寄生参数格式网表。

73.示例性的,生成芯片中的集成电路的电路图和对应版图后,确认驱动电路10、负载电路20和第一端口40、第二端口50,并利用软件提取第一端口40和第二端口50之间的标准寄生参数格式文件,以建立寄生电阻电容网络电路30,其中寄生电阻电容网路电路30包括连接第一端口40和第二端口50的信号线的寄生电阻、电容。驱动电路10和负载电路20内的电路单元也是通过信号线连接,为了避免重复计算,影响精确度,对驱动电路10,负载电路20进行挖空,即忽略驱动电路10,负载电路20内部连线的寄生电阻、电容,其中挖空可以通过eda软件中的skip cell的功能来实现。

74.步骤s212:根据标准寄生参数格式文件,建立寄生电阻电容网络电路30。示例性的,寄生电阻电容网络电路30如图4中虚线框所示,该寄生电阻电容网络电路30包括三个电阻r1,r2,r3,其中r1,r2,r3的第一端共接,r1的第二端与第一端口40,即图4中的p1连接,r2的第二端与一个第二端口50,即图4中的p2连接,r3的第二端与另一个第二端口50,即图4中的p3连接,r1,r2,r3分别表征了第一端口40与第二端口50之间的信号线的电阻,图4中还包括接地电容(未示出)。

75.步骤s220:根据相对应的电路单元和寄生电阻电容网络电路,生成每个输入信号的测试电路。

76.在一些可能的示例中,根据相对应的电路单元和寄生电阻电容网络电路30,生成每个输入信号的测试电路(步骤s230)包括:

77.步骤s231:确定驱动电路对应的第一替换单元。

78.具体的,在驱动电路10中提取一级驱动单元(driven)。输入信号由驱动电路10的输入端经过多个电路逻辑单元传输至驱动电路10的第一端口40,即驱动电路10的第一端口40为驱动电路10的输出端。一级驱动单元是指输入信号流入的第一级单元,该单元靠近驱动电路10的输入端。

79.一级驱动单元包括驱动电路中的第一级电路逻辑单元11,驱动电路中的第一级电路逻辑单元11为反相器。参考表1,作为第一级电路逻辑单元11的反相器可以有多种设计,如ddinvf8,gdinvf8,kdinvf8,其中可以通过改变反相器中的晶体管的沟道尺寸和栅极的

finger数目,提高反相器的驱动能力。

80.提取一级驱动单元后,将驱动电路10中的第一级电路逻辑单元确定为第一替换单元。示例性的,将反相器确认为第一替代单元。

81.步骤s232:确定各负载电路所对应的第二替换单元。

82.负载电路20包括多个,确定每一个负载电路20所对应的第二替代单元,针对至少一个负载电路20中的任意一个负载电路20,确定该负载电路20对应的第二替换单元,可以包括:

83.在负载电路20中提取一级负载单元(loading),一级负载单元包括负载电路中的第一级逻辑单元21。输入信号由负载电路20的第二端口50传输至负载电路20,即负载电路20的第二端口50为负载电路20的输入端。一级负载单元是指输入信号流入的第一级单元,该单元靠近负载电路20的第二端口50。

84.一级负载单元包括负载电路中的第一级电路逻辑单元21,一级负载单元可以为锁存器,d触发器,选择器等,第一级电路逻辑单元可以为标准逻辑单元(standard cell),包括反相器、与门、与非门、或门、或非门、与或门、与或非、或与、或与否、异或非、非门等。示例性的,负载电路中的第一级逻辑单元21均为反相器。

85.提取一级负载单元后,将负载电路20中的第一级电路逻辑单元确定为第二替换单元。示例性的,将反相器确认为第一替代单元。

86.步骤s233:根据第一替换单元、至少一个第二替换单元和寄生电阻电容网络电路,生成测试电路。

87.获取第一替代单元和至少一个第二替代单元后,根据第一替换单元、至少一个第二替换单元和寄生电阻电容网络电路30可以生成测试电路。即通过第一端口40,连接第一替换单元和寄生电阻电容网络电路30;以及,通过至少一个第二端口50,连接至少一个第二替换单元和寄生电阻电容网络电路30,得到测试电路。

88.参考图5,第一替代单元的输出端p1通过第一端口40连接寄生电阻电容网络电路30,每个第二替换单元的输入端p2,p3通过相对应的第二端口50分别连接寄生电阻电容网络电路30,形成测试电路,其中寄生电阻电容网路电路30包括3个电阻r1,r2,r3,这三个电阻分别代表信号线的寄生电阻,还包括接地电容(未示出)。

89.步骤s230:利用测试电路测试相对应的输入信号,获得输入信号的时间参数。

90.示例性的,利用测试电路测试相对应的输入信号,获得输入信号的上升时间和下降时间,包括以下过程:通过第一替换单元的输入端向测试电路输入信号。如图5所示,第一替代单元的输入端为force node,输入信号由该端经第一替代单元11传输至第一端口40,即p1,再经测试电路中的寄生电阻电容网络电路30传输至第二端口50,即p2和p3,之后经第二替换单元21传输至第二替代单元的输出端。

91.通过第一替换单元的输入端向测试电路输入测试信号之后,获取测试电路的至少一个第二替换单元的输入端的至少一个结果信号。每个第二替代单元的输入端对应一个结果信号,如图5所示的测试电路包括两个第二替代单元,这第二替代单元的输入端分别为measure node 1与measure node2,相应的,该测试电路可以获取两个结果信号。measure node 1所对应的结果信号的波形如图6所示,measure node 2所对应的结果信号的波形如图7所示。

92.获取测试电路的至少一个第二替换单元的输入端的至少一个结果信号之后,根据至少一个结果信号,确定输入信号的上升时间和下降时间。根据结果信号可以确定输入信号的上升时间和下降时间。

93.具体的,当结果信号为一个时,该结果信号的上升时间为输入信号的上升时间,该结果信号的下降时间为输入信号的下降时间。当结果信号为多个时,每个结果信号都具有一个上升时间和一个下降时间,获取每个结果信号的上升时间和下降时间,将所有的上升时间中的最大值作为输入信号的上升时间,并将将所有的下降时间中的最大值作为输入信号的下降时间,即取最差的结果作为输入信号的上升时间/下降时间,如果该结果不能通过,则重新进行电路设计。

94.具体的,当结果信号具有两个时,根据如图6所示的measure node 1所对应的结果信号的波形可以获得该结果信号的上升时间和下降时间,根据如图7所示的measure node 2所对应的结果信号的波形可以获得该结果信号的上升时间和下降时间,将这两个结果信号的上升时间中的最大值确定为输入信号的上升时间,将这两个结果信号的下降时间中的最大值确定为输入信号的下降时间,如图6和图7所示,tr1《tr2,因此该输入信号的上升时间为tr2。

95.本公开实施例中的每一个输入信号都通过上述过程建立测试电路,不同的输入信号所建立的测试电路也不相同。上述过程可以通过脚本或者程序自动进行搭建,提高了测试效率。

96.本公开实施例还提供一种芯片的信号测试系统,芯片具有多个输入信号,信号测试系统包括:第一获取模块、第二获取模块和处理模块。其中,第一获取模块用于获取芯片的所有的输入信号,第二获取模块用于获得每个输入信号的时间参数,处理模块用于将所有的输入信号的时间参数生成结果表格。时间参数可以为上升时间、下降时间、正占空比、负占空比、周期、频率等。

97.每个输入信号对应一组电路单元,每组电路单元包括一个驱动电路和至少一个负载电路。输入信号依次经过驱动电路、驱动电路与负载电路之间的内部电路,以及负载电路。相应的,第二获取模块包括:

98.第一获取子模块,用于提取每个输入信号对应的一组电路单元中,第一端口和第二端口之间的寄生电阻电容网络电路。

99.生成模块,用于根据相对应的电路单元和寄生电阻电容网络电路,生成每个输入信号的测试电路。

100.测试模块,用于利用测试电路测试相对应的输入信号,获得输入信号的上升时间和下降时间。

101.本公开实施例中的芯片的信号测试系统中,通过第一获取模块获取所有的输入信号,并通过第二获取模块获得各输入信号的时间参数,处理模块将获得的各输入信号的时间参数生成结果表格,实现芯片的输入信号的批量获取和测试,提高测试效率。

102.本公开实施例还提供一种设备,该设备可以为电子设备,例如计算机或者服务器。设备可以包括至少一个处理器和存储器。其中,存储器存储计算机执行指令,其可以为随机存取存储器(random access memory,简称ram)、只读存储器(read-only memory,简称rom)、可编程只读存储器(programmable read only memory,简称prom)或者可擦除只读存

储器等(erasable programmable read only memory,简称eprom)。

103.至少一个处理器执行存储器存储的计算机执行指令,使得至少一个处理器执行如上的信号测试方法。其中,处理器可以为中央处理器(central processing unit,简称cpu)、网络处理器(network processor,简称np)数字信号处理器(digital signal processor,简称dsp)、专用集成电路(application specific integrated circuit,简称asic)或者其他可编程逻辑器件等。本公开实施例中的设备用于执行上述信号测试方法,因而至少具有上述信号测试方法的优点,具体效果参照上文,在此不再赘述。

104.本公开实施例还提供一种存储介质,存储介质中存储有计算机执行指令,当处理器执行计算机执行指令时,实现如上的信号测试方法。该存储介质可以为u盘、移动硬盘、可读存储器、磁碟或者光盘等可以存储计算机执行指令的介质。本公开实施例中的存储介质用实现上述信号测试方法,因而至少具有上述信号测试方法的优点,具体效果参照上文,在此不再赘述。

105.本公开实施例还提供一种程序产品,包括计算机程序,该计算机程序被处理器执行时实现如上的信号测试方法。本公开实施例中的程序产品实现上述信号测试方法,因而至少具有上述信号测试方法的优点,具体效果参照上文,在此不再赘述。

106.本说明书中各实施例或实施方式采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分相互参见即可。

107.在本说明书的描述中,参考术“一个实施方式”、“一些实施方式”、“示意性实施方式”、“示例”、“具体示例”、或“一些示例”等的描述意指结合实施方式或示例描述的具体特征、结构、材料或者特点包含于本公开的至少一个实施方式或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施方式或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施方式或示例中以合适的方式结合。

108.最后应说明的是:以上各实施例仅用以说明本公开的技术方案,而非对其限制;尽管参照前述各实施例对本公开进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本公开各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1