一种ATE测试通道的自诊断方法与流程

一种ate测试通道的自诊断方法

技术领域

1.本发明属于ate测试领域,具体属于一种ate测试通道的自诊断方法。

背景技术:

2.ate测试机包括若干个测试单板,每一个单板会出若干的测试通道,这些测试通道的需要定时进行诊断。诊断通常需要外接一块独立的诊断单板,使数字通道进行环回,tx发送数据流,rx接收数据流,并判断tx与rx发送的数据流是否一致,来诊断单板的基础信号与基础功能是否满足后续测试需求。

3.采用现有的上述诊断方法存在如下缺陷:

4.1、自诊断的时候必须外接诊断单板,用以支持信号的环回需求。

5.2、软件需要维护tx/rx的连接关系,不同的诊断单板收发环回的通道可能会不一致。

技术实现要素:

6.为了解决上述技术问题,本发明提供了一种ate测试通道的自诊断方法,无需诊断单板作为接受端,可以快速诊断测试通道的基础信号收发功能,可以有效检测相邻测试通道的短路、断路情况。

7.为了实现上述目的,本发明提供了如下技术方案:一种ate测试通道的自诊断方法,包括如下步骤:

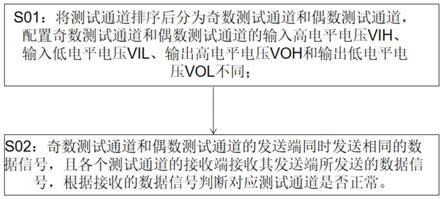

8.s01:将测试通道排序后分为奇数测试通道和偶数测试通道,配置奇数测试通道和偶数测试通道的输入高电平电压vih、输入低电平电压vil、输出高电平电压voh和输出低电平电压vol不同;

9.s02:奇数测试通道和偶数测试通道的发送端同时发送相同的数据信号,且各个测试通道的接收端接收其发送端所发送的数据信号,根据接收的数据信号判断对应测试通道是否正常。

10.进一步的,所有奇数测试通道的输入高电平电压vih、输入低电平电压vil、输出高电平电压voh和输出低电平电压vol对应相等;所有偶数测试通道的输入高电平电压vih、输入低电平电压vil、输出高电平电压voh和输出低电平电压vol对应相等。

11.进一步的,步骤s02中若奇数测试通道和偶数测试通道接收的数据信号等于发射的数据信号,则奇数测试通道和偶数测试通道正常。

12.进一步的,所述奇数测试通道的输入高电平电压vih、输入低电平电压vil、输出高电平电压voh和输出低电平电压vol对应大于偶数测试通道的输入高电平电压vih、输入低电平电压vil、输出高电平电压voh和输出低电平电压vol。

13.进一步的,若相邻的奇数测试通道和/或偶数测试通道接收的数据信号为0,则对应的奇数测试通道和/或偶数测试通道对地短路。

14.进一步的,若偶数测试通道接收的数据信号高于其发送的数据信号,则相邻的奇

数测试通道和偶数测试通道短接。

15.进一步的,所述奇数测试通道的输入高电平电压vih为3.5v,输入低电平电压vil为2.5v、输出高电平电压voh为2v,输出低电平电压vol为3v;所述偶数测试通道的输入高电平电压vih为1.5v、输入低电平电压vil为0v、输出高电平电压voh为1v,输出低电平电压vol为0.5v。

16.进一步的,所述相邻的奇数测试通道的输入高电平电压vih、输入低电平电压vil、输出高电平电压voh和输出低电平电压vol对应大于偶数测试通道的输入高电平电压vih、输入低电平电压vil、输出高电平电压voh和输出低电平电压vol。

17.进一步的,若奇数测试通道和/或偶数测试通道接收的数据信号为0,则对应的奇数测试通道和/或偶数测试通道对地短路。

18.进一步的,若奇数测试通道接收的数据信号高于发送的数据信号,则相邻的奇数测试通道和偶数测试通道短接。

19.本发明具有如下有益效果:相比现有技术中需要依靠诊断单板进行测试通道诊断的方法,本技术利用测试通道本身具备的发送和接收功能,实现自发送和自接收,配合相邻测试通道的不同参数设置,可以快速检测测试通道是否存在对地短路,是否短接等问题,本技术可以快速实现测试通道的自诊断,且诊断方法简单快速,无需依赖外接设备,大大提高了测试通道的诊断速率和效率。

附图说明

20.附图1为本发明测试通道的自诊断方法流程图;

21.附图2为本发明测试通道的内部电路图。

具体实施方式

22.为了对本发明的技术特征、目的和效果有更加清楚的理解,现对照附图详细说明本发明的具体实施方式。以下描述中,需要理解的是,“前”、“后”、“上”、“下”、“左”、“右”、“纵”、“横”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“头”、“尾”等指示的方位或位置关系为基于附图所示的方位或位置关系、以特定的方位构造和操作,仅是为了便于描述本技术方案,而不是指示所指的装置或元件必须具有特定的方位,因此不能理解为对本发明的限制。

23.还需要说明的是,除非另有明确的规定和限定,“安装”、“相连”、“连接”、“固定”、“设置”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。当一个元件被称为在另一元件“上”或“下”时,该元件能够“直接地”或“间接地”位于另一元件之上,或者也可能存在一个或更多个居间元件。术语“第一”、“第二”、“第三”等仅是为了便于描述本技术方案,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量,由此,限定有“第一”、“第二”、“第三”等的特征可以明示或者隐含地包括一个或者更多个该特征。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

24.以下描述中,为了说明而不是为了限定,提出了诸如特定系统结构、技术之类的具体细节,以便透彻理解本发明实施例。然而,本领域的技术人员应当清楚,在没有这些具体

细节的其它实施例中也可以实现本发明。在其它情况中,省略对众所周知的系统、装置、电路以及方法的详细说明,以免不必要的细节妨碍本发明的描述。

25.ate测试机中包括多个测试单板,每个测试单板上包括若干个测试通道,测试通道在正常使用之前均需要先进行诊断,确定测试通道的连接没有故障的时候才能进行正常使用。本技术的目的正是为了提高一种简单快速的测试通道诊断方法,该方法无需依赖诊断单板就可以实现。测试通道内部电路具体包括比较器电路、驱动电路、负载电路、输入接口和输出接口,输出接口位于驱动电路中,且驱动电路连接被测工件,如附图2所示。

26.本技术提供的一种ate测试通道的自诊断方法,包括如下步骤:

27.s01:将测试通道排序后分为奇数测试通道和偶数测试通道,配置奇数测试通道和偶数测试通道的输入高电平电压vih、输入低电平电压vil、输出高电平电压voh和输出低电平电压vol不同;其中,vih表示施加到器件输入的最小正电压,器件将被逻辑高接受;vil表示施加到器件输入的最大正电压,器件将被逻辑低接受;vol表示器件输出的最大正电压定义为“保证”最大正低电平指定负载电流;voh表示器件输出的最小正电压定义为“保证”最小正高于指定负载电流的高电平。其中,输入接口包含输入高电平电压vih和输入低电平电压vil对应的接口,输出接口包含输出高电平电压voh和输出低电平电压vol对应的接口。

28.s02:奇数测试通道和偶数测试通道的发送端同时发送相同的数据信号,且各个测试通道的接收端接收其发送端所发送的数据信号,根据接收的数据信号判断对应测试通道是否正常。若奇数测试通道和偶数测试通道接收的数据信号等于发射的数据信号,则奇数测试通道和偶数测试通道正常。若相邻的奇数测试通道和/或偶数测试通道接收的数据信号为0,则对应的奇数测试通道和/或偶数测试通道对地短路。若相邻的奇数测试通道和/或偶数测试通道接收的数据信号大于其发射的数据信号,则邻的奇数测试通道和或偶数测试通道短接。

29.优选的,本技术中同一个测试单板上所有奇数测试通道的输入高电平电压vih、输入低电平电压vil、输出高电平电压voh和输出低电平电压vol对应相等;所有偶数测试通道的输入高电平电压vih、输入低电平电压vil、输出高电平电压voh和输出低电平电压vol对应相等。这样便于测试通道的数据设置,同时可以对所有的测试通道一起进行测试。

30.具体的,奇数测试通道和或偶数测试通道的参数配置可以分为如下两种情况:

31.(1)奇数测试通道的输入高电平电压vih、输入低电平电压vil、输出高电平电压voh和输出低电平电压vol对应大于偶数测试通道的输入高电平电压vih、输入低电平电压vil、输出高电平电压voh和输出低电平电压vol。

32.(2)相邻的奇数测试通道的输入高电平电压vih、输入低电平电压vil、输出高电平电压voh和输出低电平电压vol对应大于偶数测试通道的输入高电平电压vih、输入低电平电压vil、输出高电平电压voh和输出低电平电压vol。

33.实施例1

34.本技术提供的一种ate测试通道的自诊断方法,包括如下步骤:

35.s01:将测试通道排序后分为奇数测试通道和偶数测试通道,设置奇数测试通道的输入高电平电压vih为3.5v,输入低电平电压vil为2.5v、输出高电平电压voh为2v,输出低电平电压vol为3v;偶数测试通道的输入高电平电压vih为1.5v、输入低电平电压vil为0v、输出高电平电压voh为1v,输出低电平电压vol为0.5v。

36.s02:奇数测试通道和偶数测试通道的发送端同时发送相同的数据信号,且各个测试通道的接收端接收其发送端所发送的数据信号,根据接收的数据信号判断对应测试通道是否正常。若奇数测试通道和偶数测试通道接收的数据信号等于发射的数据信号,则奇数测试通道和偶数测试通道正常。若相邻的奇数测试通道和/或偶数测试通道接收的数据信号为0,则对应的奇数测试通道和/或偶数测试通道对地短路。若偶数测试通道接收的数据信号高于其发送的数据信号,则相邻的奇数测试通道和偶数测试通道短接。

37.实施例2

38.本技术提供的一种ate测试通道的自诊断方法,包括如下步骤:

39.s01:将测试通道排序后分为奇数测试通道和偶数测试通道,设置偶数测试通道的输入高电平电压vih为3.5v,输入低电平电压vil为2.5v、输出高电平电压voh为2v,输出低电平电压vol为3v;奇数测试通道的输入高电平电压vih为1.5v、输入低电平电压vil为0v、输出高电平电压voh为1v,输出低电平电压vol为0.5v。

40.s02:奇数测试通道和偶数测试通道的发送端同时发送相同的数据信号,且各个测试通道的接收端接收其发送端所发送的数据信号,根据接收的数据信号判断对应测试通道是否正常。若奇数测试通道和偶数测试通道接收的数据信号等于发射的数据信号,则奇数测试通道和偶数测试通道正常。若相邻的奇数测试通道和/或偶数测试通道接收的数据信号为0,则对应的奇数测试通道和/或偶数测试通道对地短路。若奇数测试通道接收的数据信号高于其发送的数据信号,则相邻的奇数测试通道和偶数测试通道短接。

41.相比现有技术中需要依靠诊断单板进行测试通道诊断的方法,本技术利用测试通道本身具备的发送和接收功能,实现自发送和自接收,配合相邻测试通道的不同参数设置,可以快速检测测试通道是否存在对地短路,是否短接等问题,本技术可以快速实现测试通道的自诊断,且诊断方法简单快速,无需依赖外接设备,大大提高了测试通道的诊断速率和效率。

42.可以理解的,以上实施例仅表达了本发明的优选实施方式,其描述较为具体和详细,但并不能因此而理解为对本发明专利范围的限制;应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,可以对上述技术特点进行自由组合,还可以做出若干变形和改进,这些都属于本发明的保护范围;因此,凡跟本发明权利要求范围所做的等同变换与修饰,均应属于本发明权利要求的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1