一种三维芯片、芯片单元、可靠性测试方法及相关设备与流程

本技术涉及芯片,尤其涉及一种三维芯片、芯片单元、可靠性测试方法及相关设备。

背景技术:

1、3d ic(三维芯片)是将多个晶片(芯片)在垂直方向进行堆叠互连而形成的一种全新的芯片结构,具有集成度高、功耗低、带宽高、面积小、互连线短、支持异构集成等特点。目前,三维芯片的制备工艺通常采用hb(hybrid bonding,混合键合技术),混合键合技术的可靠性测试大多集中于em(电迁移)、sm(应力迁移)以及封装可靠性测试。

2、然而,目前对于三维芯片的可靠性测试均难以反映相邻两个芯片之间键合结构的可靠性能。

技术实现思路

1、本技术实施例提供一种三维芯片、芯片单元、可靠性测试方法及相关设备,能够评估相邻两个芯片之间键合结构的可靠性能。

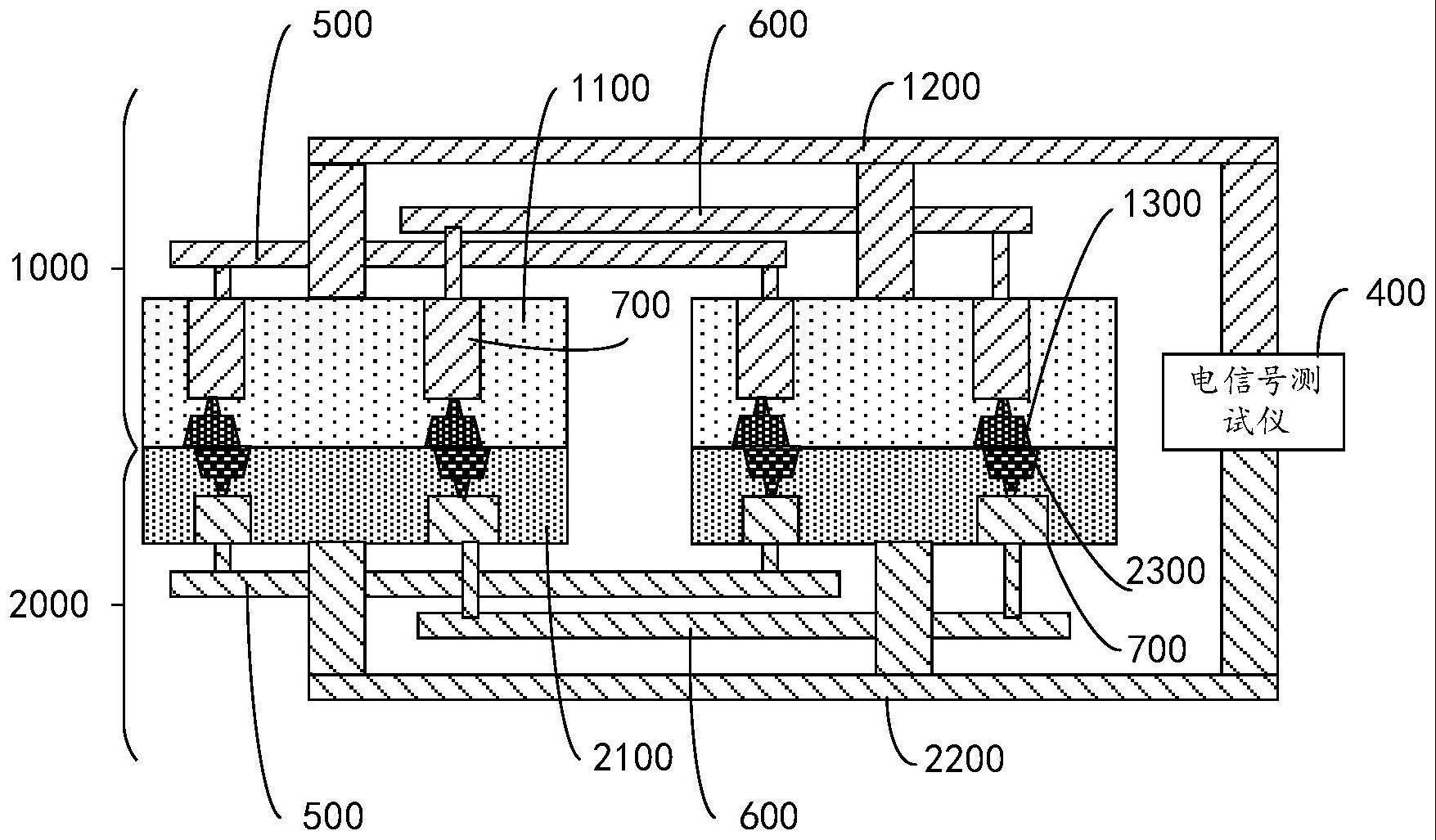

2、本技术实施例的第一方面,提供一种三维芯片,包括:

3、至少两个芯片单元,所述芯片单元包括介质层、穿设于所述介质层的键合结构;

4、所述至少两个芯片单元的所述键合结构键合连接,以形成三维键合结构,以使所述至少两个芯片单元形成三维芯片;

5、其中,所述芯片单元远离所述三维键合结构的一侧设置有测试结构,所述测试结构连接所述介质层,所述测试结构用于传导电荷,且所述测试结构还用于连接电信号测试仪,以使任意两个所述芯片单元上的所述测试结构通过所述电信号测试仪形成漏电流测试回路。

6、在一些实施方式中,所述芯片单元远离所述三维键合结构的一侧还设置有连接所述键合结构的电信号接收端子,所述电信号接收端子用于接收检测信号,所述测试结构用于传导所述介质层在所述电信信号接收端子接收所述检测信号的情况下产生的电荷。

7、在一些实施方式中,所述芯片单元还包括:

8、第一电极,所述芯片单元中至少一个所述键合结构与所述第一电极电连接,所述第一电极用于接入高电平电位;

9、第二电极,所述芯片单元中至少一个所述键合结构与所述第二电极电连接,所述第二电极用于接入低电平电位。

10、在一些实施方式中,同一所述芯片单元中,相邻的两个所述键合结构中的一者电连接所述第一电极,另一者电连接所述第二电极。

11、在一些实施方式中,同一所述三维键合结构中,对应连接的两个所述键合结构电连接所述第一电极;或者,

12、对应连接的两个所述键合结构电连接所述第二电极。

13、在一些实施方式中,所述芯片单元还包括:

14、顶层金属层,所述测试结构、所述第一电极和所述第二电极均设置在所述顶层金属层内。

15、本技术实施例的第二方面,提供一种芯片单元,包括:

16、介质层、穿设于所述介质层的键合结构,所述键合结构的键合面用于与其他芯片单元键合;

17、所述芯片单元远离所述键合面的一侧设置有测试结构,所述测试结构与所述介质层连接,所述测试结构用于传导电荷,且所述测试结构还用于连接电信号测试仪。

18、本技术实施例的第三方面,提供一种三维芯片的可靠性测试方法,包括:

19、提供待测芯片,并将所述待测芯片的测试结构与电信号测试仪连接,其中,所述待测芯片包括至少两个芯片单元,所述芯片单元包括介质层、穿设于所述介质层的键合结构,所述至少两个芯片单元的所述键合结构键合连接,以形成三维键合结构,以使所述至少两个芯片单元形成三维芯片,所述测试结构设置于所述芯片单元远离所述三维键合结构的一侧,且所述测试结构连接所述介质层;

20、利用所述电信号测试仪检测所述介质层的漏电状态,以基于所述漏电状态确定所述三维键合结构的可靠性。

21、在一些实施方式中,所述利用所述电信号测试仪检测所述介质层的漏电状态,包括:

22、向待测芯片的电信号接收端子施加检测信号,其中,所述电信号接收端子位于所述芯片单元远离所述三维键合结构的一侧,且连接所述键合结构;

23、利用所述电信号测试仪检测所述介质层的漏电状态。

24、在一些实施方式中,所述基于所述漏电状态确定所述三维键合结构的可靠性,包括:

25、根据所述检测信号和所述漏电状态确定所述三维芯片对应的失效时间;

26、根据所述失效时间,评估所述三维键合结构的可靠性。

27、在一些实施方式中,所述基于所述漏电状态确定所述三维键合结构的可靠性,包括:

28、在不同的测试条件下,测试多个所述三维芯片的漏电流,得到测试样本数据,其中,所述测试条件包括测试电压和测试环境温度;

29、基于所述测试样本数据中的所述漏电流与所述测试条件建立三维芯片寿命评估模型;

30、基于所述三维芯片评估模型以及所述待测芯片的工作条件数据确定所述待测芯片的评估寿命,其中,所述待测芯片的工作条件数据包括工作环境温度和工作电压。

31、在一些实施方式中,所述在不同的测试条件下,测试多个所述三维芯片的漏电流,得到测试样本数据,包括:

32、基于固定测试电压和对应的所述漏电流,确定所述三维芯片在不同所述测试环境温度下的失效时间;

33、根据固定测试环境温度和对应的所述漏电流,确定所述三维芯片在不同所述测试电压下的所述失效时间。

34、在一些实施方式中,所述基于所述测试样本数据中的所述漏电流与所述测试条件建立三维芯片寿命评估模型,包括:

35、确定所述失效时间与不同所述测试环境温度在所述固定测试电压下的拟合关系曲线,得到第一斜率,其中,所述第一斜率用于表征所述失效时间与不同所述测试环境温度的拟合关系曲线的斜率;

36、确定所述失效时间与不同所述测试电压在所述固定测试环境温度下的拟合关系曲线,得到第二斜率,其中,所述第二斜率用于表征所述失效时间与不同所述测试电压的拟合关系曲线的斜率;

37、根据所述第一斜率和所述第二斜率,建立所述三维芯片寿命评估模型。

38、在一些实施方式中,所述基于所述三维芯片评估模型以及所述待测芯片的工作条件数据确定所述待测芯片的评估寿命,包括:

39、根据所述工作电压得到工作电流;

40、将所述待测芯片的所述工作环境温度和所述工作电流输入至所述三维芯片评估模型中,以输出所述评估寿命。

41、本技术实施例的第四方面,提供一种电子设备,包括:

42、如第二方面所述的芯片单元,和/或,如第一方面所述的三维芯片。

43、本技术实施例的第五方面,提供一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如第三方面中任一项所述的可靠性测试方法。

44、本技术实施例的第六方面,提供一种测试设备,包括:

45、存储器,所述存储器中存储有计算机程序;

46、处理器,所述处理器用于执行所述计算机程序时实现如第三方面所述的可靠性测试方法。

47、本技术实施例提供的三维芯片、芯片单元、可靠性测试方法及相关设备,通过在芯片单元中设置有测试结构,测试结构的一端连接介质层,另一端连接电信号测试仪,通过测试结构和漏电流测试仪形成的漏电流测试回路,可以检测介质层中的漏电流,漏电流可以表征三维芯片的漏电情况,通过测试漏电流可以反映键合结构中导电材料的原子扩散程度,根据漏电流评估三维芯片中三维键合结构的可靠性,可以实现根据漏电流的数值评估芯片单元的寿命,进一步评估三维芯片的寿命。

- 还没有人留言评论。精彩留言会获得点赞!