测试装置及方法与流程

本技术涉及测试,具体涉及一种测试装置及方法。

背景技术:

1、集成电路的基于寄存器扫描链的数字逻辑测试(digital logic test based onflip-flop scan chain,简称scan test)的基本原理是:测试装置将测试向量(testvector)描述的测试激励输入待测器件,并接收待测器件输出的测试响应,将测试响应与测试向量描述的期望值进行比对,根据比对结果判断待测器件是否存在制造缺陷。

2、随着集成电路规模的持续增长,数字逻辑的测试向量以及测试时间随之显著增长。通常,测试装置需要通过复用功能数字输入/输出信号(input/output:io)管脚作为测试向量的测试激励/测试响应的传输通道,例如测试装置将测试激励通过输入管脚灌入待测器件内各个子模块(subchip),同时各个子模块将对应的测试响应通过输出管脚反馈给测试装置,这样针对集成电路数字逻辑的测试方法,业界称为低速并行扫描测试,由于待测器件内各个子模块与其对应的输出信号管脚(与测试装置连接)是有简单清晰的映射关系的,因此测试装置根据记录各个响应管脚输出的测试响应比对结果,即可确定各个待测器件各个子模块是否合格。但由于需要的输入输出管脚较多,传输带宽较低,已不能满足测试需求。

3、高速串行扫描测试中测试装置与待测器件通过串行通道连接,待测器件通过串行通道将测试响应反馈至测试装置,测试装置将测试响应与期望响应进行比对,存储比对不合格的测试响应,然后再由测试软件读取不合格的测试响应确定不合格的测试响应来自于哪一个子模块,从而确定出不合格的子模块。高速串行扫描测试仅需使用少量的串行通道传输测试激励与测试响应,可以降低测试成本,由于待测器件各个输出管脚输出的测试响应通过串行通道传输至测试装置,测试装置需要在所有的测试响应比对完成后,再根据比对结果去解算不合格的测试响应是由哪一个待测器件内部哪一个子模块的响应管脚输出的,但串行通道传输带宽较大,传输数据量也较大,但随之而来的,对存储测试响应的比对结果的存储空间要求也增大,根据比对结果解算得到待测器件内部子模块是否存在制造缺陷所需的时间增加,此外,在存储空间有限的情况下,如果测试装置无法存储所有的不合格的比对结果时,可能会存在漏判内部缺陷模块的情况,导致待测器件存在质量风险。

技术实现思路

1、本技术实施例提供一种测试装置及方法,可以在对待测器件进行检测时,降低因存储空间不足,无法存储所有的测试响应比对结果而导致的误判问题,有效减少测试时间,降低测试成本。

2、为达到上述目的,本技术实施例采用如下技术方案:

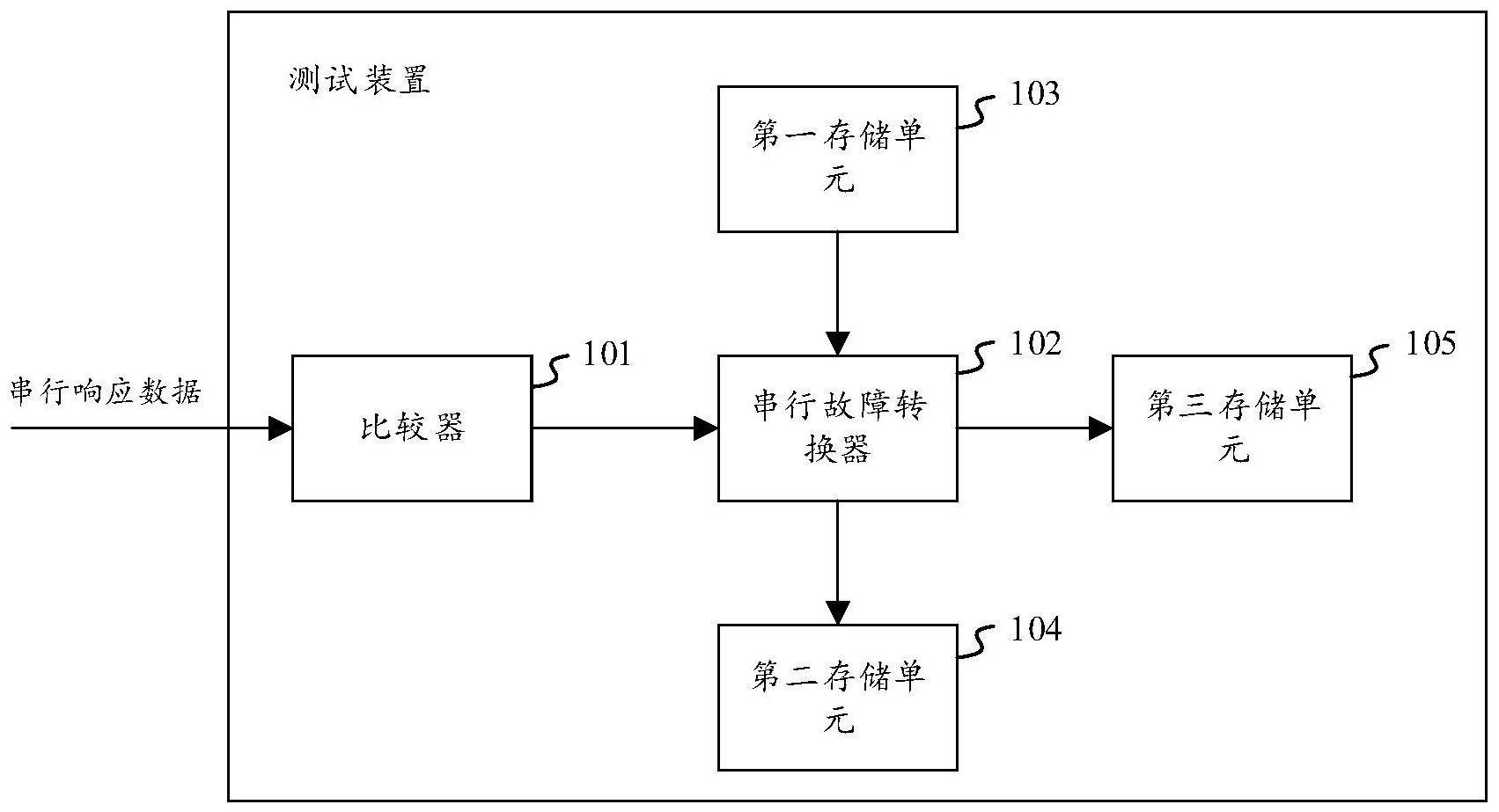

3、第一方面,本技术实施例提供了一种测试装置,测试装置包括:比较器、串行故障转换器、第一存储单元;其中第一存储单元,被配置为存储测试配置信息,测试配置信息包括待测器件的输出管脚与串行通道的对应关系,以及输出管脚输出的测试响应在串行通道的组包顺序;其中,待测器件包括多个输出管脚,多个输出管脚输出的测试响应通过串行通道传输至测试装置;比较器,被配置为将待测器件输出的测试响应与期望响应逐周期进行比对,在测试响应与期望响应比对不合格时生成响应故障信息,响应故障信息包括比对不合格的测试响应的周期序号与通道索引;串行故障转换器,被配置为根据测试配置信息,将响应故障信息转换为管脚故障信息,管脚故障信息包括输出不合格的测试响应的输出管脚的标识,这样,在比较器比对出不合格的测试响应时,即可由串行故障转换器依据测试测试配置信息将故障响应信息转换为待测器件的输出管脚的管脚故障信息,即确定不合格的测试响应是由哪一个输出管脚输出的,相比于将比对结果存储后,再由测试软件去读取比对结果确定测试不合格的输出管脚,本技术提供的方案设置串行故障转换器,比较器比对确定不合格的测试响应通道索引与周期序号时,串行故障转换器可以根据比较器比对的结果进行转换,确定输出该不合格测试响应的数据管脚,即确定测试不合格的输出管脚,无须将比对结果存储后,再读取存储的比对结果进行转换,这样在测试过程中省略了存储比较器比对的结果这一步骤,一方面可以避免因为存储空间不足、无法存储所有的比对不合格的测试响应而造成的误判,不需要存储比对不合格的测试响应,可以降低测试成本,另一方面,还可以缩短测试时间。

4、在一种可能的实施方式中,测试装置还包括第二存储单元,第二存储单元被配置为存储待测器件的输出管脚的状态,输出管脚的状态包括合格与不合格;其中,为在测试装置收到测试响应之前,第二存储单元具体被配置将待测器件的每一个输出管脚的状态配置为合格,这样可以在测试过程中,根据管脚故障信息对相应的输出管脚的状态进行更新。

5、在一种可能的实施方式中,第二存储单元还具体被配置为根据管脚故障信息,将与管脚故障信息匹配的输出管脚的状态由合格更新为不合格,其中管脚故障信息包括输出不合格测试响应的输出管脚的标识,第二存储单元依据该标识,将输出不合格测试响应的输出管脚的状态更新为不合格。

6、在一种可能的实施方式中,串行故障转换器具体被配置为依据串行通道的通道索引以及待测器件的多个输出管脚与串行通道的对应关系,确定串行通道对应的多个输出管脚;串行故障转换器具体还被配置为依据比对不合格的测试响应的周期序号,以及多个输出管脚输出的测试响应在串行通道的组包顺序,确定输出不合格的测试响应的输出管脚的标识。

7、在一种可能的实施方式中,测试配置信息包括待测器件的串行通道与测试装置的连接对应关系;比较器,具体被配置为依据待测器件的串行通道与测试装置的连接对应关系确定不合格的测试响应的通道索引。

8、在一种可能的实施方式中,测试装置还包括第三存储单元,第三存储单元被配置为存储比对不合格的测试响应。在进行故障诊断或者故障分析时需要对不合格的测试响应进行分析,测试装置设置第三存储单元用于存储不合格的测试响应,以便进行故障诊断或者故障分析。

9、在一种可能的实施方式中,第三存储单元具体被配置为存储待测器件的每一个输出管脚输出的比对不合格的测试响应,在第三存储单元存储空间较大的情况下,第三存储单元可以依据待测器件的输出管脚数量进行划分成多份,每一份用于存储一个输出管脚输出的不合格的测试响应。

10、在一种可能的实施方式中,第三存储单元具体被配置为存储待测器件的预先设定的输出管脚输出的比对不合格的测试响应,在第三存储单元存储空间较小的情况下,第三存储单元可以用于存储指定输出管脚输出的不合格的测试响应,以便对特定的输出管脚输出的不合格的测试响应进行故障分析。

11、第二方面,本技术实施例提供一种测试方法,测试方法应用于测试装置,测试装置包括比较器、串行故障转换器、第一存储单元,测试方法包括:第一存储单元存储测试配置信息,测试配置信息包括待测器件的输出管脚与串行通道的对应关系,以及输出管脚输出的测试响应在串行通道的组包顺序,其中,待测器件包括多个输出管脚,多个输出管脚输出的测试响应通过串行通道传输至测试装置;比较器将待测器件输出的测试响应与期望响应逐周期进行比对,在测试响应与期望响应比对不合格时生成响应故障信息,响应故障信息包括比对不合格的测试响应的周期序号与通道索引;串行故障转换器根据测试配置信息将响应故障信息转换为待测器件的输出管脚的管脚故障信息,管脚故障信息包括输出不合格的测试响应的输出管脚的标识,第二方面所达到的有益效果可以参见第一方面中有益效果。

12、在一种可能的实施方式中,测试装置还包括第二存储单元,测试方法还包括:第二存储单元根据管脚故障信息,将与管脚故障信息匹配的输出管脚的状态由合格更新为不合格。

13、在一种可能的实施方式中,在测试装置收到测试响应之前,测试方法还包括:第二存储单元将每一个输出管脚的状态配置为合格。

14、第三方面,本技术实施例提供一种计算机可读存储介质,包括计算机指令,当计算机指令在电子设备上运行时,使得电子设备执行上述第二方面以及第二方面中的任一种可能的实施方式所述的方法。

15、第四方面,本技术实施例提供一种计算机程序产品,当计算机程序产品在计算机上运行时,使得电子设备执行上述第二方面以及第二方面中的任一种可能的实施方式所述的方法。上述其他方面对应的有益效果,可以参见关于方法方面的有益效果的描述,此处不予赘述。

- 还没有人留言评论。精彩留言会获得点赞!