集成电路装置的检测系统、信号源及电源供应装置的制作方法

1.本公开涉及一种集成电路装置的检测系统、信号源及电源供应装置,特别涉及一种通过电源分配而提高测试能力的集成电路装置的检测系统、信号源及电源供应装置。。

背景技术:

2.在集成电路装置制造过程中,测试程序为确保装置功能正常的重要步骤。在典型的测试程序中,利用自动测试机(automated test equipment;ate)产生测试信号。自动测试机耦接晶圆探针测试机台(wafer prober station)。晶圆探针测试机台通过探针头(probe head)及探针卡(probe card)提供测试信号至待测装置(device-under-test,dut);通过测量受测物件对测试信号的响应(例如,通过测量及/或量化所得到的信号),可以得知受测物件的操作及/或性能是否正常。

3.上文的“现有技术”说明仅提供背景技术,并未承认上文的“现有技术”说明揭示本公开的标的,不构成本公开的现有技术,且上文的“现有技术”的任何说明均不应作为本案的任一部分。

技术实现要素:

4.本公开的一实施例提供一种信号源,包括:一电源供应装置,经配置以产生一附加电压、多个基础电压及一编程电压;以及一开关集合,配置在该电源供应装置与该等半导体芯片群组之间,将该附加电压和该等基础电压转换成多个供应电压。

5.在本公开的实施例中,该开关集合包括一第一开关,耦接于该电源供应装置与该等半导体芯片群组之间,并位在该附加电压的传递路径上。

6.在本公开的实施例中,该开关集合包括多个第二开关,电性耦接于该电源供应装置与该等半导体芯片群组之间,并位在该等基础电压的传递路径上。

7.在本公开的实施例中,该等附加电压通过该等第二开关传递至该等半导体芯片群组。

8.在本公开的实施例中,当该等第二开关进入该导通状态时,该电源供应装置提供一基础电流予各该半导体芯片群组,当该第一开关进入一导通状态时,该电源供应装置提供一附加电流予各该半导体芯片群组,该附加电流小于该基础电流。

9.在本公开的实施例中,该开关集合还包括多个第三开关,耦接于该电源供应装置与该复半导体芯片群组之间,并位在该编程电压的传递路径。

10.在本公开的实施例中,当该等第三开关进入一导通状态时,该电源供应装置提供一编程电流予各该半导体芯片群组,该编程电流小于该附加电流。

11.在本公开的实施例中,该编程电流等于该基础电流。

12.在本公开的实施例中,该信号源还包括一控制器,电性连接于该第一开关、该等第二开关及该等第三开关,该第一开关、该等第二开关及该等第三开关接受该控制器的控制而于该导通状态和一断路状态中切换。

13.在本公开的实施例中,该电源供应装置包括:一第一电源供应器,经配置以产生该附加电压;一第二电源供应器,经配置以产生该等基础电压;以及一第三电源供应器,经配置以产生该编程电压。

14.本公开的另一实施例提供一种检测系统,包括:一第一芯片;一第二芯片;以及一电源供应装置;其中该电源供应装置包括一第一电源供应器,经配置以产生一附加电流;以及一第二电源供应器,经配置以产生一第一基础电流及一第二基础电流;其中该附加电流和该第一基础电流中之一者提供予该第一芯片,该附加电流和该第二基础电流提供予该第二芯片。

15.在本公开的实施例中,该检测系统还包括一第一开关,其中该第一电源供应器的该附加电压经该第一开关传递至该第一芯片和该第二芯片。

16.在本公开的实施例中,该检测系统还包括多个第二开关,其中该第一电源供应器的该附加电压和该第二电源供应器的第一基础电流及第二基础电流经该等第二开关分别传递至该第一芯片和该第二芯片。

17.在本公开的实施例中,该检测系统还包括一第三电源供应器,经配置以产生一编程电压予该第一芯片和该第二芯片。

18.在本公开的实施例中,该第一芯片还包括一第一接触垫,该第二芯片还包括一第二接触垫,以及该编程电压经该第一接触垫进入该第一芯片,该编程电压经该第二接触垫进入该第二芯片。

19.在本公开的实施例中,该检测系统还包括多个第三开关,该第三电源供应器的该编程电压经该等第三开关传递至该第一芯片和该第二芯片。

20.本公开的另一实施例提供一种电源供应装置,包括:一第一电源供应器,提供一附加电压;一第二电源供应器,提供一基础电压;以及一第三电源供应器,经配置以提供一编程电压;其中,该第一电源供应器电性耦接于该第二电源供应器以配合产生一组合电流。

21.在本公开的实施例中,该电源供应装置还包括一第一开关,其中该第一电源供应器的该附加电压经该第一开关传递至该第一芯片和该第二芯片。

22.在本公开的实施例中,该电源供应装置还包括多个第二开关,其中该第一电源供应器的该附加电压和该第二电源供应器的该第一基础电流及该第二基础电流经该等第二开关分别传递至该第一芯片和该第二芯片。

23.在本公开的实施例中,该第一芯片还包括一第一接触垫,该第二芯片还包括一第二接触垫,以及该编程电压经该第一接触垫进入该第一芯片,该编程电压经该第二接触垫进入该第二芯片。

24.在本公开的实施例中,该电源供应装置还包括多个第三开关,该第三电源供应器的该编程电压经该等第三开关分别传递至该第一芯片和该第二芯片。

25.上文已相当广泛地概述本公开的技术特征及优点,从而使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中技术人员应了解,可相当容易地利用下文揭示的概念与特定实施例可作为修改或设计其它结构或工艺而实现与本公开相同的目的。本公开所属技术领域中技术人员亦应了解,这类等效建构无法脱离权利要求所界定的本公开的构思和范围。

附图说明

26.参阅实施方式与权利要求合并考量附图时,可得以更全面了解本技术案的揭示内容,附图中相同的元件符号指相同的元件。

27.图1为示意图,例示本公开实施例的检测系统。

28.图2是俯视图,例示本公开实施例的受测物件。

29.图3是示意图,例示本公开实施例的探针组和半导体芯片。

30.图4是电路方块,例示本公开实施例的电信号与反应信号在检测系统与受测物件之间的传递。

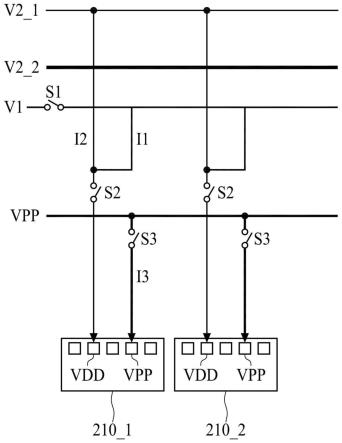

31.图5是电路方框图,例示本公开实施例的信号源和受测物件。

32.图6是电路图,例示本公开实施例的信号源和受测物件。

33.图7是电路方框图,例示本公开实施例的信号源和受测物件。

34.图8是电路图,例示本公开实施例的信号源和受测物件。

35.图9是电路方框图,例示本公开实施例的信号源和受测物件。

36.图10是电路图,例示本公开实施例的信号源和受测物件。

37.【附图标记列表】

38.10:检测系统

39.20:受测物件

40.30:检测系统

41.40:控制器

42.100:平台

43.102:承载表面

44.200_1:半导体芯片群组

45.210_2:半导体芯片群组

46.210:半导体芯片

47.210_1:半导体芯片

48.210_2:半导体芯片

49.212:接触垫

50.212a:接触垫

51.212b:接触垫

52.220:半导体晶圆

53.230:分割预定线

54.310:本体

55.312:测试卡

56.314:探针组

57.316:探针

58.320:信号源

59.325:信号分析器

60.330:电源供应装置

61.320a:信号源

62.325:信号分析器

63.330a:电源供应装置

64.330_1:第一电源供应器

65.330_2:第二电源供应器

66.330_3:第三电源供应器

67.340:开关集合

68.350:控制元件

69.3102:安装面

70.d1:第一距离

71.d2:第二距离

72.i1:附加电流

73.i2:基础电流

74.i3:编程电流

75.s1:第一开关

76.s2:第二开关

77.s3:第三开关

78.v1:附加电压

79.v2_1:基础电压

80.v2_2:附加电压

81.vdd:供应电压

82.vpp:编程电压

具体实施方式

83.本公开的以下说明伴随并入且组成说明书的一部分的附图,说明本公开的实施例,然而本公开并不受限于该实施例。此外,以下的实施例可适当整合以下实施例以完成另一实施例。

[0084]“一实施例”、“实施例”、“例示实施例”、“其他实施例”、“另一实施例”等指本公开所描述的实施例可包含特定特征、结构或是特性,然而并非每一实施例必须包含该特定特征、结构或是特性。再者,重复使用“在实施例中”一语并非必须指相同实施例,然而可为相同实施例。

[0085]

为了使得本公开可被完全理解,以下说明提供详细的步骤与结构。显然,本公开的实施不会限制该技艺中的技术人士已知的特定细节。此外,已知的结构与步骤不再详述,以免不必要地限制本公开。本公开的较佳实施例详述如下。然而,除了详细说明之外,本公开亦可广泛实施于其他实施例中。本公开的范围不限于详细说明的内容,而是由权利要求定义。

[0086]

此外,为易于说明,本文中可能使用例如“之下(beneath)”、“下面(below)”、“下部的(lower)”、“上方(above)”、“上部的(upper)”等空间相对关系用语来阐述图中所示的一个元件或特征与另一(其他(元件或特征的关系。所述空间相对关系用语旨在除图中所示出本公开的的取向外亦囊括元件在使用或操作中的不同取向。所述装置可具有其他取向(旋

转90度或处于其他取向)且本文中所用的空间相对关系描述语可同样相应地进行解释。

[0087]

图1例示本公开的检测系统10的示意图。参照图1,检测系统10包括一受测物件20和一检测系统30;检测系统30经配置以对受测物件20中的多个半导体芯片210的动作及/或性能进行检验,进而判断每个半导体芯片210的效能是否符合设计规格。

[0088]

图2示出本公开的受测物件20的俯视图。参照图2,受测物件20可包括一半导体晶圆220(例如硅晶圆),半导体晶圆220的表面以相互交叉的多个分割预定线230划成多个功能区域,半导体芯片210分别位在功能区域内;换言之,相邻的半导体芯片210由分割预定线230隔开。每个半导体芯片210可包括一或多个主动元件(例如二极管、晶体管)、一或多个无源元件(例如电阻器、电容器),以及用于电性耦接主动元件和无源元件的多个图案化互连构件;主动元件、无源元件和互连构件是通过包括掺杂、沉积、光刻、蚀刻和平坦化等一系列的集成电路装置制作程序而形成在半导体晶圆220中及/或半导体晶圆220的表面上。典型地,受测物件20的半导体芯片210具有相同的结构。于此,半导体芯片210为存储器,例如是包括金属氧化物半导体晶体管和电容器的动态随机存取存储器。

[0089]

半导体芯片210上设有多个接触垫212,可以电性连接于半导体芯片210中的不同的主动元件、无源元件,或者主动元件和无源元件的组合;借此,受测元件20接受测试时,检测系统30可通过接触垫212对主动元件、无源元件,以及由主动元件和无源元件构成的电路的电性进行测量,从而可确保每个半导体芯片210的品质。接触垫212主要以金属材料(例如铜、铝)制作而成。在图2中,每个半导体芯片210的接触垫212呈直线排列,且相邻的两个接触垫212间隔一第一距离d1。在一些实施方式中,接触垫212可排列为矩阵状或其它利于检测系统30进行检测的形状。

[0090]

参照图1,在半导体芯片210制作完成但未进行单体化之前,检测系统30会对受测物件20进行检验,以识别出不满足制作程序要求的半导体芯片210;其中,半导体芯片210的单体化是以机械锯或激光沿着分割预定线230切分半导体晶圆220,以形成多个独立的芯片,每个芯片至少包括一个半导体芯片210。申言之,检测系统30主要是用于对受测物件20执行晶圆层级测试(wafer level test)。

[0091]

参照图1及图3,检测系统30包括一本体310及一测试卡312;本体310可具有一安装面3102,测试卡312固定在本体310的安装面3102上。在一些实施方式中,测试卡312可利用螺丝(未图示)锁固在本体310上。当本体310受到控制器40的驱动而进行平移(即在xy方向移动)或升降(即在z轴方向移动)时,测试卡312的位置将跟着改变。测试卡312设有多个探针组314,每个探针组314包括多个探针316(如图3所示)。探针316主要以导电材料制作而成,例如可选自铂、铑、钯、银、铜、铱或其合金。测试卡312的表面可以布设有导电线路(未图示),导电线路用于让探针组314中相对应的探针316形成电性连接。举例来说,导电线路可以让位在每个探针组314最左侧的探针316形成电性连接。申言之,测试卡312除了供安装探针316,还能够用于传递电信号。在一些实施方式中,测试卡312包含电路板。

[0092]

参照图3,探针316可为垂直式(vertical)探针或旋臂式(cantilever)探针;垂直式探针主要以挫曲提供弹性力,具有小体积、易于组装和更换等特点;悬臂式探针的尖端距离小,适用于对具有窄间距接触垫212的半导体芯片210进行电性检测。在一些实施方式中,探针组314的数量等于受测物件20上半导体芯片210的数量,且探针316的数量可等于接触垫212的数量,借此可以有效地降低检测时间。其次,在每个探针组312中,相邻二探针316的

尖端间隔的一第二距离d2不小于相邻二接触垫212间隔的第一距离d1,借此避免传递错误测试信号给半导体芯片210内的元件或电路,而导致检测结果不正确的问题,甚至是毁坏半导体芯片210内元件的状况。

[0093]

参照图1,检测系统10还可包括平台100,其具有一承载表面102;承载表面102面对探针卡312。在进行检测之前,探针316的尖端与平台100的承载表面102之间的间距大于受测物件20的高度,以利于摆放待测物件20。平台100和检测系统30可分别电性连接于控制器40。在半导体芯片210制作完成之后,受测物件20会被装载在平台100的支持表面102上以准备接受测试。当进行受测物件20的测试时,首先控制器40会水平移动平台100或检测系统30,以让探针卡312的探针316对准半导体芯片210的接触垫212。接着,控制器40可通过将检测系统30的探针卡312下降,而使探针316接触对应的接触垫212。在一些实施方式中,在探针316和接触垫212对准之后,控制器40可以通过使平台100的垂直上升,而让探针316接触接触垫212。控制器40经配置可具有高度检测功能,以使探针316和接触垫212相互接触,但探针316不压迫接触垫212的位置,借此避免半导体芯片210毁坏或探针316断裂。

[0094]

参照图3和图4,在探针316与对应的接触垫212接触之后,检测系统30产生多个电信号s就能够通过探针316传递至半导体芯片210,以对半导体芯片210中的元件及/或由多个元件构成的电路进行电性检测;其中,半导体芯片210中元件或电路检测的参数及内容可以依据设计或使用上的需求而进行调整。

[0095]

参照图4,检测系统30包括至少一信号源320,产生至少一个电信号s。例如,信号源320可放置在检测系统30的本体310中,并通过导线(未图示)而与测试卡312形成电性连接;传递到测试卡312的电信号s,可以通过在其表面及其中的导电线路而传递至探针316。当半导体芯片210为半导体存储器(例如动态随机存取存储器)时,信号源320产生的电信号可包括适于对半导体芯片210进行写入测试和读取测试的指令。

[0096]

参照图4,检测系统30另包括一信号分析器325,接收由半导体芯片210提供的反应信号sr,其中反应信号sr可以呈现半导体芯片210内的元件或电路对检测系统30提供的电信号s作出的响应。检测系统30可通过分析反应信号以确定每个半导体芯片210的基本电性。在完成半导体芯片210的基本电性的测试之后,检测系统10还能够在不良的半导体芯片210处标记,以节省封装和成本测试的成本。在一些实施方式中,探针组314中的部分探针316除了用于将电信号s传递至半导体芯片210,还能够将半导体芯片210提供的反应信号sr传递至检测系统30。

[0097]

参照图4,信号源320产生的电信号可以进一步包括用于驱动半导体芯片210的电力信号;具体言之,检测系统30信号源可包括一或多个电源供应装置330,产生半导体芯片210执行写入测试和读取测试时需求的电压和电流。

[0098]

图5例示本公开实施例的信号源320和受测物件20的功能方框图;图6例示本公开实施例的信号源320和受测物件20的电路图。参照图5和图6,受测物件20包括两个半导体芯片群组200_1和200_2,每个半导体芯片群组200_1和200_2可包括多个半导体芯片210;在一些实施方式中,所有的半导体芯片群组200_1和200_2具有相同数量的半导体芯片210。

[0099]

参照图5及图6,信号源320经配置可产生二供应电压vdd_1、vdd_2和一编程电压vpp。当半导体芯片210为动态随机存取存储器时,供应电压vdd_1、vdd_2用于启动/驱动半导体芯片210,编程电压vpp用于为半导体芯片210的字元线提供电压;进一步地,当半导体

芯片210为第四代双倍数据率同步动态随机存取存储器(double-data-rate fourth generation synchronous dynamic random access memory,简称为ddr4 sdram)时,供应电压vdd_1、vdd_2为1.2伏特,编程电压vpp为2.5伏特。

[0100]

参照图5及图6,信号源320可包括一个电源供应装置330、一开关集合340及一控制元件350。电源供应装置330经配置可以产生一附加电压v1和多个基础电压v2_1、v2_2,开关集合340配置在电源供应装置330和半导体芯片群组200_1和200_2之间,并接受控制元件350的控制而将电源供应装置330产生的附加电压v1和基础电压v2_1、v2_2转换成为供应电压vdd_1、vdd_2。

[0101]

参照图6,开关集合340包括一第一开关s1及多个第二开关s2;其中,第二开关s2的数量等于半导体芯片210的数量。第二开关s2耦接于电源供应装置330和半导体芯片210之间。具体言之,每个第二开关s2与一个半导体芯片210串联连接以形成一个开关电路;由多个第二开关s2与多个半导体芯片210组成的多个开关开路呈并联连接。当第二开关s2接受控制元件350产生的一控制信号而进入导通状态时,基础电流i2进入每个半导体芯片210,进行电性测试;此外,第一开关s1耦接于电源供应装置330和半导体芯片210之间,当第一开关s1接受控制元件350提供的一控制信号而进入导通状态时,半导体装置210呈并联连接,第一开关s1串接在电源供应器330和并联连接的多个半导体装置210之间。

[0102]

进一步地,参照图6,当第一开关s1和第二开关s2同时进入导通状态时,附加电流i1和基础电流i2一并流经第二开关s2进入半导体芯片210,进行电性测试;其中,基础电流i2大于附加电流i1。举例来说,附加电流i1可为100毫安培,基础电流i2为200毫安培;换言之,电源供应装置330可提供300毫安培的电流予半导体芯片210,借此启动半导体芯片210。

[0103]

此外,参照图6,信号源320还可以产生编程电压vpp予每个半导体芯片210;当施加编程电压vpp予半导体芯片210,一编程电流i3进入半导体芯片210。编程电流i3可例如为100毫安培。

[0104]

通过前述电路配置,控制元件350能够通过改变第一开关s1和每个第二开关s2的状态,而判断每个半导体芯片210是否能够正常操作。举例来说,在电源供应装置330不提供编程电压vpp予半导体芯片210的情况下,若半导体芯片210依然能够执行写入测试和读取测试,则可判定这个半导体芯片210中的元件和电路毁坏。

[0105]

图7例示本公开实施施的信号源320和受测物件20的功能方框图;图8例示本公开实施施的信号源320和受测物件20的电路图。参照图7和图8,受测物件20包括二半导体芯片群组200_1和200_2,每个半导体芯片群组200_1和200_2可包括多个半导体芯片210;在一些实施方式中,半导体芯片群组200_1和200_2具有相同数量的半导体芯片210。

[0106]

参照图7和图8,信号源320可包括一个电源供应装置330、一开关集合340及一控制元件350。电源供应装置330经配置以产生一附加电压v1、多个基础电压v2_1、v2_2,以及一编程电压vpp;其中编程电压vpp、附加电压v1和基础电压v2_1、v2_2由电源供应装置330的不同输出端传递至开关集合340。

[0107]

参照图7和图8,开关集合340配置在电源供应装置330和半导体芯片群组200_1和200_2之间,并根据控制元件350产生的控制信号而传递编程电压vpp、附加电压v1和基础电压v2_1、v2_2中的至少一者至半导体芯片群组200_1和200_2。具体言之,开关集合340包括一第一开关s1、多个第二开关s2和多个第三开关s3,当第二开关s2进入导通状态时,基础电

流i2通过第一接触垫212a进入半导体芯片210;此外,当第一开关s1进入导通状态时,附加电流i1通过第一接触垫212a进入半导体芯片210。

[0108]

进一步地,当第一开关s1和第二开关s2同时进入导通状态时,附加电流i1和基础电流i2一并流经第二开关s2并经第一接触垫212a进入半导体芯片210,借此启动半导体芯片210。此外,当第三开关s3进入导通状态时,编程电流i3通过一第二接触垫212b进入半导体芯片210。

[0109]

通过前述电路配置,通过改变第一开关s1和每个第二开关s2的状态,而判断每个半导体芯片210是否能够正常操作。举例来说,在电源供应装置320不提供编程电压vpp予半导体芯片210的情况下,若半导体芯片210依然能够执行写入测试和读取测试,则可判定这个半导体芯片210中的元件和电路毁坏。

[0110]

图9例示本公开实施施的信号源320a和受测物件20的功能方框图;图10例示本公开实施施的信号源320a和受测物件20的电路图。参照图9和图10,受测物件20包括二半导体芯片210_1和210_2。

[0111]

信号源320a可包括一个电源供应装置330a、一开关集合340及一控制元件350。电源供应装置330a包括一第一电源供应器330_1、一第二电源供应器330_2及一第三电源供应器330_3,第一电源供应器330_1经配置可以产生一附加电压v1,第二电源供应器330_2经配置以产生二基础器v2_1、v2_2,第三电源供应器330_3经配置以产生一编程电压vpp;开关集合340配置在电源供应装置330a和半导体芯片群组200_1和200_2之间,并接受控制元件350的控制而将电源供应装置330a产生的附加电压v1和基础电压v2_1、v2_2转换成为供应电压vdd_1、vdd_2。

[0112]

参照图9及图10,开关集合340包括一第一开关s1及多个第二开关s2;其中,第二开关s2的数量等于半导体芯片群组200_1和200_2的数量。第二开关s2耦接于电源供应装置330a和半导体芯片210_1和210_2之间。具体言之,每个第二开关s2与一个半导体芯片210_1和210_2串联连接以形成一个开关电路;由多个第二开关s2与多个半导体芯片210_1和210_2组成的多个开关开路呈并联连接。当第二开关s2接受控制元件350产生的一控制信号而进入导通状态时,基础电流i2进入每个半导体芯片210_1和210_2,进行电性测试;此外,第一开关s1耦接于电源供应器340和半导体芯片210_1和210_2之间,当第一开关s1接受控制元件350提供的一控制信号而进入导通状态时,半导体芯片210_1和210_2呈并联连接,第一开关s1串接在电源供应器330a和并联连接的多个半导体芯片210_1和210_2之间。

[0113]

进一步地,当第一开关s1和第二开关s2同时进入导通状态时,附加电流i1和基础电流i2形成一组合电流,一并流经第二开关s2进入半导体芯片210_1和210_2,进行电性测试;其中,基础电流i2大于附加电流i1。举例来说,附加电流i1可为100毫安培,基础电流i2为200毫安培。换言之,电源供应装置330a可提供300毫安培的电流予半导体芯片210,借此启动半导体芯片210。

[0114]

此外,信号源320的第三电源供应器330_3产生编程电压vpp予半导体芯片210_1和210_2;当第三开关s3进入导通状态时,第三电源供应器330_3施加编程电压vpp予半导体芯片210_1和210_2,编程电流i3进入每个半导体芯片群组200_1和200_2,其中编程电流i3可例如为100毫安培。

[0115]

通过前述电路配置,控制元件350能够通过改变第一开关s1和每个第二开关s2的

状态,而判断每个半导体芯片210是否能够正常操作。举例来说,在电源供应装置330a不提供编程电压vpp予半导体芯片210_1和210_2的情况下,若半导体芯片210_1和210_2依然能够执行写入测试和读取测试,则可判定这个半导体芯片210_1和210_2中的元件和电路毁坏。

[0116]

本公开提供一种信号源,用于提供多个供应电压和一编程电压予多个半导体芯片群组。该信号源包括一电源供应装置和一开关集合。电源供应装置经配置以产生一附加电压、多个基础电压及该编程电压;开关集合配置在该电源供应装置与该等半导体芯片群组之间,并用于将该附加电压和该等基础电压转换成为该等供应电压。

[0117]

虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求所定义的本公开的构思与范围。例如,可用不同的方法实施上述的许多工艺,并且以其他工艺或其组合替代上述的许多工艺。

[0118]

再者,本技术案的范围并不受限于说明书中所述的工艺、机械、制造、物质组成物、手段、方法与步骤的特定实施例。本领域技术人员可自本公开的揭示内容理解可根据本公开而使用与本文所述的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的工艺、机械、制造、物质组成物、手段、方法、或步骤。据此,这些工艺、机械、制造、物质组成物、手段、方法、或步骤包含于本技术案的权利要求内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1