表贴式晶振测试装置的制作方法

1.本发明属于晶振检测领域,具体涉及一种表贴式晶振测试装置。

背景技术:

2.社会及科技发展至今,尤其伴随大数据的兴起,各行各业都处于数据量高速增长的阶段。数据量的增长除对存储容量、计算速度提出更高要求外,高速的数据传输也是一项关键要求。高速数据传输不但要求数据的精确性,对传输数据的主要功能模块的开启与关断速度,芯片的唤醒速度都有很高的要求,同时又不能增加过多功耗,芯片保持低功耗设计。高速数据处理电路需要高速参考时钟,参考时钟的精度及起振速度直接影响芯片的唤醒速度及精度。

3.参考时钟可由石英晶体产生,石英晶体可等效高品质电感电容串并联谐振腔,石英晶体配合包含放大器的晶振电路可以构成稳定度很好的时钟生成电路,一般叫做晶体振荡器。石英晶体必须依靠包含放大器的晶振电路来驱动,但是晶振电路设计不合理可能会使得晶振起振速度慢,功耗大,或者具有相位噪声的问题,从而影响了芯片的唤醒速度,增加了芯片唤醒的功耗,降低了芯片处理数据的精度。

4.在目前广泛应用的带定时功能的电路中,一般需要兼具定时和不定时功能,在定时功能时,为保证时间的精准,一般会使用外接32768hz的晶振来提供振荡信号;而在不定时功能下,晶振产生的计时信号不再起作用,在此期间可能会导致晶振停振或损坏,如果不及时更换,就会影响到电路中后续定时功能的使用。这就需要及时检测晶振是否有信号输出。

5.传统的检测晶振是否有信号输出的方法是用示波器的探头接到晶振的输出端上观察是否有波形产生。由于示波器的探头存在十几到二十几pf的电容,如果直接接到晶振上,会使晶振分布电容增大,改变晶振的反馈系数,可能会导致晶振停振。这就需要在探头上夹一个剪短引线的1兆欧以上的电阻,用电阻的另一端接触待测点,这种方法较为繁琐,而且在电路中无法及时判断晶振是否停振。而且随着现代电子科学技术的不断发展与革新,晶振的种类越来越多,封装越来越小,表贴式的晶体振荡器可靠性检测也成了一个问题。

6.因此,现有的晶振检测过程繁琐,无法及时判断晶振是否失效,因而可能导致电路中后续定时功能不能正常使用。

技术实现要素:

7.本发明目的在于提供一种表贴式晶振测试装置,通过设置两个整流模块,可以同时对四个晶振器进行检测,提高检测效率。

8.为了解决现有技术存在的上述问题,本发明所采用的技术方案为:

9.表贴式晶振测试装置,包括电源模块、整形模块和测试座;

10.所述电源模块与整形模块电连接;

11.所述整形模块包括第一整形模块和第二整形模块;

12.所述测试座包括第一测试座、第二测试座、第三测试座和第四测试座;

13.所述第一测试座和第二测试座与第一整形模块连接,所述第三测试座和第四测试座与第二整形模块连接。

14.通过设置两个整形模块,可以同时对多个晶振器进行检测,提高检测效率。

15.进一步的,所述第一整形模块和第二整形模块结构相同,第一整形模块包括六个反相器,第一测试座对应两个反相器,第二测试座对应两个反相器,另外两个反相器闲置,所述反向器的型号为cd4069ube。

16.进一步的,所述测试座用于连接被测元件,测试座再与整形模块连接,通过整形模块给被测元件上电,对晶振器进行检测。

17.进一步的,所述整形模块的输出端为sma端口,用于连接示波器等设备进行检测。

18.本发明的有益效果:本发明可快速复制及批量生产,且不限制于不同频率的晶振,只要采用弹性连接件作为电性能连接的工具,就可以一次多个工位对晶振测试,测试所得结果的精度范围在

±

0.5%以内。有利于提高电路的可靠性,保证了电路后续定时功能的正常运行。

附图说明

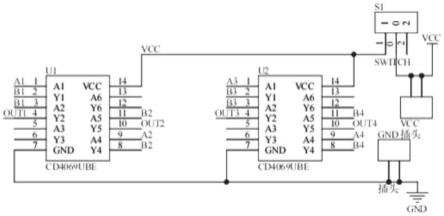

19.图1为本发明中整形模块的电路图。

20.图2为本发明中测试座的电路图。

21.图3为本发明中测试端的电路图。

22.图4为本发明中整形模块的原理图。

具体实施方式

23.下面结合附图及附图标记对本发明作进一步阐述。

24.为了能够更清楚地理解本发明的上述目的、特征和优点,下面结合附图和具体实施例对本发明进行详细描述。需要说明的是,在不冲突的情况下,本技术的实施例及实施例中的特征可以相互组合。

25.术语“第一”、“第二”、“第三”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

26.在本发明的描述中,还需要说明的是,除非另有明确的规定和限定,术语“设置”、“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

27.以下结合附图对本发明的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明,并不用于限制本发明。

28.实施例1:

29.如图1和2所示,表贴式晶振测试装置,包括电源模块、整形模块和测试座。

30.所述电源模块与整形模块电连接。

31.所述整形模块包括第一整形模块和第二整形模块。

32.所述测试座包括第一测试座、第二测试座、第三测试座和第四测试座。

33.所述第一测试座和第二测试座与第一整形模块连接,所述第三测试座和第四测试座与第二整形模块连接。

34.通过设置两个整形模块,可以同时对多个晶振器进行检测,提高检测效率。

35.实施例2:

36.如图1-4所示,表贴式晶振测试装置,包括电源模块、整形模块和测试座。

37.所述电源模块与整形模块电连接。

38.所述整形模块包括第一整形模块和第二整形模块。

39.所述测试座包括第一测试座、第二测试座、第三测试座和第四测试座。

40.所述第一测试座和第二测试座均与第一整形模块连接,所述第三测试座和第四测试座均与第二整形模块连接。

41.通过设置两个整形模块,可以同时对多个晶振器进行检测,提高检测效率。

42.所述第一整形模块和第二整形模块结构相同,第一整形模块包括六个反相器,第一测试座对应两个反相器,第二测试座对应两个反相器,另外两个反相器闲置;第三测试座对应第二整形模块中的两个反相器,第四测试座也对应第二整形模块中的两个反相器,所述反向器的型号为cd4069ube。

43.所述测试座用于连接被测元件(晶振器),测试座与整形模块连接,通过整形模块给被测元件上电,对晶振器进行检测。

44.所述整形模块的输出端为sma端口,用于连接示波器等设备进行检测。

45.具体工作原理:

46.测试装置由晶振起振电路、整形模块、电源模块和检测模块(检测模块为现有技术,此处直接应用)组成。电源连接后,拨动钮子开关,给系统上电,cd4069ube中的非门开始工作,cmos管的vdd端接通高电平,vss接地,晶振的起振模块形成回路,开始产生正弦波形。当输入端的波形从逐渐上升,经过了cmos的电压阈值vt+,其中nmos管导通,pmos管截止,输出端为低电平;当信号电压下降到负触发电压阈值vt-时,pmos管导通,nmos管截止,输出变为高电平。这样就得到了一个周期的粗整形方波,由于在电极性发生反转时会伴随着瞬态电流起始值很大,导致在方波的起始端产生窄脉冲,波形有毛刺,不利于测量,所以在第一个输出端再接一个反相器整形,得到更有利于测试的波形。

47.在测试过程中,应佩戴防静电手环,用镊子将表贴式晶振放置于锁紧座的对应槽内,盖上座子的盖子,以保证晶振的接触性良好,在测试端用sma插头转到频率计或者示波器的bnc端口即可。

48.本发明不局限于上述可选实施方式,任何人在本发明的启示下都可得出其他各种形式的产品,但不论在其形状或结构上作任何变化,凡是落入本发明权利要求界定范围内的技术方案,均落在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1