一种针对射频信号的瞬时频率捕捉器

1.本实用新型属于射频信号捕捉领域,具体涉及一种针对射频信号的瞬时频率捕捉器。

背景技术:

2.在现代电子战和雷达目标模拟领域中,需要对雷达激励信号进行数字存储转发。由于模数转换器件的性能限制,采样带宽小于实际信号带宽。因此,需要利用瞬时测频模块对待转发信号进行瞬时测频,然后通过调谐本振模块,将信号变频至适于ad采样的带宽内。然后才能进行数字存储转发。因此,瞬时测频模块是电子战设备和雷达目标模拟器中不可或缺的。

3.瞬时测频模块通常基于延迟线、变频器、ad采样等数模混合技术,设计难度大,制作工艺复杂。并且,瞬时测频模块的成本体积重量与测频带宽成正相关。当测频带宽较大时,其成本、体积、重量均会有较大幅度的提升。

4.除了上述缺点以外,采用瞬时测频模块还有一个问题。不管是电子战系统,还是转发式雷达目标模拟,其主要作战对象就是雷达。传统雷达激励信号通常是脉组频率捷变的脉冲串。瞬时测频模块对脉组中的第一个脉冲进行瞬时测频,然后调谐本振,使信号落入ad采样带宽内。一般而言,瞬时测频过程需要300ns以上,本振切换及稳定时间大致需要200ns 以上。这样,脉冲信号实际落入ad采样带宽时,已经损失了500ns以上的信号了。对于脉组捷变的雷达体制,在丢失掉首个脉冲信号信息的情况下,只要保证后续脉冲能够有效复制,依旧能够实现欺骗干扰或目标仿真的功能。但是对于脉间捷变的新体制雷达,每个脉冲的频率都是不一样的,此时如果每次测频都要丢失脉冲信息的话,则整个电子战或目标模拟器系统就无法正常工作了。因此,基于瞬时测频模块工作的电子战或目标模拟器,在面对脉间捷变雷达时,是无法有效工作的。这成为了这类设备的一个重大问题。

技术实现要素:

5.本实用新型的目的在于提供一种针对射频信号的瞬时频率捕捉器,能够有效解决采样信号频率突变过程的信号丢失问题。

6.为达到上述目的,本实用新型采用的技术方案为:

7.本实用新型提供一种针对射频信号的瞬时频率捕捉器,包括一次混频模块、数字瞬时测频模块、信号缓存模块和二次混频模块:

8.一次混频模块,用于接收射频收发系统中采样得到的数字信号,并将数字信号转换成i/q信号,i/q信号被复制为ab两路,其中a路i/q信号被送入数字瞬时测频模块,b路i/q信号被送入信号缓存模块;

9.数字瞬时测频模块,用于计算输入的i/q信号的中心频率,并将中心频率作为输出信号送入二次混频模块中,用于产生二次混频的数字本振;

10.信号缓存模块,用于将输入的i/q信号进行可控的延迟,等待针对i/q信号的瞬时

测频和二次混频的数字本振调整完成,避免信号频率突变过程的信号丢失;

11.二次混频模块,通过数字本振将i/q信号中的载波成分去除,使i/q信号转换为基带,再对 i/q信号进行多倍抽取,降低采样率,实现对射频信号的瞬时频率捕捉。

12.所述信号缓存模块包括一个双口ram、一个自增循环计数器和一个减法器,自增循环计数器产生按时钟递增的二进制数,该二进制数的位宽与双口ram地址位宽一致,该二进制数作为双口ram的a端口写地址输入,同时通过一个减法器,该二进制数减去缓存级数,得到双口rma的b端口读地址输入;b路i/q信号经过合并后,送入双口ram的a 端口数据输入,a端口的写入使能始终有效,双口ram的b端口数据输出经过按位分裂后,恢复成i/q信号,b端口的读出使能始终有效,这样b端口的读出数据是a端口写入数据延迟缓存级数时钟的数据,实现了信号缓存,i/q信号经过信号缓存模块缓存后,i/q信号本身不发生变化。

13.相对于现有技术,本实用新型的有益效果为:

14.本实用新型提供的针对射频信号的瞬时频率捕捉器,包括一次混频模块、数字瞬时测频模块、信号缓存模块和二次混频模块,其中一次混频模块、数字瞬时测频模块和二次混频模块均为现有技术,本实用新型在现有技术的基础上新增了信号缓存模块,用于将输入信号进行可控的延迟,等待针对信号的瞬时测频和二次混频的数字本振调整完成,从而避免了信号频率突变过程的信号丢失问题。本实用新型能够在数字域中进行测频、缓存和信号调谐,可以有效解决采样信号频率突变过程的信号丢失问题。

附图说明

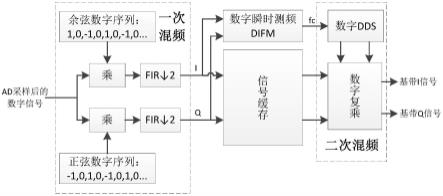

15.图1是本实用新型提供的针对射频信号的瞬时频率捕捉器的基本结构图;

16.图2为本实用新型提供的信号缓存模块的基本结构图。

具体实施方式

17.下面结合附图进一步阐述本实用新型,以下实例仅用于描述本实用新型而不用于限制本实用新型的使用范围,各领域工程技术人员对本实用新型的各种等价变换均包含在本实用新型所要求的权力范围内。

18.本实用新型提供了一种针对射频信号的瞬时频率捕捉器,在现有的瞬时频率捕捉电路 (包括一次混频模块、二次混频模块和数字瞬时测频模块)中增加信号缓存模块,本实用新型的针对射频信号的瞬时频率捕捉器能够在数字域中进行测频、缓存和信号调谐,从而避免了信号丢失的问题,能够对射频信号的瞬时频率进行捕捉。

19.本实用新型提供的针对射频信号的瞬时频率捕捉器的基本结构如图1所示,包括一次混频模块、数字瞬时测频模块、信号缓存模块和二次混频模块。

20.在射频收发系统中,模数转换器件对模拟信号进行数字化采样,形成数字信号,被送入一次混频模块中。

21.ad采样后的数字信号表达式如下:

22.其中n取0、1、2

……

,a(n)表示信号幅度,f表示信号频率, fs表示采样频率,θ(n)表示信号调制信息。

23.1、一次混频模块

24.一次混频模块将该数字信号复制为ab两路。a路信号按时钟序列以此与余弦数字序列 [1,0,-1,0,1,0,-1,0...]相乘,b路信号按时钟序列以此与正弦数字序列[-1,0,1,0,-1,0,1,0...]相乘。利用两个一模一样的数字低通滤波器fir,将ab两路信号的高频部分滤除。然后进行一次2 倍抽取,由此得到了i/q信号。

[0025]

因此,当将序列[1,0,-1,0,1,0,-1,0...]和序列[-1,0,1,0,-1,0,1,0...]分别与原始信号进行相乘后,所得到的新序列,即是原始信号频率下降四分之一采样率和原始信号频率上升四分之一采样率之和。通过一个低通滤波器,可以将原始信号频率上升四分之一采样率的信号滤除掉。

[0026]

最终得到i/q信号如下:

[0027][0028][0029]

考虑到在经过ad采样的实信号,其最高频率小于采样频率的一半(1/2fs)。因此上述i/q信号频率必定小于采样频率的1/4(1/4fs)。因此,采样频率下降一半后(1/2fs),信号频率依旧满足奈奎斯特采样定律。为了降低后续处理压力,在完成滤波后,对信号进行二倍抽取。在实际电路设计时,为了简化电路设计,可以将二倍抽取放置在滤波之前,两者完全等效。

[0030]

一次混频模块输出的i/q信号,再次被复制为ab两路。其中a路i/q信号被送入数字瞬时测频(后续简称difm)模块,b路i/q信号被送入信号缓存模块。

[0031]

2、数字瞬时测频模块

[0032]

数字瞬时测频模块对输入的a路i/q信号进行延迟相关,并将一个脉冲内每个相关结果进行累加,最后对累加结果进行arctan,相位修正,求频率。因为输入信号是一串脉冲,每个脉冲都需要测频,所以在脉冲起始点,应将累加器清零,把上个脉冲的结果清除。对于单点频信号,只需脉冲前沿测频即可达到测频指标,测频时间《200ns。

[0033]

最终difm模块可以根据输入的i/q信号,可以在200纳秒内计算出该信号的中心频率fo。该中心频率作为该模块的输出信号,被送入后续二次混频模块中,用于产生二次混频的数字本振。

[0034][0035]

3、信号缓存模块

[0036]

一次混频模块输出的i/q信号的另一副本信号b路信号,被送入信号缓存模块中。信号缓存模块的基本结构如图2所示。

[0037]

信号缓存模块包括一个双口ram、一个自增循环计数器和一个减法器,自增循环计数器产生按时钟递增的二进制数,该二进制数的位宽与双口ram地址位宽一致,该二进制数作为双口ram的a端口写地址输入,同时通过一个减法器,该二进制数减去缓存级数,得到双口rma的b端口读地址输入。b路i/q信号经过合并后,送入双口ram的a端口数据输入,a端口的写入使能始终有效,双口ram的b端口数据输出经过按位分裂后,恢复成i/q信号,b端口的读出使能始终有效,这样b端口的读出数据是a端口写入数据延迟缓存级数时钟的数据,实现了信号缓存,i/q信号经过信号缓存模块缓存后,i/q信号本身不发生变化。

[0038]

信号缓存模块主要用于将输入的i/q信号进行可控的延迟,等待针对i/q信号的瞬时测频和二次混频的数字本振调整完成,从而避免信号频率突变过程的信号丢失问题。

[0039]

信号缓存模块必须存在的原因(本实用新型的主要创新处)是:瞬时测频需要一定时间;瞬时测频完成后,输出信号频率信息,后续二次混频内部的数字dds在接收到该频率信息后,对数字本振进行调整也需要一定的时间。在这段时间内,当前信号与二次混频的数字本振是不相匹配的。如果没有设计信号缓存电路,直接将一次混频后的信号输入至二次混频,这样在信号频率发生跳变后,在瞬时测频尚未完成或二次混频内部数字dds尚未完成频率调整的这段时间内,数字本振无法将i/q信号混频至基带。在这段时间内,信号实际上是丢失了。有了信号缓存电路后,可以将一次混频输出的i/q信号进行延迟,且延迟时间可以通过缓存级数来调整。因此,一次混频输出的i/q信号,可以在信号缓存电路中延迟到瞬时测频和二次混频的数字dds频率调整完成。这样,经过信号缓存电路的i/q信号可以在时序上与二次混频的数字本振相匹配,从而避免了信号丢失问题。

[0040]

4、二次混频模块

[0041]

一次混频后的i/q信号经过信号缓存模块后,i/q信号本身不会发生变化。

[0042]

同时,difm模块能够测得i/q信号的频率fc[0043][0044]

将fc值取反后,输入二次混频模块中的数字dds模块。数字dds模块是一种业界熟知的,完全公开的数字信号产生模块。一般是根据相位值,在正余弦查找表中查找对应的正余弦值。每个时钟的相位值,可以通过初始相位和信号频率计算所得。

[0045]

找出数字dds模块输出的数字本振信号,将输入的i/q信号与数字本振信号进行复数相乘,这样即将信号中的载波成分去除,信号转换为了基带。后续信号处理可以通过多倍抽取,转换为较低的采样率进行处理。即可实现对射频信号的瞬时频率进行捕捉。

[0046]

本实用新型提供的针对射频信号的瞬时频率捕捉器的具体电路结构,其具体实现方式包括但不限于下述四种:

[0047]

1.利用fpga等可编程逻辑芯片,将电路烧写至该芯片中,实现电路功能。

[0048]

2.按照asic设计开发流程,将电路设计成集成电路,并流片生产。

[0049]

3.采用基础逻辑元器件,在pcb电路板上搭建电路。

[0050]

4.综合采取上述三种方法。

[0051]

上述方法均为业界所熟知的,无需赘述的电路实现方式。

[0052]

以上所述,仅是本实用新型的较佳实施例,并非对本实用新型作任何限制,凡是根据本实用新型技术实质对以上实施例所作的任何简单修改、变更以及等效结构变换,均仍属于本实用新型技术方案的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1