一种可扩展多只晶振自动测试电路的制作方法

1.本实用新型涉及电子设备检测技术领域,特别是涉及一种可扩展多只晶振自动测试电路。

背景技术:

2.晶体振荡器是指从一块石英晶体上按一定方位角切下晶片,添加lc组成振荡电路的晶体元件;其产品一般用金属外壳封装。其作用主要包括:

3.1.通用晶体振荡器,用于各种电路中,产生振荡频率。

4.2.时钟脉冲用石英晶体谐振器,与其它元件配合产生标准脉冲信号,广泛用于数字电路中。

5.3.微处理器用石英晶体谐振器。

6.晶体振荡器的主要参数包括频率准确度、温度稳定度,频率调节范围,调频特性、负载特性、电压特性等。

7.在晶体振荡器的设计和生产过程中,需要对晶体振荡器的参数进行检测。

8.目前,市场上针对晶振的测试夹具只能单只测试,由于电子产品往往生产量很大,采用单只测试方式比较花费人力,测试成本较高,效率低下。

9.因此,现有技术的缺陷是,缺少一种可扩展多只晶振自动测试电路,采用自动测试方式对多只晶振进行测试,节约测试成本,并可以提高对测试设备的使用率。

技术实现要素:

10.有鉴于现有技术的至少一个缺陷,本实用新型的目的是提供一种可扩展多只晶振自动测试电路,采用自动测试方式对多只晶振进行批量测试,节约测试成本,并可以提高对测试设备的使用率。

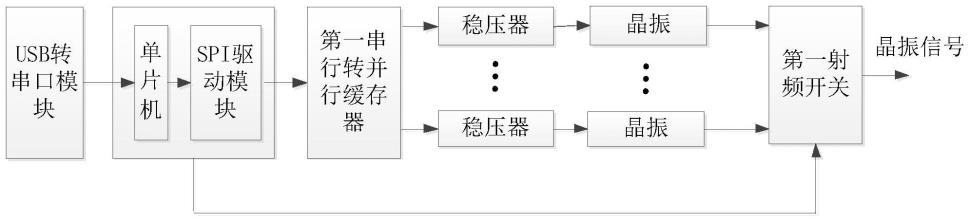

11.为了达到上述目的,本实用新型采用如下技术方案:一种可扩展多只晶振自动测试电路,包括usb转串口模块、控制模块、第一串行转并行缓存器、第一射频开关以及至少两个稳压器,每个稳压器均连接有晶振为晶振供电,usb转串口模块用于获取上位机的选通指令发送给控制模块,控制模块输出串行选通数据给第一串行转并行缓存器,第一串行转并行缓存器输出并行选通数据选择稳压器为相应的晶振供电,所有晶振的信号输出端通过第一射频开关输出信号,控制模块连接第一射频开关控制其选通相应的晶振信号。

12.所述控制模块或者是单片机,或者是单片机通过spi串行接口连接有spi 驱动模块;单片机根据usb转串口模块的串口数据转换成spi串行数据。

13.所述单片机的串行输入端组连接usb转串口模块,单片机的spi串行接口连接有spi驱动模块,单片机经spi驱动模块连接第一串行转并行缓存器输出 spi串行选通数据;单片机还经spi驱动模块连接第一射频开关的选择端组控制其选通相应的晶振信号。

14.所述spi驱动模块连接第一串行转并行缓存器的串行数据输入端组,第一串行转并行缓存器的并行输出端组连接稳压器的使能端,晶振的信号输出端依次连接第一射频开

关的相应信号输入端,第一射频开关的信号输出端输出相应的晶振信号。

15.所述晶振、稳压器为16只,所述第一串行转并行缓存器采用74hc595d模块,第一串行转并行缓存器为两只,第一射频开关采用hmc241alp3e模块,第一射频开关为1只,还包括四个第二射频开关,第二射频开关采用hmc241alp3e模块,16只晶振的16个输出端依次连接四个第二射频开关的输入端,四个第二射频开关的输出端连接第一射频开关的四个输入端;

16.单片机经spi驱动模块连接有第二串行转并行缓存器,第二串行转并行缓存器采用74hc595d模块,第二串行转并行缓存器的八个信号输出端依次连接四个第二射频开关的选择端组控制其选通相应的晶振信号。

17.显著效果:本实用新型提供了一种一种可扩展多只晶振自动测试电路,采用自动测试方式对多只晶振进行批量测试,节约测试成本,并可以提高对测试设备的使用率。

附图说明

18.图1为本实用新型的结构图;

19.图2为16只晶振自动测试电路的电路图;

20.图3为1-4只晶振及其稳压器的电路图;其中,(a)为第1只晶振及其稳压器的电路图,(b)为第2只晶振及其稳压器的电路图,(c)为第3只晶振及其稳压器的电路图,(d)为第4只晶振及其稳压器的电路图;

21.图4为5-8只晶振及其稳压器的电路图;其中,(a)为第5只晶振及其稳压器的电路图,(b)为第6只晶振及其稳压器的电路图,(c)为第7只晶振及其稳压器的电路图,(d)为第8只晶振及其稳压器的电路图;

22.图5为9-12只晶振及其稳压器的电路图;其中,(a)为第9只晶振及其稳压器的电路图,(b)为第10只晶振及其稳压器的电路图,(c)为第11只晶振及其稳压器的电路图,(d)为第12只晶振及其稳压器的电路图;

23.图6为13-16只晶振及其稳压器的电路图;其中,(a)为第13只晶振及其稳压器的电路图,(b)为第14只晶振及其稳压器的电路图,(c)为第15只晶振及其稳压器的电路图,(d)为第16只晶振及其稳压器的电路图;

24.图7为第一串行转并行缓存器和第二串行转并行缓存器的电路图,其中, (a)、(b)分别为两个第一串行转并行缓存器的电路图;(c)为第二串行转并行缓存器的电路图;(d)为第一串行转并行缓存器、第二串行转并行缓存器、第一射频开关、第二射频开关的电源模块的电路图;(e)为j2接口的电路图;

25.图8为第二射频开关和第一射频开关的电路图;其中(a)、(b)、(c)、(d) 为第二射频开关的电路图,(e)为第一射频开关的电路图;

26.图9为单片机及其供电模块的电路图;其中,(a)为单片机的电路图,(b) 为供电模块的电路图,(c)为单片机接口j2的电路图;

27.图10为usb转串口模块的电路图;其中,(a)为usb转串口芯片的电路图, (b)为usb指示灯的电路图;

28.图11为三个spi驱动模块及其输出接口的电路图;其中,(a)为第一个spi 驱动模块的电路图,(b)为第二个spi驱动模块的电路图,(c)为第三个spi 驱动模块的电路图,(d)

为spi驱动模块输出接口的电路图。

具体实施方式

29.下面结合附图和具体实施例对本实用新型作进一步详细说明。

30.本实用新型涉及一种可扩展多只晶振自动测试电路。特指通过单片机将串行数据转换为并行数据,控制电路中的各个稳压块和微波射频开关,实现多个待测晶振的自动测试。

31.本发明解决其技术问题所采用的技术方案是:采用usb为控制接口,控制方式为串口通信协议,利用计算机软件发指令给电路中的单片机,单片机输出串行指令,通过串行转并行电路,选择不同的晶振,从而达到一次测试16只甚至更多晶振的目的。

32.本发明的有益效果是,能较好的满足批量晶振的测试需要,并且电路结构简单,并可根据不同的要求对电路进行扩展,测试效率搞,成本低,实现大规模自动测试。

33.如图1-图11所示,一种可扩展多只晶振自动测试电路,包括usb转串口模块、控制模块、第一串行转并行缓存器、第一射频开关以及至少两个稳压器,每个稳压器均连接有晶振为晶振供电,usb转串口模块用于获取上位机的选通指令发送给控制模块,控制模块输出串行选通数据给第一串行转并行缓存器,第一串行转并行缓存器输出并行选通数据选择稳压器为相应的晶振供电,所有晶振的信号输出端通过第一射频开关输出信号,控制模块连接第一射频开关控制其选通相应的晶振信号。

34.稳压器为多个,比如2个、4个、8个、16个等,每个稳压器均连接有晶振为晶振供电。如图3-图6所示,稳压器为16个,如u1、u5、u9、u13等,连接有16 个晶振,如u3、u7、u11、u15等。

35.usb转串口模块用于获取上位机的选通指令发送给控制模块,其中usb转串口模块采用ch9326g模块,比如,上位机的选通指令为1号晶振u3,控制模块输出串行选通数据给第一串行转并行缓存器,比如“00000001”,第一串行转并行缓存器输出并行选通数据,比如q7-q0为“00000001”,q0为高电平,通过 control11输出高电平,控制稳压器u1为1号晶振u3供电,1号晶振u3输出脉冲信号,经第一射频开关输出1号晶振信号给测试设备,对1号晶振的参数进行检测。

36.同理,又可以通过第一串行转并行缓存器控制稳压器u5给2号晶振u7供电, 2号晶振u7输出脉冲信号,经第一射频开关输出2号晶振信号给测试设备,对2号晶振的参数进行检测。

37.所述控制模块或者是单片机,或者是单片机通过spi串行接口连接有spi 驱动模块;单片机根据usb转串口模块的串口数据转换成spi串行数据,spi驱动模块是为spi串行数据提供稳定的驱动能力。由于单片机的负载能力有限,为了提高单片机的驱动能力,单片机连接有spi驱动模块。

38.单片机的功能是把usb转串口模块输入的串行数据转换成自定义的spi串行控制数据。可根据不同的spi串行控制数据要求对spi数据进行定制,不会因为电脑升级更新后没有并口,导致产品测试电脑不能升级更新,提高了产品的测试效率,更提高了产品测试夹具的适应性。

39.如图9所示,单片机采用pic16lf1936单片机,如图11所示,spi驱动模块采用

74hc573d模块。

40.所述单片机的串行输入端组18脚和19脚连接usb转串口模块的txd、rxd,单片机的spi串行接口ra0、ra1、rb0连接有spi驱动模块,控制模块经spi 驱动模块连接第一串行转并行缓存器t6的11、14、12脚输出spi串行选通数据;第一串行转并行缓存器t6的q7-q0输出并行控制数据给稳压器,控制模块还经spi驱动模块的control9、control10连接第一射频开关t1的选择端组8 脚、7脚控制其选通相应的晶振信号。

41.所述spi驱动模块连接第一串行转并行缓存器的串行数据输入端组,第一串行转并行缓存器的并行输出端组q7-q0连接稳压器的使能端en,晶振的信号输出端依次连接第一射频开关t1的相应信号输入端,第一射频开关t1的信号输出端输出相应的晶振信号。

42.稳压器采用tps73801dcqr稳压模块,其具有使能端en,控制其vout端输出信号。

43.所述晶振、稳压器为16只,所述第一串行转并行缓存器采用74hc595d模块,第一串行转并行缓存器为两只,第一射频开关采用hmc241alp3e模块,第一射频开关为1只,还包括四个第二射频开关,第二射频开关采用hmc241alp3e模块, 16只晶振的16个输出端依次连接四个第二射频开关的输入端,四个第二射频开关的输出端连接第一射频开关的四个输入端;

44.单片机经spi驱动模块连接有第二串行转并行缓存器,第二串行转并行缓存器采用74hc595d模块,第二串行转并行缓存器的八个信号输出端依次连接四个第二射频开关的选择端组控制其选通相应的晶振信号。

45.四个第二射频开关分别是第二射频开关t2、第二射频开关t3、第二射频开关t4、第二射频开关t5。

46.上述电路为16只晶振的自动测试电路,由于具有16只晶振,一只74hc595d 模块只以输出8位并行选通数据,需要对电路进行扩展,所以需要两只74hc595d 模块组合形成16选1的并行选通数据,第一射频开关采用hmc241alp3e模块只有4 个信号输入端,只能连接4个输入信号,因此,增加了四个第二射频开关,每个第二射频开关连接四只晶振,形成四选1结构,再经过第一射频开关选择一路晶振信号输出。

47.每个第二射频开关均设置有两个选择端组a、b,因此共有8个选择端组,单片机仍然输出8位spi串行数据,经spi驱动模块扩展其驱动能力,然后输出给第二串行转并行缓存器,第二串行转并行缓存器的输出端组q7-q0依次连接四个第二射频开关的选择端组,控制四个第二射频开关只有一个输出晶振信号。单片机再经spi驱动模块输出选择信号给第一射频开关t1的选择端组a、b,选择四个第二射频开关其中的一个输出晶振信号给测试设备,其中测试设备属于现有技术,不再赘述。

48.第一串行转并行缓存器t6、第一串行转并行缓存器t7、第二串行转并行缓存器t8的clk、data共用74hc573d模块u2的q1和q2端,单片机通过rb0、ra2、 ra4端输出片选信号给cs1、cs2、cs3,从而选择第一串行转并行缓存器t6、第一串行转并行缓存器t7、第二串行转并行缓存器t8,向其输出选通控制数据。单片机通过ra5、ra7输出信号,经74hc573d模块u2的q6、q7输出选择数据给第一射频开关t1的选择端组a、b,使其选择其中一个第二射频开关的信号输出。

49.当选择1号晶振u3时,稳压器u1通电,其余稳压器均不通电,第二射频开关 t2通过其a和b两个选择端选择out1从out17输出,其余三个第二射频开关不输出信号,第一射频开

关t1通过其a和b两个选择端选择out17输入,从j1输出晶振信号到测试设备,以此类推,上述选择受单片机输出信号控制。

50.附图11中,spi驱动模块共有三只74hc573d模块。其中,74hc573d模块的 io8、io10-io20为预留控制端,通过其能继续扩大检测晶振的数量。

51.为了方便测试晶振,每一个晶振均设置有插槽,插槽设置有5个顶针,通过 5个顶针连接晶振的5个接线端,5个顶针与稳压器和第二射频开关连接,方便测试时装拆晶振,为现有成熟技术,图略。

52.计算机usb发出指令后,经过u3后将usb发出的指令转化为串口数据。串口数据经ic1校验后,把正确的数据发送给各个io口。参见图4,控制数据发给各个74hc595d模块,经过译码器把控制数据转变为74hc595d模块的q0~q7 引脚的高低电平。参见图3和图4,通过74hc595d模块的q0~q7控制各个稳压块,射频开关从而达到16路晶振选择一路的目的。整个电路结构合理,成本较低,扩展性强,电路运行可靠,使用安全。

53.为了降低晶振测试成本,增加测试设备的利用率。本发明提供了一种可扩展多只晶振自动测试电路,可满足16个晶振一次测试的需求,并根据实际需要,可扩展为至少96只晶振自动测试的电路。

54.最后,需要注意的是:以上列举的仅是本实用新型的具体实施例子,当然本领域的技术人员可以对本实用新型进行改动和变型,倘若这些修改和变型属于本实用新型权利要求及其等同技术的范围之内,均应认为是本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1