一种半导体器件的ESD测试系统的制作方法

本技术涉及半导体可靠性测试中的静电可靠性测试领域,特别是一种半导体器件的esd测试系统。

背景技术:

1、根据静电的产生方式以及对电路的损伤模式不同通常分为四种测试方式:人体放电模式(hbm:human-body model)、机器放电模式(machine model)、元件充电模式(cdm:charge-device model)、电场感应模式(fim:field-induced model),但是业界通常使用前两种模式来测试(hbm,mm)。在半导体器件的esd测试中,因为每个chip的pin脚很多,为了降低测试周期,一般会会分为几种组合: i/o-pin测试(input and output pins)、pin-to-pin测试、vdd-vss测试(输入端到输出端)。在测试过程中,通常都是给各分组的管脚打3次电压。任意管脚之间都会发生静电放电现象,若每只管脚都测试,成本太高。故在实际测试过程中,业界标准会把它简化成如图1电路。

2、此种方法存在以下几个方面不足。

3、1、此种方法因不同规格的半导体器件管脚数目及类型各不相同无法适用不同规格的半导体器件。实验时若更换器件进行esd测试,需要重新搭建电路,普遍适用性较低。

4、2、此种方法无法适用于管脚数目较多的半导体器件,在实际应用中,半导体器件的管脚数目越多,esd测试时所需要连接的导线越多,导线之间越易产生电磁干扰,接头越多甚至会导致相邻接头产生短路的情况发生,影响测试结果的判定。

技术实现思路

1、针对传统esd测试技术面对不同类型半导体器件需要重新搭建测试电路的问题,本实用新型提供一种半导体器件的esd测试系统,克服传统esd测试方法对于不同规格的元器件需要进行重新组建电路费时费力以及针对对管脚数目多的半导体器件进行测试时易造成接脚间短路的问题,通过控制组输出的高低电平信号实现对测试电路的控制,达到控制管脚浮空或导通的目的。

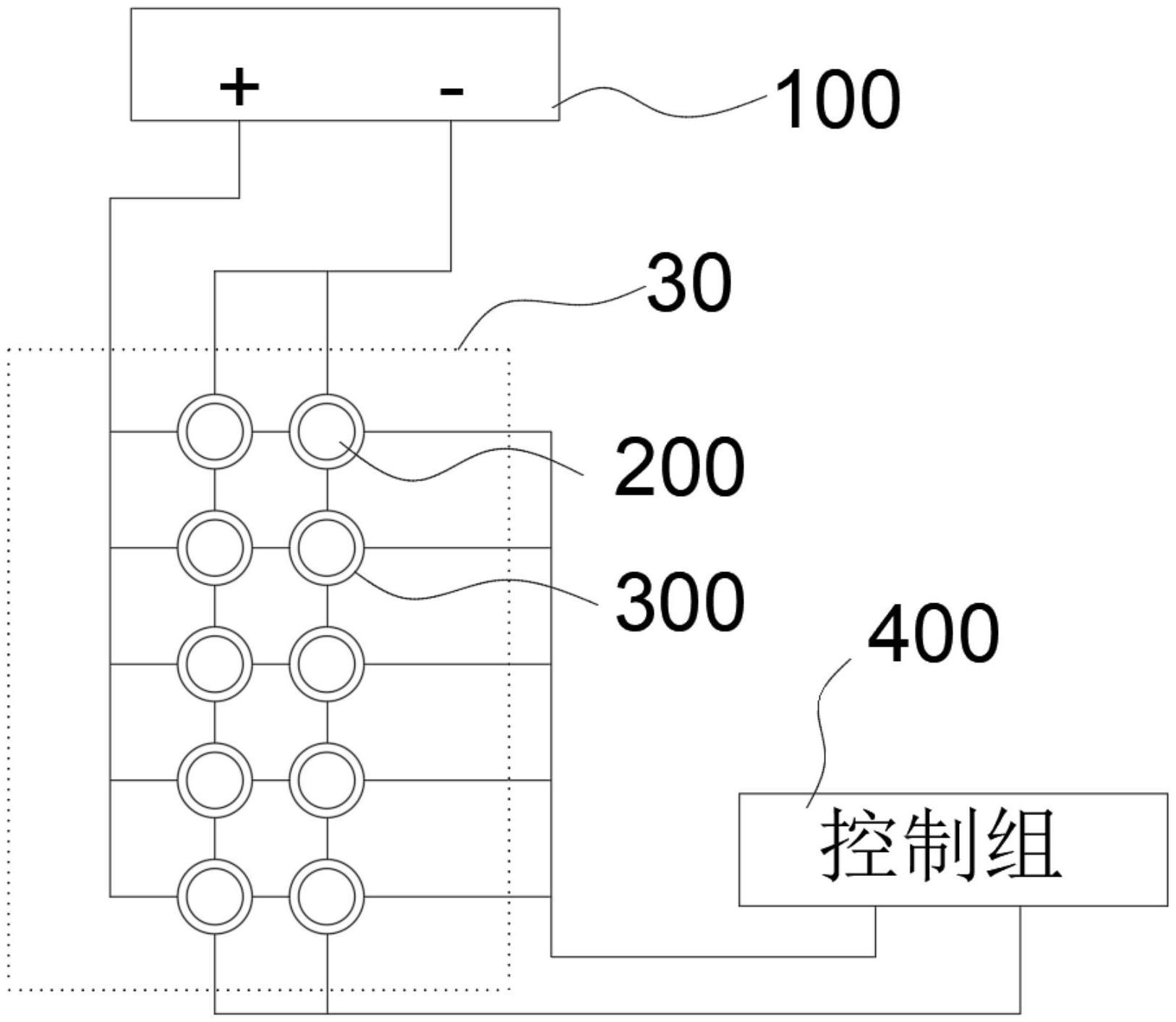

2、为实现上述目的,本实用新型选用如下技术方案:一种半导体器件的esd测试系统,包括静电发生组和被测管脚端,还包括测试电路,所述测试电路具有继电器和逻辑门电路,所述继电器的一触点端与所述静电发生组的静电释放端连接,另一触点端与所述被测管脚端连接,所述逻辑门电路与所述继电器的信号控制端电性连接以使所述继电器根据所述逻辑门电路的输出信号控制所述静电发生组和所述被测管脚端之间的导通或浮空。

3、优选地,还包括控制组,所述控制组具有至少2路输出分别所述逻辑门电路的输入端电性连接。

4、优选地,所述逻辑门电路为与门电路,所述控制组具有第一路输出和第二路输出,分别接入与门电路的两输入端,所述与门电路的输出端与所述继电器的信号控制端连接。

5、优选地,所述被测管脚端具有多个,对应所述被测管脚端设有多个测试电路组成矩阵测试电路组,各个测试电路的逻辑门电路输入端分别电性连接所述控制组的至少2路输出。

6、优选地,所述控制组的各路输出为用于向逻辑门电路的输入端输入高电平信号或低电平信号。

7、另一方面,本实用新型选用如下技术方案:一种半导体器件的esd测试方法,应用上述的一种半导体器件的esd测试系统,包括以下步骤:

8、按照被测管脚端的管脚类型设置需要进行esd测试的管脚,且将静电发生组的正负端接入被测管脚端,设置进行测试的参数后开始测试;

9、通过控制组的各路输出向测试电路的逻辑门电路输入高电平信号或低电平信号,经过逻辑门电路的运算输出信号控制继电器的导通状态或断路状态;

10、测试电路根据继电器的导通状态或断路状态进而控制静电发生组和被测管脚端的管脚测试导通或测试浮空。

11、优选地,还包括以下步骤:

12、在管脚数目较多的半导体器件测试时,设置多个被测管脚端且分别接入所述控制组的各路输出,并将管脚按照测试要求设置在被测管脚端;

13、由所述控制组对应被测管脚端上的管脚为应测试导通或应测试浮空进行控制各路输出,向逻辑门电路的输入端输出高电平信号或低电平信号,进而控制各测试电路的导通或断路,使得静电发生组和被测管脚端根据继电器的导通状态或断路状态实现多个管脚按照预先设定地测试导通或测试浮空。

14、优选地,所述逻辑门电路为与门电路,当控制组的一路输出为高电平信号和另一路输出为低电平信号时,所述测试电路的继电器信号控制端接收与门电路的输出信号为低电平信号,继电器处于断路状态;当控制组的各路输出为高电平信号时,所述测试电路的继电器信号控制端接收与门电路的输出信号为高电平信号,继电器处于导通状态。

15、优选地,所述控制组根据各管脚的应测试导通或应测试浮空设置好各路输出;

16、应测试导通的与门电路的输入端皆为高电平信号,该与门电路输出高电平信号控制继电器导通,静电发生组的静电释放端和被测管脚端的连接导通,该管脚处于导通测试状态;

17、应测试浮空的与门电路的至少一个输入端为低电平信号,该与门电路输出低电平信号控制继电器断路,静电发生组的静电释放端与被管脚端的连接断开,该管脚处于浮空不接入测试电路状态;

18、将各路输出根据信号输出情况组成需要的矩阵电路,所述矩阵电路的各横列路和纵列路用于输出相同的高电平信号或低电平信号。

19、另一方面,本实用新型选用如下技术方案:一种半导体器件的esd测试控制装置,包括存储器和处理器,所述处理器通过调用所述存储器中存储的控制程序,以执行如上述的一种半导体器件的esd测试方法。

20、相较于现有技术,本实用新型具有以下有益效果:

21、本实用新型为了克服传统esd测试方法对于不同规格的元器件需要进行重新组建电路费时费力以及针对对管脚数目多的半导体器件进行测试时易造成接脚间短路的问题,通过控制组的各路输出控制高低电平信号输出,进而对测试电路的控制,从而实现静电发生组和被测管脚端之间的导通和断开,达到控制管脚浮空或导通的目的,弥补了传统esd测试技术人工控制费时费力的缺陷,增强了整体系统的可控性,降低了测试成本。

22、本实用新型的多个测试电路根据控制组的各路输出还可以组成矩阵测试电路组,矩阵的存在使测试电路板可以根据需要制作不同规格大小的电路板,由此本实用新型可适用于任何管脚数目和任何类型的半导体器件,弥补了传统esd测试技术面对不同类型半导体器件需要重新搭建测试电路的不足,增强了系统的普遍适用性。

技术特征:

1.一种半导体器件的esd测试系统,包括静电发生组和被测管脚端,其特征在于:还包括测试电路,所述测试电路具有继电器和逻辑门电路,所述继电器的一触点端与所述静电发生组的静电释放端连接,另一触点端与所述被测管脚端连接,所述逻辑门电路与所述继电器的信号控制端电性连接以使所述继电器根据所述逻辑门电路的输出信号控制所述静电发生组和所述被测管脚端之间的导通或浮空。

2.根据权利要求1所述的一种半导体器件的esd测试系统,其特征在于:还包括控制组,所述控制组具有至少2路输出分别所述逻辑门电路的输入端电性连接。

3.根据权利要求2所述的一种半导体器件的esd测试系统,其特征在于:所述逻辑门电路为与门电路,所述控制组具有第一路输出和第二路输出,分别接入与门电路的两输入端,所述与门电路的输出端与所述继电器的信号控制端连接。

4.根据权利要求2所述的一种半导体器件的esd测试系统,其特征在于:所述被测管脚端具有多个,对应所述被测管脚端设有多个测试电路组成矩阵测试电路组,各个测试电路的逻辑门电路输入端分别电性连接所述控制组的至少2路输出。

5.根据权利要求3或4所述的一种半导体器件的esd测试系统,其特征在于:所述控制组的各路输出为用于向逻辑门电路的输入端输入高电平信号或低电平信号。

技术总结

一种半导体器件的ESD测试系统,包括静电发生组和被测管脚端,还包括测试电路,所述测试电路具有继电器和逻辑门电路,所述继电器的一触点端与所述静电发生组的静电释放端连接,另一触点端与所述被测管脚端连接,所述逻辑门电路与所述继电器的信号控制端电性连接以使所述继电器根据所述逻辑门电路的输出信号控制所述静电发生组和所述被测管脚端之间的导通或浮空。本技术通过控制组的各路输出控制高低电平信号输出,进而对测试电路的控制,从而实现静电发生组和被测管脚端之间的导通和断开,达到控制管脚浮空或导通的目的,弥补了传统ESD测试技术人工控制费时费力的缺陷,增强了整体系统的可控性,降低了测试成本。

技术研发人员:张程,徐世明,周海,王伊纳,廖志鹏

受保护的技术使用者:珠海格力新元电子有限公司

技术研发日:20221010

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!