用于减轻永久磁铁阵列的杂散场的屏蔽策略的制作方法

本公开涉及检验系统,且更具体来说涉及利用电子束及永久磁铁阵列的检验系统。

背景技术:

1、半导体制造工业的演化对良率管理且具体来说对计量及检验系统提出越来越高的要求。临界尺寸继续缩小,但行业需要减少达到高良率、高价值生产的时间。最小化从检测到良率问题到解决这个问题的总时间确定半导体制造商的投资回报率。

2、制造半导体装置(例如逻辑及存储器装置)通常包含使用大量制造工艺处理半导体晶片或euv掩模以形成半导体装置的各种特征及多个层级。例如,光刻是涉及将图案从倍缩式掩模转印到布置在半导体晶片上的光致蚀刻剂的半导体制造工艺。半导体制造工艺的额外实例包含但不限于化学机械抛光(cmp)、蚀刻、沉积及离子植入。多个半导体装置可被制造成单个半导体晶片上的一个布置,其被分成个别半导体装置。

3、在半导体制造期间的各个步骤使用检验工艺来检测晶片上的缺陷,以促进制造工艺中的较高良率及因此较高利润。检验始终是制造半导体装置(例如集成电路(ic))的重要部分。然而,随着半导体装置的尺寸减小,检验对于可接受半导体装置的成功制造变得甚至更为重要,因为较小缺陷可能引起装置故障。例如,随着半导体装置的尺寸减小,具有减小大小的缺陷的检测已变得有必要,因为甚至相对较小缺陷仍可引起半导体装置中的非所要像差。

4、一种用于检验工艺的装置是多柱系统。在多柱系统中,产生数百个小射束(beamlet)并将其聚焦到目标上。每一小射束经引导通过包括上部及下部永久磁铁的光学柱。然而,永久磁铁产生引起射束偏转的杂散场。射束偏转导致不良射束对准,且降低检验工艺的准确度。

5、因此,需要一种用于减轻多射束系统中的杂散场的方法。

技术实现思路

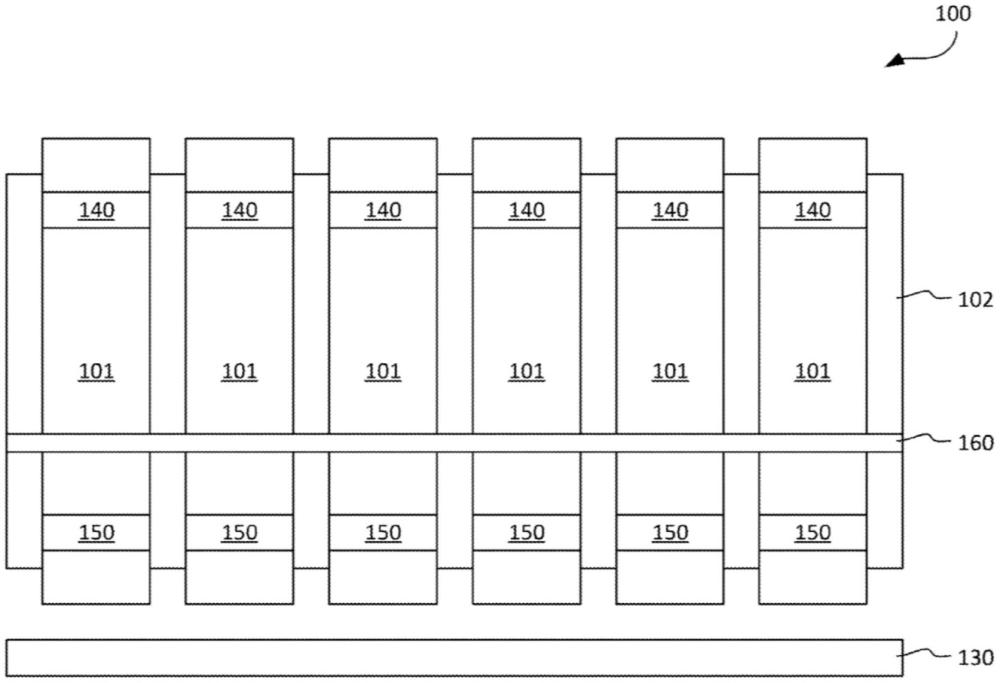

1、本公开的实施例提供一种检验系统。所述检验系统包括电子束柱阵列,所述电子束柱各自包括经配置以朝向载物台发射电子的电子源。所述检验系统进一步包括经配置以将来自每一电子源的电子会聚成电子束阵列的第一永久磁铁阵列。所述第一永久磁铁阵列布置在所述电子束柱阵列的第一端处。所述检验系统进一步包括在所述第一永久磁铁阵列下游在电子发射的方向上跨越所述电子束柱阵列延伸的多个屏蔽板。所述多个屏蔽板各自包括多个孔隙且具有介于1μm与1mm之间的厚度,且所述电子束阵列穿过所述多个孔隙。所述多个屏蔽板减少在所述电子束阵列的径向方向上的杂散磁场。

2、根据本公开的实施例,所述检验系统可进一步包括经配置以将所述电子束阵列聚焦朝向所述载物台上的目标的第二永久磁铁阵列。所述第二永久磁铁阵列布置在所述电子束柱阵列的第二端处。

3、根据本公开的实施例,所述多个屏蔽板包括靠近所述第一永久磁铁阵列布置的第一屏蔽板,及靠近所述第二永久磁铁阵列布置的第二屏蔽板。

4、根据本公开的实施例,所述检验系统进一步包括经配置以检测从所述目标反射的电子的检测器。所述检测器布置在所述第一永久磁铁阵列与所述第二永久磁铁阵列之间。所述多个屏蔽板进一步包括靠近所述检测器布置的第三屏蔽板。

5、根据本公开的实施例,所述多个屏蔽板进一步包括靠近所述检测器、与所述第三屏蔽板相对布置的第四屏蔽板。

6、根据本公开的实施例,所述多个屏蔽板进一步包括布置在所述第一屏蔽板与所述第二屏蔽板之间的至少一个补充屏蔽板。

7、根据本公开的实施例,所述多个屏蔽板包括至少七个屏蔽板。

8、根据本公开的实施例,所述多个屏蔽板中的至少一者布置在所述杂散磁场在所述电子束阵列的所述径向方向上处于最高量值之处。

9、根据本公开的实施例,所述多个屏蔽板中的每一者的所述厚度是至少120μm。

10、根据本公开的实施例,所述多个屏蔽板包括磁性镍铁合金。

11、本公开的实施例提供一种应用于多柱检验系统的杂散场减轻的方法。所述检验系统包含电子束柱阵列,每一电子束柱包括经配置以朝向载物台发射电子的电子束源。所述方法包括将来自每一电子源的电子引导通过第一永久磁铁阵列以将所述电子会聚成电子束阵列。所述第一永久磁铁阵列布置在所述电子束柱阵列的第一端处。所述方法进一步包括将所述电子束阵列引导通过在所述第一永久磁铁阵列下游跨越所述电子束柱阵列延伸的多个屏蔽板。所述多个屏蔽板各自包括多个孔隙且具有介于1μm与1mm之间的厚度,且所述电子束阵列穿过所述多个孔隙。所述多个屏蔽板减少在所述电子束阵列的径向方向上的杂散磁场。

12、根据本公开的实施例,所述方法进一步包括将所述电子束阵列引导通过第二永久磁铁阵列以将所述电子束阵列聚焦朝向所述载物台上的目标。所述第二永久磁铁阵列布置在所述电子束柱阵列的第二端处,在所述多个屏蔽板下游。

13、根据本公开的实施例,将所述电子束阵列引导通过多个屏蔽板包括:将所述电子束阵列引导通过靠近所述第一永久磁铁阵列布置的第一屏蔽板,及将所述电子束阵列引导通过靠近所述第二永久磁铁阵列布置的第二屏蔽板。

14、根据本公开的实施例,所述方法进一步包括将所述电子束阵列引导通过经配置以检测从所述目标反射的电子的检测器。所述检测器布置在所述第一永久磁铁阵列与所述第二永久磁铁阵列之间。将所述电子束阵列引导通过多个屏蔽板进一步包括:将所述电子束阵列引导通过靠近所述检测器布置的第三屏蔽板。

15、根据本公开的实施例,将所述电子束阵列引导通过多个屏蔽板进一步包括:将所述电子束阵列引导通过靠近所述检测器、与所述第三屏蔽板相对布置的第四屏蔽板。

16、根据本公开的实施例,将所述电子束阵列引导通过多个屏蔽板进一步包括:将所述电子束阵列引导通过布置在所述第一屏蔽板与所述第二屏蔽板之间的至少一个补充屏蔽板。

技术特征:

1.一种检验系统,其包括:

2.根据权利要求1所述的检验系统,其进一步包括:

3.根据权利要求2所述的检验系统,其中所述多个屏蔽板包括:

4.根据权利要求3所述的检验系统,其进一步包括:

5.根据权利要求4所述的检验系统,其中所述多个屏蔽板进一步包括:

6.根据权利要求5所述的检验系统,其中所述多个屏蔽板进一步包括:

7.根据权利要求1所述的检验系统,其中所述多个屏蔽板包括至少七个屏蔽板。

8.根据权利要求1所述的检验系统,其中所述多个屏蔽板中的至少一者布置在所述杂散磁场在所述电子束阵列的所述径向方向上处于最高量值之处。

9.根据权利要求1所述的检验系统,其中所述多个屏蔽板中的每一者的所述厚度是至少120μm。

10.根据权利要求1所述的检验系统,其中所述多个屏蔽板由磁性镍铁合金构成。

11.一种应用于多柱检验系统的杂散场减轻的方法,所述多柱检验系统包含电子束柱阵列,每一电子束柱包括经配置以朝向载物台发射电子的电子束源,所述方法包括:

12.根据权利要求11所述的方法,其进一步包括:

13.根据权利要求12所述的方法,其中将所述电子束阵列引导通过多个屏蔽板包括:

14.根据权利要求13所述的方法,其进一步包括:

15.根据权利要求14所述的方法,其中将所述电子束阵列引导通过多个屏蔽板进一步包括:

16.根据权利要求15所述的方法,其中将所述电子束阵列引导通过多个屏蔽板进一步包括:

17.根据权利要求11所述的方法,其中所述多个屏蔽板包括至少七个屏蔽板。

18.根据权利要求11所述的方法,其中所述多个屏蔽板中的至少一者布置在所述杂散磁场在所述电子束阵列的所述径向方向上处于最高量值之处。

19.根据权利要求11所述的方法,其中所述多个屏蔽板中的每一者的所述厚度是至少120μm。

20.根据权利要求11所述的方法,其中所述多个屏蔽板由磁性镍铁合金构成。

技术总结

本公开提供一种检验系统及一种杂散场减轻的方法。所述系统包含电子束柱阵列、第一永久磁铁阵列及多个屏蔽板。所述电子束柱阵列各自包含经配置以朝向载物台发射电子的电子源。所述第一永久磁铁阵列经配置以将来自每一电子源的所述电子会聚成电子束阵列。所述第一永久磁铁阵列布置在所述电子束柱阵列的第一端处。所述多个屏蔽板在所述第一永久磁铁阵列下游在电子发射的方向上跨越所述阵列电子束柱延伸。所述电子束阵列穿过所述多个屏蔽板中的每一者中的多个孔隙,这减少在所述电子束阵列的径向方向上的杂散磁场。

技术研发人员:张乾,W·济伟·罗,J·毛里诺,T·普勒特纳

受保护的技术使用者:科磊股份有限公司

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!