芯片测试装置及测试方法与流程

本发明涉及半导体,特别涉及一种芯片测试装置及测试方法。

背景技术:

1、目前,在芯片的抽样测试,例如芯片验证测试、芯片可靠性测试和芯片特性测试,需要手动操作,例如,在测试结束时,需要手动从测试机台中取出芯片,但在取出芯片的过程中,无法区分测试机台是否完全断电,如在测试机台未完全断电的情况下将芯片取出,或者因操作不当或误操作未及时从测试机台中取出芯片造成芯片重复测试,从而造成芯片损坏,甚至会损坏测试机台。

技术实现思路

1、本发明的目的在于提供一种芯片测试装置及测试方法,以在芯片测试时避免损坏芯片或者测试机台。

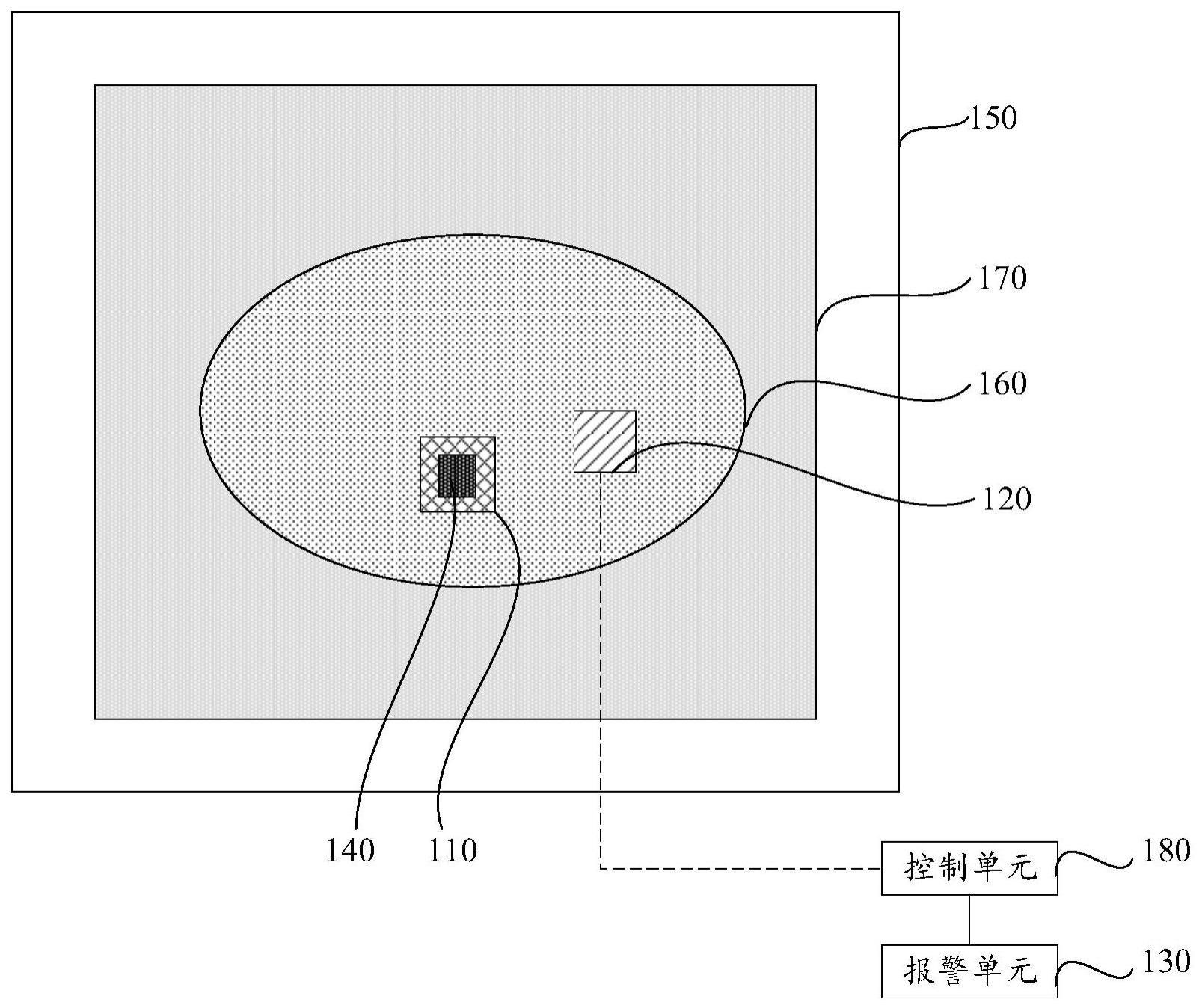

2、为实现上述目的,本发明提供一种芯片测试装置,包括:光控开关单元、计时单元和报警单元,所述光控开关单元与所述计时单元信号连接,所述计时单元与所述报警单元信号连接;

3、所述光控开关单元用于在芯片的测试结束时控制测试机台的电源断开;

4、所述计时单元用于在所述芯片的测试结束时记录所述芯片的测试时间;

5、所述报警单元用于在所述芯片的测试时间小于或者大于预设测试时间时发出报警。

6、可选的,在所述的芯片测试装置中,所述芯片测试装置还包括测试夹具,所述测试夹具具有一密闭的容置空间,所述芯片、所述光控开关单元和所述计时单元均置于所述容置空间内。

7、可选的,在所述的芯片测试装置中,所述光控开关单元还用于在所述芯片的测试开始时控制测试机台的电源导通。

8、可选的,在所述的芯片测试装置中,所述光控开关单元通过感应所述容置空间内的光强变化来控制所述测试机台的电源断开或者导通,其中,在所述芯片的测试结束时所述测试夹具处于开启状态,以及在所述芯片的测试开始时所述测试夹具处于关闭状态,所述测试夹具处于开启状态时的容置空间内的光强与所述测试夹具处于关闭状态时的容置空间内的光强不同。

9、可选的,在所述的芯片测试装置中,所述芯片测试装置还包括控制单元,所述控制单元在所述测试夹具外与所述计时单元信号连接,所述计时单元将所述芯片的测试时间提供至所述控制单元,所述控制单元在所述芯片的测试时间小于预设测试时间时向所述报警单元发送报警信息,所述报警单元根据所述报警信息发出报警。

10、可选的,在所述的芯片测试装置中,所述报警单元为蜂鸣器或者发光二极管。

11、基于同一发明构思,本发明还提供一种芯片测试方法,包括:

12、通过光控开关单元在芯片的测试结束时控制测试机台的电源断开;

13、通过计时单元在所述芯片的测试结束时记录所述芯片的测试时间;

14、判断所述芯片的测试时间是否小于或者大于预设测试时间,若是,则报警单元发出报警。

15、可选的,在所述的芯片测试方法中,所述光控开关单元还用于在所述芯片的测试开始时控制测试机台的电源导通。

16、可选的,在所述的芯片测试方法中,所述光控开关单元通过感应所述容置空间内的光强变化来控制所述测试机台的电源断开或者导通,其中,在所述芯片的测试结束时所述测试夹具处于开启状态,以及在所述芯片的测试开始时所述测试夹具处于关闭状态,所述测试夹具处于开启状态时的容置空间内的光强与所述测试夹具处于关闭状态时的容置空间内的光强不同。

17、在本发明提供的芯片测试装置及测试方法中,通过光控开关单元在芯片的测试结束时控制测试机台的电源断开,如此,可以在芯片测试结束时,及时的使测试机台的电源断开,由此避免在测试机台未断电的情况下取出芯片,从而避免损伤芯片或者机台。以及,通过计时单元在芯片的测试结束时记录芯片的测试时间,并通过报警单元在芯片的测试时间小于或者大于预设测试时间时发出报警,如此,在芯片的测试时间未达到预设测试时间或者超出预设时间时能够及时提醒,从而能够及时发现异常,避免损坏芯片或者测试机台,提高了芯片和机台的安全稳定性。

技术特征:

1.一种芯片测试装置,其特征在于,包括:光控开关单元、计时单元和报警单元,所述光控开关单元与所述计时单元信号连接,所述计时单元与所述报警单元信号连接;

2.如权利要求1所述的芯片测试装置,其特征在于,所述芯片测试装置还包括测试夹具,所述测试夹具具有可密闭的容置空间,所述芯片、所述光控开关单元和所述计时单元均置于所述容置空间内。

3.如权利要求2所述的芯片测试装置,其特征在于,所述光控开关单元还用于在所述芯片的测试开始时控制测试机台的电源导通。

4.如权利要求3所述的芯片测试装置,其特征在于,所述光控开关单元通过感应所述容置空间内的光强变化来控制所述测试机台的电源断开或者导通,其中,在所述芯片的测试结束时所述测试夹具处于开启状态,以及在所述芯片的测试开始时所述测试夹具处于关闭状态,所述测试夹具处于开启状态时的容置空间内的光强与所述测试夹具处于关闭状态时的容置空间内的光强不同。

5.如权利要求1所述的芯片测试装置,其特征在于,所述芯片测试装置还包括控制单元,所述控制单元在所述测试夹具外与所述计时单元信号连接,在测试结束时,所述计时单元将所述芯片的测试时间提供至所述控制单元,所述控制单元在所述芯片的测试时间小于预设测试时间时向所述报警单元发送报警信息,所述报警单元根据所述报警信息发出报警。

6.如权利要求1所述的芯片测试装置,其特征在于,所述报警单元为蜂鸣器或者发光二极管。

7.如权利要求1~6中任一项所述的芯片测试装置,其特征在于,所述测试机台为芯片最终测试机台,所述芯片为快闪存储器。

8.一种芯片测试方法,其特征在于,包括:

9.如权利要求8所述的芯片测试方法,其特征在于,所述光控开关单元还用于在所述芯片的测试开始时控制测试机台的电源导通。

10.如权利要求9所述的芯片测试方法,其特征在于,所述光控开关单元通过感应所述容置空间内的光强变化来控制所述测试机台的电源断开或者导通,其中,在所述芯片的测试结束时所述测试夹具处于开启状态,以及在所述芯片的测试开始时所述测试夹具处于关闭状态,所述测试夹具处于开启状态时的容置空间内的光强与所述测试夹具处于关闭状态时的容置空间内的光强不同。

技术总结

本发明提供一种芯片测试装置及测试方法,通过光控开关单元在芯片的测试结束时控制测试机台的电源断开,如此,可以在芯片测试结束时,及时的使测试机台的电源断开,由此避免在测试机台未断电的情况下取出芯片,从而避免损伤芯片或者机台。以及,通过计时单元在芯片的测试结束时记录芯片的测试时间,并通过报警单元在芯片的测试时间小于或者大于预设测试时间时发出报警,如此,在芯片的测试时间未达到预设测试时间或者超出预设时间时能够及时提醒,从而能够及时发现异常,避免损坏芯片或者测试机台,提高了芯片和机台的安全稳定性。

技术研发人员:朱倩,鲍小燕,周俊,傅秀菲

受保护的技术使用者:上海华岭集成电路技术股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!