多颗粒封装芯片的阻抗校准装置和方法

本技术属于芯片校准,尤其涉及一种多颗粒封装芯片的阻抗校准装置和方法。

背景技术:

1、多颗粒封装芯片由多个芯片颗粒组成,每一个芯片颗粒都配置有一个作为该芯片颗粒(简称颗粒)的物理接口的高速收发驱动接口电路(以下简称驱动电路)。

2、颗粒的驱动电路通常需要满足相关标准规定的阻抗匹配要求,即,驱动电路在工作时表现出的外部阻抗,应当和相关标准中规定的标准阻抗相匹配。

3、受芯片加工时的过程、电压和温度(process、voltage、temperature,pvt)等因素影响,驱动电路的外部阻抗可能出现较大波动,以致于驱动电路的外部阻抗和标准阻抗不匹配,因此,需要对多颗粒封装芯片中各颗粒的驱动电路进行阻抗校准。

4、阻抗校准需要用到片外校准电阻。现有阻抗校准方案中,多个驱动电路共享一个片外校准电阻。因此校准过程中同一时间只能校准一个颗粒的驱动电路,即,先校准一个颗粒的驱动电路,该颗粒的驱动电路校准结束后再开始校准下一个颗粒的驱动电路,以此类推。

5、这种校准方法导致多颗粒封装芯片的阻抗校准用时较长。

技术实现思路

1、为此,本技术公开如下技术方案:

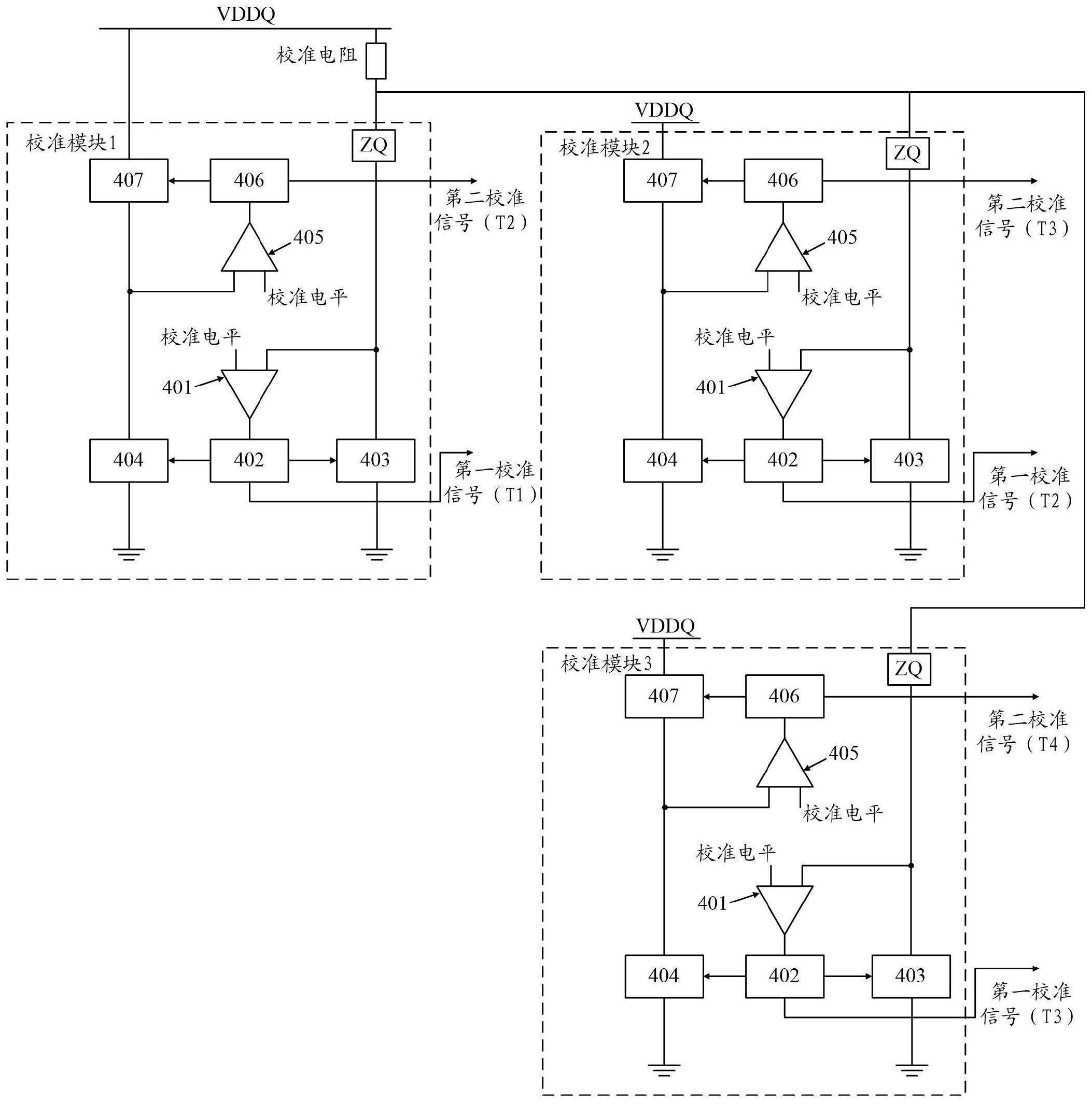

2、本技术第一方面提供一种多颗粒封装芯片的阻抗校准装置,包括校准电阻和多个校准模块,所述校准电阻和所述多个校准模块连接,多个所述校准模块和多颗粒封装芯片中多个芯片颗粒的驱动电路一一对应;

3、所述校准模块包括,利用所述校准电阻校准对应驱动电路的第一校准单元,以及在所述第一校准单元结束校准后,利用所述第一校准单元校准对应驱动电路的第二校准单元;

4、当多个所述校准模块逐一用于校准对应的所述驱动电路时,除首个所述校准模块以外,每一所述校准模块的所述第一校准单元,均在前一校准模块的所述第一校准单元结束校准之后,所述第二校准单元结束校准之前开始校准。

5、可选的,所述阻抗校准装置还包括和所述校准模块一一对应的多个控制模块;

6、所述控制模块用于控制所述校准模块的第一校准单元和第二校准单元进行校准。

7、可选的,所述控制模块控制所述校准模块的第一校准单元和第二校准单元进行校准时,具体用于:

8、若所述控制模块对应于首个所述校准模块,所述控制模块在获得开始校准信号后,控制首个所述校准模块的第一校准单元和第二校准单元依次进行校准;

9、若所述控制模块对应于除首个所述校准模块以外的校准模块,所述控制模块在获得前一校准模块的第一结束信号后,控制对应的校准模块的第一校准单元和第二校准单元依次进行校准;其中,所述第一结束信号表征所述前一校准模块的第一校准单元结束校准;

10、在对应的所述校准模块的所述第一校准单元结束校准后,向后一校准模块输出第一结束信号。

11、可选的,所述第一校准单元包括第一比较器,第一计数器,第一校准电路和复制电路;

12、所述复制电路具有和所述第一校准电路相同的电路结构,所述第一校准电路具有和第一驱动电路相同的电路结构,所述第一驱动电路指代所述驱动电路中被所述第一校准单元校准的驱动电路;

13、所述第一校准电路和所述校准电阻串联;

14、所述第一比较器的一个输入端接入校准电平,所述第一比较器的另一个输入端接入所述第一校准电路和所述校准电阻的公共端;

15、所述第一比较器的输出端和所述第一计数器连接;

16、所述第一计数器用于:

17、根据所述第一比较器的比较结果,输出用于调整第一目标阻抗的第一校准信号,直至所述第一目标阻抗和所述校准电阻的阻值满足预设的第一数量关系为止;其中,所述第一目标阻抗指代所述第一驱动电路、所述第一校准电路和所述复制电路的阻抗;

18、所述复制电路用于在所述第一校准单元结束校准后,作为同一校准模块的第二校准单元校准时的依据。

19、可选的,所述第二校准单元包括第二比较器,第二计数器和第二校准电路;

20、所述第二校准电路具有和第二驱动电路相同的电路结构,所述第二驱动电路指代所述驱动电路中被所述第二校准单元校准的驱动电路;

21、所述第二校准电路和同一校准模块的所述第一校准单元的复制电路串联;

22、所述第二比较器的一个输入端接入校准电平,所述第二比较器的另一个输入端接入所述第二校准电路和所述复制电路的公共端;

23、所述第二比较器的输出端和所述第二计数器连接;

24、所述第二计数器用于:

25、根据所述第二比较器的比较结果输出用于调整第二目标阻抗的第二校准信号,直至所述第二目标阻抗和所述校准电阻的阻值满足预设的第二数量关系为止;其中,所述第二目标阻抗指代所述第二驱动电路和所述第二校准电路的阻抗。

26、可选的,所述第一驱动电路为下拉驱动电路,所述第二驱动电路为上拉驱动电路;

27、或者,所述第一驱动电路为上拉驱动电路,所述第二驱动电路为下拉驱动电路。

28、可选的,所述第一数量关系为:

29、所述第一目标阻抗和所述校准电阻的阻值相等,或者,所述第一目标阻抗和所述校准电阻的阻值的比值为预设的第一比值;

30、所述第二数量关系为:

31、所述第二目标阻抗和所述校准电阻的阻值相等,或者,所述第二目标阻抗和所述校准电阻的阻值的比值为预设的第二比值。

32、可选的,所述第一计数器根据所述第一比较器的比较结果,输出用于调整第一目标阻抗的第一校准信号时,具体用于:

33、根据所述第一比较器的比较结果和预设的校准算法,输出用于调整第一目标阻抗的第一校准信号;

34、所述第二计数器根据所述第二比较器的比较结果输出用于调整第二目标阻抗的第二校准信号时,具体用于:

35、根据所述第二比较器的比较结果和预设的校准算法,输出用于调整第二目标阻抗的第二校准信号。

36、可选的,所述每一所述校准模块的所述第一校准单元,均在前一校准模块的所述第一校准单元结束校准之后,所述第二校准单元结束校准之前开始校准,包括:

37、当预设的校准模式为第一校准模式时,每一所述校准模块的所述第一校准单元,均在前一校准模块的所述第一校准单元结束校准之后,所述第二校准单元结束校准之前开始校准;

38、当所述校准模式为第二校准模式时,每一所述校准模块的所述第一校准单元,均在前一所述校准模块的所述第二校准单元结束校准之后开始校准。

39、本技术第二方面提供一种多颗粒封装芯片的阻抗校准方法,应用于本技术第一方面任意一项所提供的多颗粒封装芯片的阻抗校准装置,所述方法包括:

40、利用多个校准模块逐一校准对应的驱动电路,直至每一驱动电路均被校准为止;

41、其中,除首个所述校准模块以外,每一所述校准模块的所述第一校准单元,均在前一校准模块的所述第一校准单元结束校准之后,所述第二校准单元结束校准之前开始校准。

42、本技术公开一种多颗粒封装芯片的阻抗校准装置和方法,包括校准电阻和多个校准模块,校准电阻和多个校准模块连接,多个校准模块和多颗粒封装芯片中多个芯片颗粒一一对应;校准模块包括,利用校准电阻校准对应芯片颗粒的第一校准单元;在第一校准单元结束校准后,利用第一校准单元校准对应芯片颗粒的第二校准单元;当多个校准模块逐一用于校准对应的芯片颗粒时,除首个以外的每一校准模块的第一校准单元,均在前一校准模块的第一校准单元结束校准之后,第二校准单元结束校准之前开始校准。该装置校准多颗粒封装芯片时,不同校准模块之间第一校准单元和第二校准单元可以同时校准对应的芯片颗粒。所以本方案能缩短多颗粒封装芯片的阻抗校准用时。

- 还没有人留言评论。精彩留言会获得点赞!