一种3DNADA闪存垂直通道的超薄电镜样品及其制样方法与流程

本发明涉及检测分析制样,尤其涉及一种3dnada闪存垂直通道的超薄电镜样品及其制样方法。

背景技术:

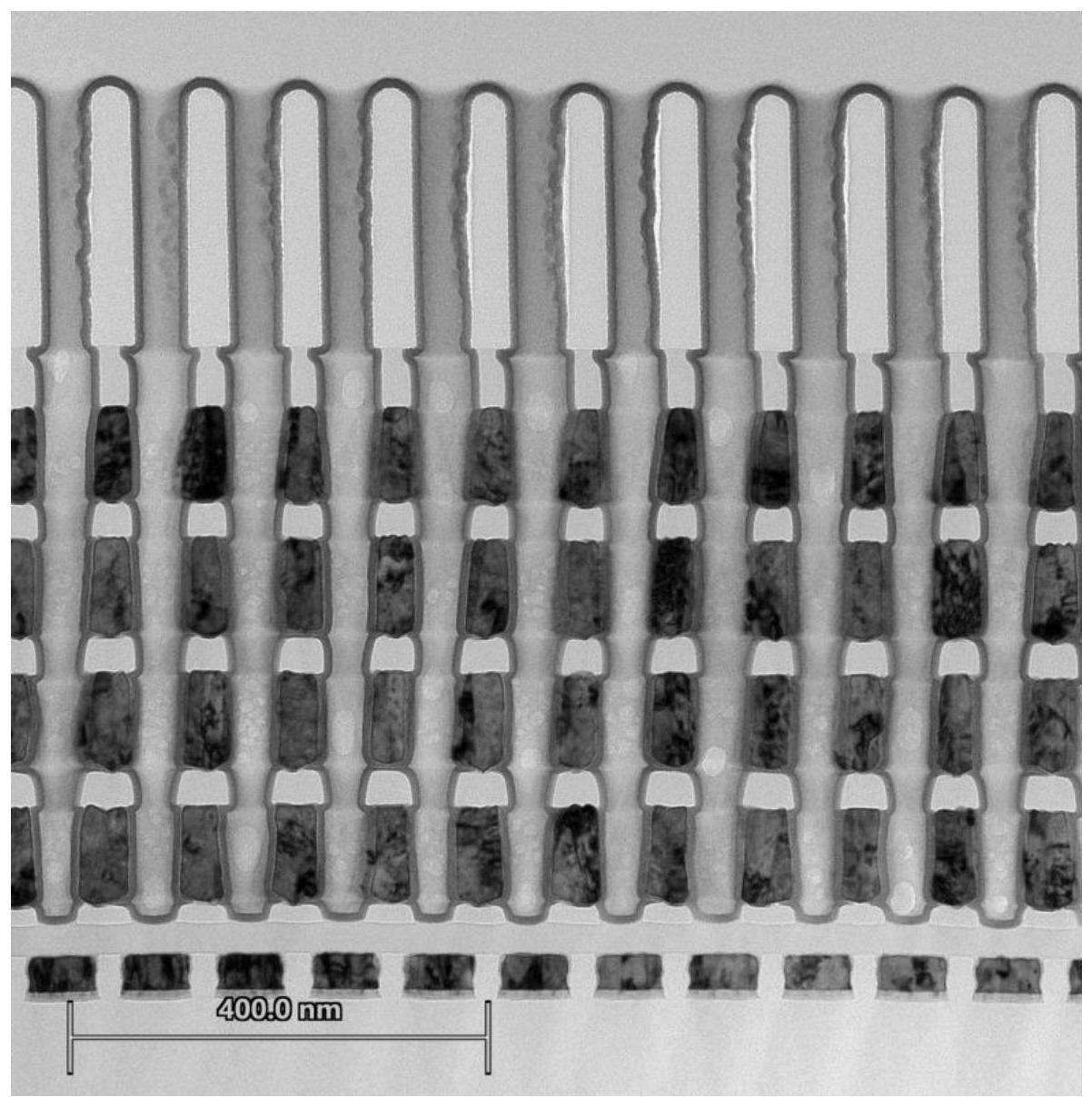

1、3dnand闪存垂直孔(3dnada flash vertical channel)在生产过程中,在多层金属钨中刻蚀垂直孔,产品研发和生产工艺均需要监控孔径、孔内侧残留、金属钨(w)与金属间氧化层的界面变化。相比于金属w的硬度,填充的胶极软,目前现有方法在制备此类样品中容易在硬度差异界面产生切割刀痕。最先进的制程工艺已要求此类垂直孔直径小于30nm,因此在制备分析样品时,制备的电镜(tem)截面样品必须小于30nm。当无法避免刀痕,样品会先产生空洞,刀痕破坏结构,无法达到制备目标。

2、在现有技术中,有人提出在用聚焦离子束(fib)制备电镜样品时采用倒切技术的方法,即离子束切割与目标结构平行,但是为反向切割。其主要针对浅沟槽隔离结构的制造方法,即开槽上大下小的样品,但是无法满足大深宽比样品的制备。例如,3dnand闪存垂直孔就是为大的深宽比,且孔的上下宽度几乎无差异,采用倒切技术也难以制得超薄电镜样品。

3、其中另一个重要问题为,由于刻蚀速率的差异,w金属层刻蚀后,w与上下层sio2界面细微的空隙需要体现,传统的直接填胶技术无法很好的表征此类缺陷。

4、因此,需要开发新的制样方法来弥补现有技术中的缺陷。

技术实现思路

1、鉴于现有技术中存在的问题,本发明提供一种3dnada闪存垂直通道的超薄电镜样品及其制样方法,尤其是超薄透射电镜样品及其制样方法,所述制样方法能够制得无划痕和空洞的电镜样品,且针对深宽比高的样品也能将电镜样品的尺寸做到30nm以下,解决了此类器件的检测难题。

2、为达此目的,本发明采用以下技术方案:

3、第一方面,本发明提供一种3dnada闪存垂直通道的超薄电镜样品的制样方法,所述制样方法包括:所述3dnada闪存垂直通道向第一方向倾斜至与水平面呈a角度后,再经聚焦离子束进行切割,得到第一样品;所述第一样品向第二方向倾斜至与水平面呈b角度后,再经聚焦离子束进行抛光,得到超薄电镜样品;

4、所述第一方向和第二方向属于平行且相反的方向。

5、本发明提供的制样方法可以对3dnand闪存垂直孔这样大深宽比样品进行聚焦离子束电镜超薄样品的制备,可以实现消除刀痕,获得高质量的超薄3dnand闪存垂直孔电镜分析样品,样品厚度可以降低至30nm以下,提升了质量和成功率。

6、优选地,所述a角度和所述b角度各自独立地为15~20°,例如可以是15°、15.6°、16.2°、16.7°、17.3°、17.8°、18.4°、18.9°、19.5°或20°等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

7、由于倾斜的角度对于最终是否有刀痕和空洞较为关键,当倾斜的角度过大时,存在抛光深度过大以及尖角造成的刀痕问题,当倾斜的角度过小时,难以消除刀痕和空洞,因此本发明优选将倾斜的角度控制在15~20°的范围内,显著提高了电镜样品的制样成功率。

8、优选地,所述a角度和b角度的数值相当。切割和抛光的工艺更简单且在后续能够更快的消除刀痕和空洞。

9、优选地,所述3dnada闪存垂直通道的深宽比为20~30,例如可以是20、21、22、23、24、25、26、27、28、29或30等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

10、正是由于本发明中3dnada闪存垂直通道样品的特殊性,其垂直孔的直径较小,导致深宽比较大,一般而言≥20的深宽比导致采用常规切割技术极易出现刀痕和空洞,然而采用本发明提供的制样方法后能够较好地消除刀痕和空洞,提高样品的制样成功率。

11、优选地,所述超薄电镜样品的厚度≤30nm,例如可以是20nm、22nm、23nm、24nm、25nm、26nm、27nm、28nm、29nm或30nm等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

12、本发明制得的样品的厚度可下降至30nm以内,能够较好地观察3dnada闪存垂直通道。

13、优选地,所述切割直至3dnada闪存垂直通道剩余一排垂直孔。

14、优选地,所述切割包括依次进行的第一切割、第二切割和第三切割。

15、本发明进一步优选将切割分为三步切割进行,通过采用下述不同的离子束参数,更有利于提高制样成功率。

16、优选地,所述第一切割的离子束参数为25~30kv以及0.75~10na,例如可以是25kv、27kv、28kv、29kv或30kv等,例如可以是0.75na、1.78na、2.81na、3.84na、4.87na、5.89na、6.92na、7.95na、8.98na或10na等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

17、优选地,所述第一切割直至剩余三排垂直孔。

18、优选地,所述第二切割的离子束参数为15~20kv以及50~80pa,例如可以是15kv、16kv、17kv、17kv、18kv、18kv、19kv、19kv、20kv或20kv等,例如可以是50pa、54pa、57pa、60pa、64pa、67pa、70pa、74pa、77pa或80pa等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

19、优选地,所述第二切割直至剩余最后一排垂直孔。

20、优选地,所述第三切割的离子束参数为6~10kv以及50~80pa,例如可以是6kv、6.5kv、6.9kv、7.4kv、7.8kv、8.3kv、8.7kv、9.2kv、9.6kv或10kv等,例如可以是50pa、54pa、57pa、60pa、64pa、67pa、70pa、74pa、77pa或80pa等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

21、优选地,所述第三切割直至切割到最后一排垂直孔的边缘。

22、优选地,所述边缘占所述最后一排垂直孔的宽度的0.05~0.13,例如可以是0.05、0.06、0.07、0.08、0.09、0.1、0.11、0.12、0.13或0.13等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

23、优选地,所述抛光包括第一抛光和第二抛光。

24、本发明优选将抛光分两步进行,其中第一抛光用于进一步削薄最后一排垂直孔,得到厚度≤30nm的样品,第二抛光用于去除垂直孔的表面非晶层,使其在透射电镜成像时衬度清晰,具有受表层非晶损伤层影响更小等优势。

25、优选地,所述第一抛光的离子束参数为3~5kv以及20~30pa,例如可以是3kv、3.3kv、3.5kv、3.7kv、3.9kv、4.2kv、4.4kv、4.6kv、4.8kv或5kv等,例如可以是20pa、22pa、23pa、24pa、25pa、26pa、27pa、28pa、29pa或30pa等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

26、优选地,所述第一抛光直至3dnada闪存垂直通道的厚度≤30nm,例如可以是20nm、22nm、23nm、24nm、25nm、26nm、27nm、28nm、29nm或30nm等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

27、优选地,所述第二抛光的离子束参数为1~2.5kv以及15~25pa,例如可以是1kv、1.2kv、1.4kv、1.5kv、1.7kv、1.9kv、2kv、2.2kv、2.4kv或2.5kv等,例如可以是15pa、16.2pa、17.3pa、18.4pa、19.5pa、20.6pa、21.7pa、22.8pa、23.9pa或25pa等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

28、优选地,所述第二抛光消除垂直孔的表面非晶层。

29、优选地,所述制样方法包括:

30、在所述3dnada闪存垂直通道向第一方向倾斜至与水平面呈a角度之前,先在所述3dnada闪存垂直通道的垂直孔内依次填充有保护层和填充胶。

31、由于3dnada闪存垂直通道分为上层器件层和下层氧化硅层,上层器件层的材质一般为钨金属,如果钨金属与氧化硅之间是否具有细微的空隙或者连接良好,一般希望在进行电镜表征的时候体现出来此类缺陷,本发明采用先填充保护层的方式,这层保护层能够填充金属w与sio2因刻蚀导致的空隙,从而使其在电镜检测时体现出钨金属与氧化硅的连接关系。

32、优选地,所述保护层通过沉积得到。

33、优选地,所述沉积包括原子层沉积。

34、优选地,所述原子层沉积的速度为0.10~0.20nm/cycle,例如可以是0.10nm/cycle、0.12nm/cycle、0.13nm/cycle、0.14nm/cycle、0.15nm/cycle、0.16nm/cycle、0.17nm/cycle、0.18nm/cycle、0.19nm/cycle或0.20nm/cycle等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

35、优选地,所述原子层沉积的温度≤65℃,例如可以是65℃、64℃、63℃、62℃、60℃、58℃、55℃或50℃等。

36、优选地,所述保护层的材质包括氧化铪和/或氧化锆。

37、本发明优选保护层的材质为氧化铪,其与钨金属能够更好地相容,相比于氧化铜、氧化铁等金属而言具有沉积温度低,膜层性质稳定等优势,同时在工艺环节后续的工序也是沉积hfo2,方便比对刻蚀效果。

38、本发明当保护层的材质为氧化铪时,采用的沉积气源包括铪源和氧源;其中所述铪源包括四(二甲铵基)铪,所述氧源包括水。当沉积hfo2时铪源瓶的加热温度为80-90℃,例如可以是80℃、81℃、82℃、85℃、87℃、88℃或90℃等;铪源的通入时间为55-65ms/cycle,例如可以是55ms/cycle、56ms/cycle、57ms/cycle、58ms/cycle、59ms/cycle、60ms/cycle、61ms/cycle、62ms/cycle、63ms/cycle、64ms/cycle或65ms/cycle;铪源的通入流量为3.5-4.5mg/cycle,例如可以是3.5mg/cycle、3.6mg/cycle、3.7mg/cycle、3.8mg/cycle、3.9mg/cycle、4.0mg/cycle、4.1mg/cycle、4.2mg/cycle、4.3mg/cycle、4.4mg/cycle或4.5mg/cycle等;氧源的通入时间为55-65ms/cycle,例如可以是55ms/cycle、56ms/cycle、57ms/cycle、58ms/cycle、59ms/cycle、60ms/cycle、61ms/cycle、62ms/cycle、63ms/cycle、64ms/cycle或65ms/cycle等;氧源的通入流量为3.5-4.5mg/cycle,例如可以是3.5mg/cycle、3.6mg/cycle、3.7mg/cycle、3.8mg/cycle、3.9mg/cycle、4.0mg/cycle、4.1mg/cycle、4.2mg/cycle、4.3mg/cycle、4.4mg/cycle或4.5mg/cycle等;氮气的通入流量为8-12sccm,例如可以是8sccm、8.5sccm、9sccm、9.5sccm、10sccm、10.5sccm、11sccm、11.5sccm或12sccm等。

39、优选地,所述保护层的厚度为5~10nm,例如可以是5nm、6nm、7nm、8nm、9nm、或10nm等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

40、优选地,所述填充胶包括环氧树脂。

41、优选地,所述环氧树脂包括m-bond-610。

42、优选地,所述填充胶的填充方法包括:将流动态的填充胶加入至设有保护层的垂直孔内,再进行固化。

43、优选地,所述固化的温度为45~55℃,例如可以是45℃、47℃、48℃、49℃、50℃、51℃、52℃、53℃、54℃或55℃等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

44、优选地,所述固化的时间为1.5~4h,例如可以是1.5h、1.8h、2.1h、2.4h、2.7h、2.9h、3.2h、3.5h、3.8h或4h等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

45、优选地,所述填充胶固化之后的硬度≥邵d80,例如可以是邵d80、邵d81、邵d82、邵d85、邵d90、邵d92或邵d95等。

46、值得说明的是,该填充胶固化之后的硬度较为关键,在切割和抛光的过程中,离子束同时对填充胶和3dnada闪存垂直通道进行切割和抛光,填充胶固化之后的硬度与倾斜的角度相匹配才能避免刀痕和空洞。

47、第二方面,本发明提供一种3dnada闪存垂直通道的超薄电镜样品,所述超薄电镜样品采用第一方面所述的3dnada闪存垂直通道的超薄电镜样品的制样方法制得。

48、本发明第二方面的超薄电镜样品厚度薄,能够看清3dnada闪存垂直通道的垂直孔,且制样成功率高,样品上不存在刀痕和空洞。

49、优选地,所述超薄电镜样品的厚度≤30nm,例如可以是20nm、22nm、23nm、24nm、25nm、26nm、27nm、28nm、29nm或30nm等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

50、优选地,所述超薄电镜样品的表面无线痕且无空洞。

51、优选地,所述3dnada闪存垂直通道包括器件以及连接所述器件的底层;所述底层上设置有至少三排器件,所述器件内设有均匀分布的垂直孔。

52、优选地,所述垂直孔的直径为25~40nm,例如可以是25nm、26nm、27nm、28nm、29nm、30nm、32nm、34nm、35nm、38nm或40nm等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

53、优选地,所述垂直孔的深宽比为20~30,例如可以是20、21、22、23、24、25、26、27、28、29或30等,但不限于所列举的数值,该范围内其他未列举的数值同样适用。

54、优选地,所述器件包括交替叠加设置的钨层和氧化硅层。

55、与现有技术相比,本发明至少具有以下有益效果:

56、(1)本发明提供的3dnada闪存垂直通道的超薄电镜样品的制样方法可以实现消除刀痕,获得高质量的超薄3dnand闪存垂直孔透射电镜分析样品,提升了质量和成功率,成功率优选可达100%;

57、(2)本发明提供的超薄电镜样品厚度≤30nm,能够较好地观察3dnada闪存垂直通道的表面形态。

- 还没有人留言评论。精彩留言会获得点赞!