高速高精度的电压陡降监测电路

本发明属于数字集成电路设计和电源管理领域,尤其涉及一种高速高精度的电压陡降监测电路。

背景技术:

1、集成电路的快速发展,使处理器需要承担更复杂多变的任务,剧烈的负载变化给供电网络的稳定性带来挑战。负载变化直接导致供电电流的变化,进而产生电压陡降现象。这意味着时序余量不足甚至不满足最低需求,进而导致计算错误。通常电压陡降现象可以划分为三个阶段,其中一阶电压陡降最难以监测,其频率和幅度取决于封装电感和片上电容,频率范围从几十到几百兆赫兹,幅度范围从几十到上百毫伏。

2、传统设计由于无法快速、精准的监测电压陡降,故采用保护环设计来应对,其要求系统工作在更高的电压、更低的频率,即使电压陡降出现,仍能满足时序要求。然而,芯片的动态功耗与电压呈二次方的关系,静态功耗呈线性关系。因此,保护环方案会导致额外的功耗和温度代价,违背低功耗设计原则。近年来,如何快速、精准的实现电压陡降监测,使系统能更快的做出调节响应,进而压缩保护环获得能效收益,成为目前学术界和工业界的研究热点。

3、面对电压陡降现象时,传统的模拟电压陡降监测电路主要实现一种阈值比较功能,尽管其具备结构简单的优点,但仅可用于判断电压是否低于预设阈值。如需设置多个阈值进行电压判断,通常需要多组参考电压或多组电压陡降监测电路电路,显著增加了硬件代价。另一方面,传统模拟模数转换器(模拟adc)采样频率低,难以捕捉电压陡降过程。因此,数字电压陡降监测电路具备分辨率高、响应速度快的优点,比传统模拟电压陡降监测电路更适用于电压陡降监测任务。目前的数字传感器研究主要可分为两条技术路线:1)基于延迟链构建的数字电压陡降监测电路,具备结构简单、高采样率的优点,但是监测范围有限,延迟链的稳定性较差,易受噪声影响;2)基于环形振荡器构建的电压陡降监测电路,具备高分辨率、高采样率的优点,能更精准的监测电压陡降现象。另外,结合计数器设计,有效提升了电压陡降监测电路的监测范围。但是,其量化逻辑较为复杂,通常需要多个周期才能得到电压量化结果,实时性差。

4、总的来说,电压陡降现象,尤其是对系统威胁最大的一阶电压陡降现象(降幅>100mv,时间<10ns),仍然难以被现有的数字电压陡降监测电路精准、快速的监测。其设计挑战包括:1)电压陡降监测电路的分辨率受环形振荡器的性能限制,但缺乏一种面向高电压灵敏度和负载平衡的环形振荡器设计方法;2)基于“环形振荡器-计数器”的设计思路能有效拓宽电压检测范围,但是传统的计数器设计会破环振荡器接入结点的负载平衡,导致最终量化结果抖动;3)传统数字电压陡降监测电路的量化逻辑复杂、关键路径长,限制了最大采样率,或需要多个周期才能得到最终量化结果,即滞后现象严重。

技术实现思路

1、本发明目的在于提供一种高速高精度的电压陡降监测电路,有效提升了电压分辨率和采样率,降低了响应时延,解决了大规模集成电路中的电压陡降现象难以被准确、及时监测的问题。

2、本发明为实现上述发明目的采用如下技术方案:

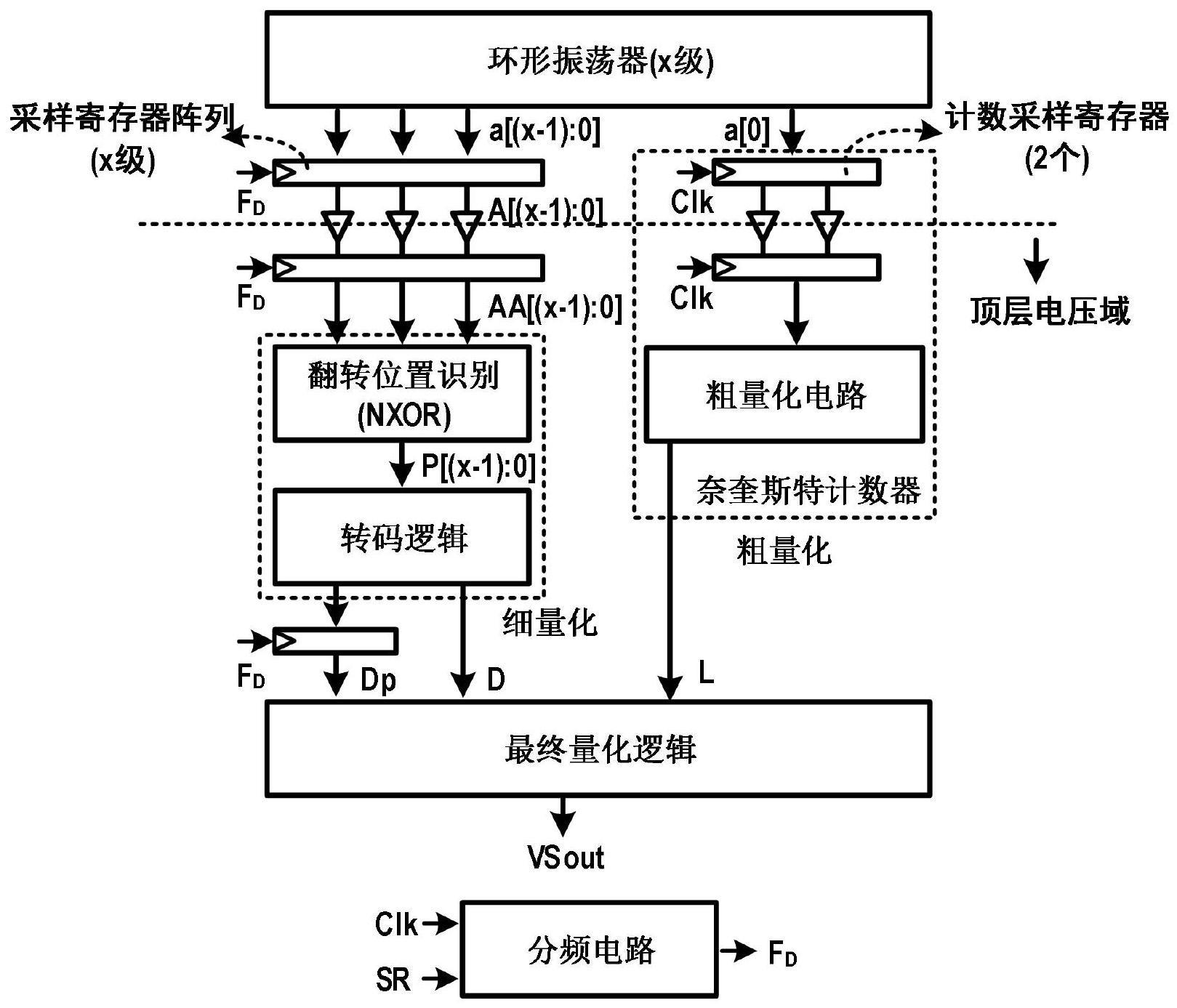

3、一种高速高精度的电压陡降监测电路,包括优化设计的环形振荡器,采样寄存器阵列,奈奎斯特计数器,高速电压量化电路,分频电路;利用优化设计的环形振荡器将电压变化映射为标准单元的延迟变化,由采样寄存器阵列根据量化时钟fd,采样环形振荡器的每个结点的电压状态;在n个采样周期内,由奈奎斯特计数器的计数采样寄存器监测计数结点的翻转,并由奈奎斯特计数器的粗量化电路计算翻转次数,得到粗量化结果l;高速电压量化电路对环形振荡器的采样结果进行细量化处理,得到环形振荡器的翻转位置和细量化结果d,并结合粗量化结果l,计算最终的电压量化码值vsout;分频电路使量化时钟的频率可配置为采样时钟的频率的1/n倍。

4、环形振荡器的优化设计方法包括电路设计和版图设计层面,用于构建一种高电压灵敏度和负载平衡的环形振荡器,进而提升电压陡降监测电路的分辨率并抑制输出抖动;针对环形振荡器翻转位置的采样寄存器阵列,在量化时钟fd上升沿到达时,采样并获取环形振荡器每个结点的电压状态;针对奈奎斯特计数器的两个计数采样寄存器,分别在采样时钟clk的上升沿和下降沿到达时,采样并获取计数结点的电压状态;奈奎斯特计数器的粗量化电路用于统计计数结点在n个采样时钟周期内的翻转次数,作为粗量化结果;高速电压量化电路根据采样寄存器阵列的采样结果,执行细量化操作,并计算最终量化结果;分频电路用于配置量化时钟fd的频率,其可配置为采样时钟clk的频率的1/n倍,其中n=2^(i-1),i为不小于1的正整数;最终量化结果为10-bit数据vsout。

5、所述优化设计的环形振荡器是以构成环形振荡器的标准单元类型、阈值、驱动能力和功耗代价四个维度为变量,找到最高电压灵敏度的环形振荡器电路设计,提升了电压陡降监测电路的分辨率;并且提供了一种一次折叠、紧凑排布的环形振荡器版图设计,保证了环形振荡器每个结点之间的负载平衡,抑制了输出抖动;

6、所述奈奎斯特计数器,利用高频采样时钟激励采样寄存器,对计数结点的电压状态采样并处理,得到计数结点在一段时间的翻转次数,解决了传统计数器的计数延迟导致亚稳态采样的问题,提升了电压陡降监测电路的监测范围,保持了环形振荡器每个结点之间的负载平衡。

7、所述高速电压量化电路,将环形振荡器结点的采样结果送往顶层电压域执行同或操作,利用转码逻辑得到细量化结果,结合粗量化结果,计算最终的电压量化码值。高速电压量化电路,实现了环形振荡器翻转位置的细量化,在架构上将粗量化和细量化并行处理,提升了传感器的最高采样率和最高量化时钟的频率;

8、所述高速高精度的电压陡降监测电路,通过优化环形振荡器设计,实现了高电压分辨率,最高达到ghz级的采样频率和量化频率,能有效监测最为恶劣的一阶电压陡降现象,解决了大规模集成电路中的电压陡降现象难以被准确、及时监测的问题。

9、进一步的,环形振荡器的电路设计方法为:以构成环形振荡器的标准单元类型、阈值、驱动能力和功耗代价四个维度为变量,通过仿真实验得到不同的环形振荡器的结点频率;在固定的电压差异下,结点频率差额越大的环形振荡器结构,具有更高的电压灵敏度,基于其构建的电压陡降监测电路具备更优秀的分辨率。环形振荡器的电路设计的具体步骤为:

10、步骤1:环形振荡器由x级、相同的标准单元构成,且x为大于等于3的奇数。其中,标准单元采用级联的方式连接,每一个标准单元的输出端,接到下一级标准单元的输入端,且最后一级标准单元的输出端连接到第一级标准单元的输入端,首尾相接构成环状。

11、步骤2:以构成环形振荡器的标准单元类型、阈值、驱动能力和功耗代价四个维度为变量,评估不同的环形振荡器的结点频率。

12、步骤3:在固定的电压差异下,计算结点频率差额,找到差额越大的环形振荡器结构,实现电压陡降监测电路分辨率的改善。

13、进一步的,环形振荡器的版图优化设计方法为:环形振荡器的版图排布采用一次折叠、紧凑排布设计;其中,构成环形振荡的标准单元布置于内层,分为二行,每行等间距放置,两行之间的距离为布线规则允许的最小距离;每个标准单元对应的采样寄存器布置于外层,二者相邻放置;保证了构成环形振荡器的标准单元之间连线距离相等,最小化标准单元输出端到采样寄存器输入端的布线距离,保证环形振荡器结点之间的负载平衡。由于构成x级环形振荡器的标准单元的输出结点,即a[0],a[1],···,a[x-1],都要接到相应的采样寄存器的数据端,因此在版图设计层面,要将环形振荡器和采样寄存器阵列一起考虑。环形振荡器的版图优化设计的具体步骤为:

14、步骤1:环形振荡器的版图排布采用一次折叠设计,其中,构成环形振荡的标准单元布置于内层,分为二行,每行等间距放置,两行之间的距离为布线规则允许的最小距离。

15、步骤2:每个标准单元对应的采样寄存器布置于外层,二者相邻放置。目的在于最小化振荡器结点到寄存器数据端的布线距离和标准单元之间的布线距离,降低向结点引入的额外负载,并保证每个结点的负载平衡。

16、进一步的,环形振荡器采样方法为:环形振荡器和采样寄存器布置于被测电压域,环形振荡器的结点一一对应的接到采样寄存器阵列的数据端,采样寄存器阵列的时钟端接量化时钟fd,其频率即为量化频率。每一次量化时钟上升沿到达,采样寄存器阵列即完成一次采样操作,结点a[0],a[1],···,a[x-1]的电压状态被采样为寄存器的输出a[0],a[1],···,a[x-1]。a[0],a[1],···,a[x-1]再经过电平转换器送往顶层电压域执行细量化处理。

17、进一步的,奈奎斯特计数器将位于环形振荡器上的计数结点,接到一个由采样时钟下降沿触发的计数采样寄存器的数据端,和一个由采样时钟上升沿沿触发的计数采样寄存器的数据端;这使奈奎斯特计数器的实际采样速率为采样时钟频率的2倍,且实际采样速率始终高于被计数结点的翻转频率的2倍,即满足奈奎斯特采样定律。

18、传统计数器中,计数结点接到寄存器的时钟端,作为触发信号,但这会对计数结点引入过多的额外负载,严重破坏环形振荡器x个结点之间的负载平衡。另一方面,从计数结点翻转,到计数器完成“+1”存在延迟,易导致亚稳态采样现象,进而使最终量化结果错误。本发明提供的奈奎斯特计数器,首先将两个计数采样寄存器置于被测电压域,数据端接计数结点a[0],时钟端接采样时钟clk(其频率为采样频率),该设计能大幅度降低对计数结点a[0]引入的负载,且翻转特征会在clk到达时被立即记录,不存在传统计数器存在的亚稳态采样问题。其中,一个计数采样寄存器由clk的上升沿触发,另一个计数采样寄存器由clk的下降沿触发,该设计将对计数结点的实际采样频率提升为clk的2倍。那么,只需要控制环形振荡器的级数x,使计数结点的频率在电压监测范围内均不高于clk的频率,即可满足奈奎斯特采样定理,不会漏监测该结点的翻转。最后,由两个电平转换器将采样结果送往顶层电压域。

19、进一步的,奈奎斯特计数器的粗量化电路为:计数结点的采样数据经过电平转换器被送往顶层电压域;首先,由两组移位寄存器,对来自电平转换器的信号进行移位存储,相应的,两组寄存器激励对应计数采样寄存器,分别由采样时钟clk的上升沿和下降沿触发,其按时间顺序存储计数结点在一个量化时钟周期内的采样数据。其次,在一个量化时钟周期内的计数结点状态被调用,利用异或逻辑,判断相邻两个状态是否相同,如果不同,则发生一次翻转;反之,则无翻转。最后,由一组加法器,统计一个量化时钟周期内的翻转次数,得到l,完成粗量化。

20、进一步的,高速电压量化电路对采样结果进行细量化的方法为:根据x个采样数据,a[0],a[1],···,a[x-1],执行细量化操作。首先,一组位于顶层电压域的寄存器阵列的数据端,接电平转换器的输出端,激励为量化时钟fd,得到一组x-bit数据aa[0],aa[1],···,aa[x-1]。其次,相邻的两个数据被作为同或逻辑的输入,得到一组x-bit数据p[0],p[1],···,p[x-1],目的在于找到采样时刻的环形振荡器翻转位置,即得到一组独热码,完成翻转定位。最后,由转码逻辑将独热码转为二进制码值,完成细量化操作,得到d。

21、进一步的,高速电压量化电路计算最终电压量化结果的方法为:细量化和粗量化并行执行,用于缩短关键路径的长度,实现快速计算。高速电压量化电路记录上一个量化时钟到达时的细量化结果dp。奈奎斯特计数器的计数结点位于a[0]。如果d>dp,执行公式1的量化逻辑,将两次细量化结果做差,并将粗量化结果l乘以环形振荡器的级数x,再将二者求和。将两次细量化结果做差再减1,粗量化结果减1后乘以环形振荡器的级数,再将二者求和。如果d<dp,意味着奈奎斯特计数器执行了额外的“+1”操作,需要“-1”进行修正,即执行公式2的量化逻辑,将两次细量化结果做差再减1,粗量化结果减1后乘以环形振荡器的级数,再将二者求和。求和结果即为在一次量化周期内环形振荡器翻转的位置改变量,得到当前电压的10-bit量化码值vsout。在一种量化时钟频率下,vsout的码值大小对应着电压状态,数值越大,则电压越高

22、vsout=(d-dp)-x*l (1)

23、vsout=(d-dp-1)-x*(l-1) (2)

24、进一步的,量化时钟的频率的配置方法为:通过可配置的寄存器分频电路,配置信号为sr,使量化时钟的频率为采样时钟的频率的1/n倍,其中n=2^(i-1),i为不小于1的正整数。

- 还没有人留言评论。精彩留言会获得点赞!