射频芯片在片测试的去嵌结构、方法、存储介质及终端与流程

本发明涉及射频芯片在片测试领域,特别是涉及一种射频芯片在片测试的去嵌结构、方法、存储介质及终端。

背景技术:

1、现代电子系统随着功能性与复杂度的显著提升,对于从器件级到系统级每一个环节的精准度要求越来越高。精准的测试结果是器件建模与电路设计的基石,同时亦可以反馈指导器件材料与工艺的优化设计。

2、而芯片级微波元件在片测试过程中,由于芯片本身尺寸很小,通常需要在微波探针和待测件(dut,device-under-test)之间引入包括焊盘(gsg,ground-signal-ground)和微带连接线的测试夹具,尺寸在几十到几百微米之间。因此,最终的测试对象除待测件dut本征结构外还包含了额外的测试夹具寄生网络,结果并不准确。要想获得精准的本征参数,需要采用去嵌入技术剥离gsg焊盘与微带连接线引入的寄生参数,将所测网络的参考平面从探针针尖校准到芯片两端,如图1所示。

3、现有技术中的去嵌入方法分为两大类,一类基于集总电路等效模型,典型的去嵌方法包括open去嵌、open-short去嵌;该方法去嵌的具体步骤为:

4、步骤1:在同一衬底上制备待测件、相应的焊盘结构与微带互连线、开路结构及短路结构,测量s参数,分别得到待测件的s参数smeas、开路结构s参数sopen、短路结构s参数sshort,将上述三种结构的s参数转换为y参数,得到ymeas、yopen、yshort。

5、步骤2:剥离寄生并联部分。计算y1=ymeas-yopen,去除待测件两端口之间的并联寄生,计算y2=yshort-yopen,剥离短路结构两端口并联寄生阻抗。将剥离寄生并联后的y1、y2矩阵转换为z参数z1、z2。

6、步骤3:剥离寄生串联部分,计算zdut=z1-z2,zdut为待测件本征z参数。

7、步骤4:将待测件本征z参数转换为s参数,得到待测件本征s参数。

8、此类方法以集总参数rlc代替分布式微波元件,在低频时误差较小,但是随着工作频率的升高,微带连接线之间因断路产生的电容越来越难以被忽略,且短路结构的地孔近似接地点,无法实现理想短路点,去嵌误差会越来越大,甚至会出现“过去嵌”的现象。

9、另一类去嵌方法基于等效网络参数,典型算法有l-2l方法、trl方法、lrm方法。这一类方法主要的去嵌思路是将整个待测结构等效为微波网络进行分析,待测件及其左右两端的gsg焊盘和微带连接线可等效为三个二端口网络级联,通过特定的矩阵运算消除测试夹具的寄生。基于网络分析的去嵌方法更多得考虑到器件的分布效应,因此在高频段去嵌精度更高。但是,目前的trl方法、lrm方法主要存在的问题是:准确的负载、准确特性阻抗的传输线、理想的匹配结构都很难定义与制作,同时计算过程较为复杂,解方程存在一元二次方程,需要根据假设条件舍弃一个根。相比之下,l-2l方法只需要两组不同长度(l2=2l1)的微带线结构,可以有效降低制作时间和成本,且计算方法为线性方程,不需要假设条件;而现有的l-2l方法也存在一定的局限性:一方面,现有的算法依旧是根据等效电路模型,将测试夹具等效为并联导纳y和特性阻抗z与待测件网络级联,直接推导测试夹具的abcd矩阵;另一方面,目前的方法仅仅适用于对称结构。

10、因此,如何提高高频段的去嵌精度、扩大适用范围,已成为本领域技术人员亟待解决的问题之一。

11、应该注意,上面对技术背景的介绍只是为了方便对本技术的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本技术的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种射频芯片在片测试的去嵌结构、方法、存储介质及终端,用于解决现有技术中的去嵌方法精度低、计算过程复杂、适用范围小等问题。

2、为实现上述目的及其他相关目的,本发明提供一种射频芯片在片测试的去嵌结构,所述射频芯片在片测试的去嵌结构至少包括:

3、与待测件的测试结构形成于同一衬底上的第一微带线测试结构、第二微带线测试结构及负载测试结构;所述第一微带线测试结构包括第一微带线及测试夹具,所述第二微带线测试结构包括第二微带线及测试夹具,所述负载测试结构包括负载及测试夹具;

4、其中,所述第二微带线的长度为所述第一微带线的长度的两倍,所述第一微带线测试结构、所述第二微带线测试结构、所述负载测试结构中的测试夹具与所述待测件的测试夹具的结构及尺寸相同。

5、可选地,所述负载包括已知阻抗的薄膜电阻及地孔,所述薄膜电阻与所述地孔串联。

6、更可选地,当所述待测件两侧的测试夹具对称时,所述负载测试结构包括第一测试单元,所述第一测试单元包括负载及测试夹具,所述第一测试单元中的测试夹具与所述待测件两侧任意一侧的测试夹具的结构及尺寸相同;

7、当所述待测件两侧的测试夹具非对称时,所述负载测试结构包括第二测试单元及第三测试单元,所述第二测试单元及所述第三测试单元均包括负载及测试夹具,其中,所述第二测试单元及所述第三测试单元中的测试夹具分别与所述待测件两侧的测试夹具的结构及尺寸相同。

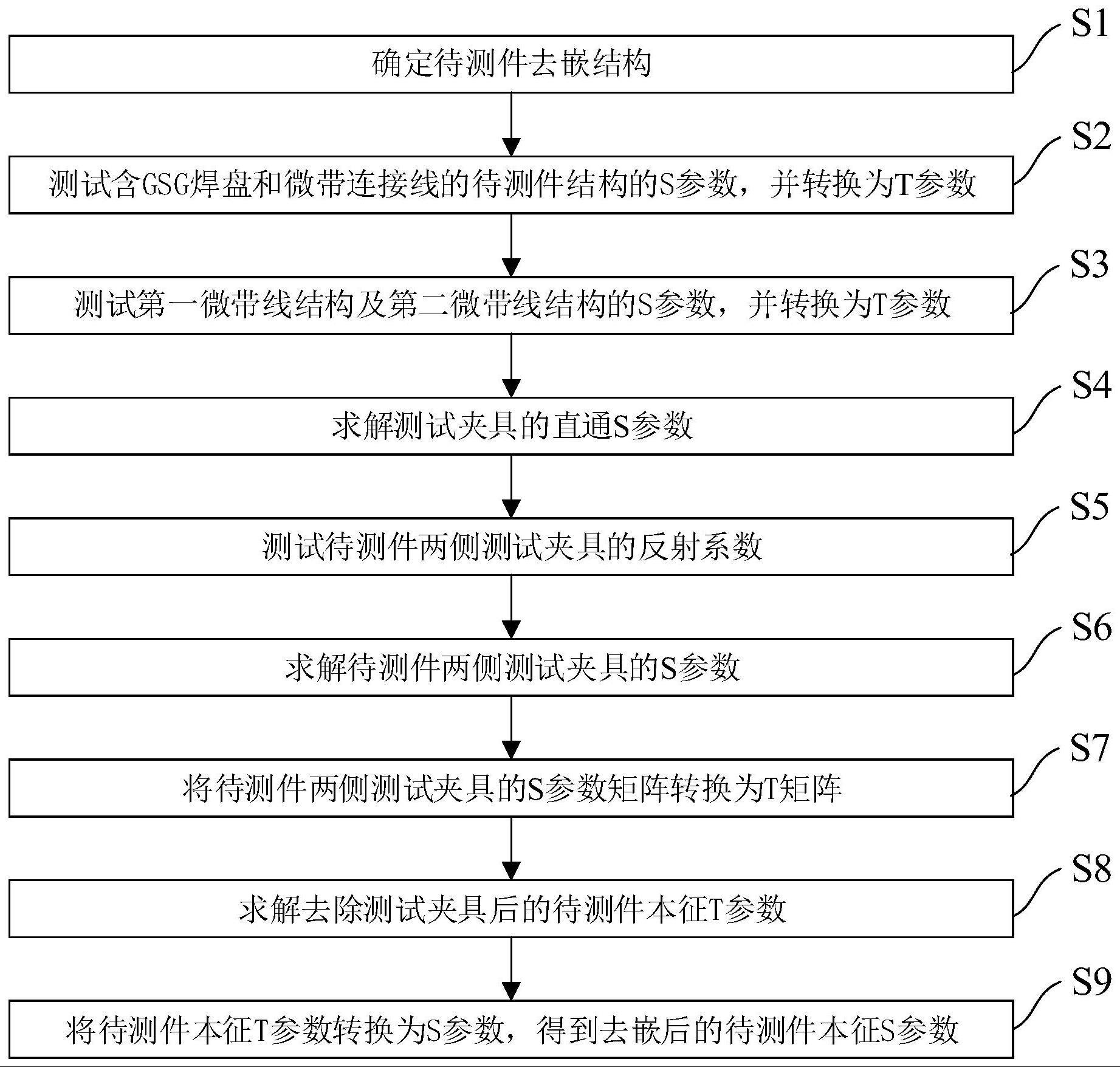

8、为实现上述目的及其他相关目的,本发明还提供一种射频芯片在片测试的去嵌方法,基于上述射频芯片在片测试的去嵌结构实现,所述射频芯片在片测试的去嵌方法至少包括:

9、获取第一微带线测试结构的t参数及第二微带线测试结构的t参数,基于所述第一微带线测试结构及所述第二微带线测试结构的t参数得到测试夹具的直通t参数,并利用矩阵转换得到测试夹具的直通s参数;

10、测试所述负载测试结构,分别得到所述待测件两侧的测试夹具的反射系数;基于所述待测件两侧的测试夹具的反射系数、负载的本征s参数及所述测试夹具的直通s参数求解得到所述待测件两侧的测试夹具的s参数;

11、对所述待测件两侧的测试夹具的s参数进行矩阵转换,得到所述待测件两侧的测试夹具的t参数;

12、获取所述待测件的测试结构的t参数,并基于所述待测件的测试结构的t参数、所述待测件两侧的测试夹具的t参数求解所述待测件的本征t参数;

13、对所述待测件的本征t参数进行矩阵转换,得到所述待测件的本征s参数。

14、可选地,基于所述第一微带线测试结构及所述第二微带线测试结构的t参数得到测试夹具的直通t参数的步骤包括:

15、建立关系式:

16、tl=ta*tx*tb;

17、t2l=ta*tx*tx*tb;

18、tthru=ta*tx*tb*(ta*tx*tx*tb)-1*ta*tx*tb=ta*tb;

19、联立上述三个关系式,得到所述测试夹具的直通t参数,满足:tthru=tl*t2l-1*tl;

20、其中,tl为所述第一微带线测试结构的t参数,t2l为所述第二微带线测试结构的t参数,ta为所述待测件第一侧的测试夹具的t参数,tb为所述待测件第二侧的测试夹具的t参数,tx为第一微带线的t参数,tthru为所述测试夹具的直通t参数。

21、可选地,基于所述待测件两侧的测试夹具的反射系数、负载的本征s参数及所述测试夹具的直通s参数求解得到所述待测件两侧的测试夹具的s参数的步骤包括:

22、建立所述测试夹具的直通s参数与所述待测件第一侧及第二侧的测试夹具的s参数的关系式;建立所述待测件两侧的测试夹具的反射系数与所述待测件第一侧及第二侧的测试夹具的s参数、所述负载的本征s参数的关系式;

23、基于已知的所述测试夹具的直通s参数、所述待测件两侧的测试夹具的反射系数及所述负载的本征s参数计算所述待测件第一侧及第二侧的测试夹具的s参数,满足:

24、

25、其中,

26、

27、a21=k;

28、

29、

30、b12=k;

31、

32、

33、其中,sa为所述待测件第一侧的测试夹具的s参数,a11、a12、a21、a22为所述待测件第一侧的测试夹具的s参数所在矩阵中的元素,sb为所述待测件第二侧的测试夹具的s参数,b11、b12、b21、b22为所述待测件第二侧的测试夹具的s参数所在矩阵中的元素,sthru为所述测试夹具的直通s参数,s11t、s12t、s21t、s22t所述测试夹具的直通s参数所在矩阵中的元素,gamin1为所述待测件第一侧的测试夹具的反射系数,gamin2为所述待测件第二侧的测试夹具的反射系数,gaml为所述负载的本征s参数,k为任意值。

34、更可选地,所述待测件两侧的测试夹具的反射系数与所述待测件第一侧及第二侧的测试夹具的s参数、所述负载的本征s参数的关系式满足;

35、

36、更可选地,当所述待测件两侧的测试夹具对称时,所述待测件第一侧及第二侧的测试夹具的s参数相等。

37、可选地,基于所述待测件的测试结构的t参数、所述待测件两侧的测试夹具的t参数求解所述待测件的本征t参数满足如下关系式:

38、tdut=ta-1*tmeas*tb-1;

39、其中,tdut为所述待测件的本征t参数,ta为所述待测件第一侧的测试夹具的t参数,tb为所述待测件第二侧的测试夹具的t参数,tmeas为所述待测件的测试结构的t参数。

40、可选地,分别通过测试得到所述第一微带线测试结构、所述第二微带线测试结构及所述待测件的测试结构的s参数,再通过矩阵转换得到所述第一微带线测试结构、所述第二微带线测试结构及所述待测件的测试结构的t参数。

41、为实现上述目的及其他相关目的,本发明还提供一种存储介质,其上存储有计算机程序,该程序被处理器执行时实现上述射频芯片在片测试的去嵌方法。

42、为实现上述目的及其他相关目的,本发明还提供一种终端,包括:处理器及存储器;

43、所述存储器用于存储计算机程序;

44、所述处理器用于执行所述存储器存储的计算机程序,以使所述终端执行上述射频芯片在片测试的去嵌方法。

45、如上所述,本发明的射频芯片在片测试的去嵌结构、方法、存储介质及终端,具有以下

46、有益效果:

47、1、本发明的射频芯片在片测试的去嵌结构、方法、存储介质及终端基于简单的l-2l辅助去嵌结构,可以有效降低制作时间和成本。

48、2、本发明的射频芯片在片测试的去嵌结构、方法、存储介质及终端以微波网络理论和矩阵运算为基础,没有假设和等效,没有引入额外误差源,去嵌入的精度仅取决于已知负载精度,误差较小。

49、3、本发明的射频芯片在片测试的去嵌结构、方法、存储介质及终端中已知负载的s参数gaml为唯一误差来源,可通过辅助手段减小已知阻抗值与实际值的误差,提高精度。

50、4、本发明的射频芯片在片测试的去嵌结构、方法、存储介质及终端以解夹具参数为主,去嵌端面精确到器件连接处,被测件可为任意形式,且两端夹具不对称的情况同样适用,适用范围广。

- 还没有人留言评论。精彩留言会获得点赞!