一种基于奇数级偶数级版图分离的测试结构及其方法

本发明涉及集成电路单粒子辐照测试领域,具体而言,涉及一种基于奇数级偶数级版图分离的测试结构及其方法。

背景技术:

1、随着集成电路技术的不断发展,集成电路的复杂度和密度不断提高,对其在单粒子辐照条件下进行可靠和高效的测试变得日益困难。现有的单粒子测试结构往往无法区分重离子是在集成电路的nmos还是pmos晶体管造成影响,难以满足高密度集成电路的测试需求,且测试成本较高,因此我们对此做出改进,提出一种基于奇数级偶数级版图分离的测试结构及其方法。

技术实现思路

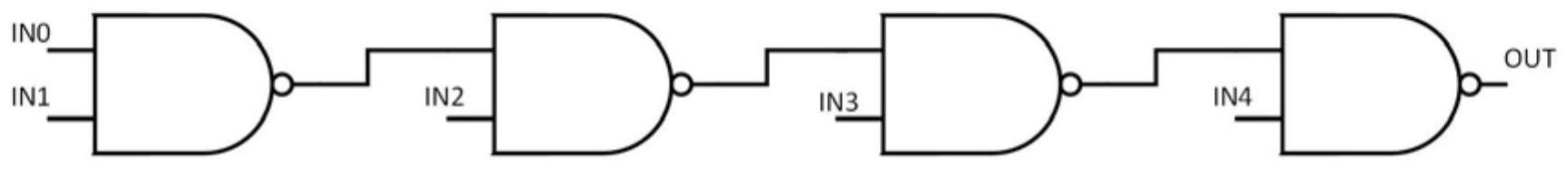

1、本发明的目的在于:针对目前存在的背景技术提出的问题。为了实现上述发明目的,本发明提供了以下技术方案:一种基于奇数级偶数级版图分离的测试结构,将芯片的版图分为奇数级版图和偶数级版图两部分,分别设计测试结构,测试结构采用传统的扫描链(scan chain)或者边缘扫描链(boundary scan);测试信号发生器采用任何一种合适的电路实现,包括但不限于多谐振荡器、格雷码发生器;测试信号采集器采用任何一种合适的电路实现,包括但不限于比较器、反相器;奇数级和偶数级的测试结构采用不同的测试策略,以提高测试效率和准确性;测试结构电路和版图;电路输入通过与非门串联起来,每一级与非门通过一个端口级联,并留出一个端口作为激励的输入端口,即图中的in0、in1、in2、in3、in4,以上端口可接固定输入,也可接入其他的信号源和电路生成测试激励;奇数级和偶数级信号发生的变化存在不同,如果奇数级正常情况下输出的信号为恒为1,则偶数级输出的信号恒为0,反之亦然;通过分析输出的数据是从0向1的翻转还是从1向0的翻转,以此判断出现故障或翻转的电路发生在奇数级还是偶数级。

2、作为本发明优选的技术方案,在奇数级版图和偶数级版图中连接控制逻辑和数据处理电路,通过测试控制器使用计数器或状态机控制分配的顺序和时间间隔将测试序列分配给奇数级版图和偶数级版图;测试控制器将根据测试序列分配逻辑,将相应的测试序列发送到奇数级版图和偶数级版图。

3、作为本发明优选的技术方案,在奇数级版图和偶数级版图中添加相应的数据接口电路,以与数据传输通道进行连接;这些接口电路包括数据输入缓冲器和数据输出缓冲器,用于接收和发送数据;在奇数级版图和偶数级版图中分别实现数据传输通道的接口逻辑;这包括将数据从输入缓冲器传输到通道,以及从通道将数据传输到输出缓冲器。

4、作为本发明优选的技术方案,数据传输通道将接收到的数据传输到奇数级版图和偶数级版图的输入缓冲器中;奇数级版图和偶数级版图从输入缓冲器中接收到数据,进行相应的处理和操作;处理完毕后,奇数级版图和偶数级版图将结果数据传输到输出缓冲器中;数据传输通道将奇数级版图和偶数级版图的输出缓冲器中的数据传输到测试控制器。

5、一种基于奇数级偶数级版图分离的测试方法,步骤1:提供奇数级版图和偶数级版图;其中,奇数级版图用于测试奇数级逻辑电路,偶数级版图用于测试偶数级逻辑电路;奇数级版图和偶数级版图相互独立;

6、步骤2:预先设定测试序列;测试序列包括一系列测试激励和测试数据,用于测试逻辑电路的功能和性能;

7、步骤3:通过一个测试控制器控制奇数级版图和偶数级版图的测试过程;测试控制器按照预先设定的测试序列对奇数级版图和偶数级版图进行测试;测试控制器根据需要将测试序列分配给奇数级版图和偶数级版图,实现并行测试;

8、步骤4:在奇数级版图和偶数级版图之间设置数据传输通道;数据传输通道用于在奇数级版图和偶数级版图之间传输测试数据;测试数据通过数据传输通道从奇数级版图传输到偶数级版图,或者从偶数级版图传输到奇数级版图。

9、作为本发明优选的技术方案,步骤1:提供奇数级版图和偶数级版图具体的步骤如下:

10、s11.根据测试需求和电路设计,确定奇数级逻辑电路和偶数级逻辑电路的结构和功能;

11、s12.设计奇数级版图和偶数级版图的逻辑电路图,包括组合逻辑单元、触发器、时钟元件;

12、s13.基于逻辑电路图,进行版图设计,布局逻辑元件的位置和连线;

13、s14.使用相应的电路设计软件进行版图布局和布线;

14、s15.完成奇数级版图和偶数级版图的版图设计和布线,生成相应的版图文件。

15、作为本发明优选的技术方案,步骤2:预先设定测试序列具体的步骤如下:

16、s21.分析逻辑电路的功能和性能要求,确定需要测试的功能和性能参数;

17、s22.根据功能和性能要求,设计测试序列,包括测试激励和测试数据;

18、s23.根据测试序列的设计,编写测试程序或生成测试序列文件;

19、s24.将测试序列文件存储到测试控制器中,以便后续的测试过程使用。

20、作为本发明优选的技术方案,步骤3:通过一个测试控制器控制奇数级版图和偶数级版图的测试的具体过程如下:

21、s31.将测试控制器与奇数级版图和偶数级版图进行连接,确保通信正常;

22、s32.在测试控制器中设置测试模式和参数,包括时钟频率、测试序列选择;

23、s33.启动测试控制器,发送测试指令和测试数据到奇数级版图和偶数级版图;

24、s34.监控奇数级版图和偶数级版图的输出信号,通过测试控制器进行数据采集和分析;

25、s35.根据测试结果,判断奇数级版图和偶数级版图的功能和性能是否符合要求。

26、作为本发明优选的技术方案,步骤4:在奇数级版图和偶数级版图之间设置数据传输通道;数据传输通道用于在奇数级版图和偶数级版图之间传输测试数据的具体过程如下:s41.确定奇数级版图和偶数级版图之间的数据传输需求,包括传输的数据类型和传输速率;

27、s42.设计数据传输通道的结构和接口,包括数据输入和输出的端口、数据总线的宽度,实现数据传输通道的电路连接和信号传输在奇数级版图和偶数级版图中添加相应的数据接口电路,以与数据传输通道进行连接;

28、s43.在测试控制器中设置数据传输通道的参数,包括传输模式、时钟频率;启动测试控制器,发送测试数据通过数据传输通道到奇数级版图和偶数级版图;

29、s44.监控奇数级版图和偶数级版图中的数据接口,通过数据传输通道进行数据交换和传输,根据传输结果,判断数据传输通道的性能和可靠性是否满足要求。

30、作为本发明优选的技术方案,s44.判断数据传输通道的性能和可靠性是否满足要求的具体步骤为:s441.数据完整性:检查接收端是否成功接收到发送端发送的所有数据,并与发送端发送的数据完全一致;通过比较发送端和接收端的数据进行验证;

31、s442.时序正确性:验证数据传输通道是否能够在规定的时钟频率下按时传输数据;通过检查数据的到达时间和时钟信号的稳定性来判断是否存在时序偏差或时钟周期不稳定的问题;

32、s443.传输速率:根据设计要求,比较实际传输速率与预期传输速率之间的差距;如果实际传输速率明显低于预期传输速率,可能存在传输带宽不足或传输延迟过高的问题;

33、s444.抗干扰性:检查数据传输通道是否受到来自其他信号或环境干扰的影响;通过引入外部干扰或模拟噪声来测试数据传输通道的抗干扰性能;

34、s445.错误率:统计在传输过程中可能出现的错误数量,并与设计容忍的错误率进行比较;如果错误率超过设计容忍范围,可能存在传输过程中的错误或噪声问题;

35、s446.可靠性分析:通过长时间运行测试或大量数据传输测试来验证数据传输通道的可靠性;如果在长时间或大数据量测试中没有出现异常或错误,认为数据传输通道具有较高的可靠性。

36、作为本发明优选的技术方案,与现有技术相比,本发明的有益效果:

37、1.采用奇数级偶数级版图分离的方式,将测试结构分散到芯片的不同部分,减小测试结构占用的芯片面积,提高芯片的性能和生产成本。

38、2.采用多种测试策略,提高测试效率和准确性,确保芯片的质量。

39、3.测试结构的设计灵活多样,根据芯片的不同需求进行调整和优化。

- 还没有人留言评论。精彩留言会获得点赞!