干扰检测电路、静电释放保护电路和电池保护芯片的制作方法

本发明涉及集成电路,具体涉及一种干扰检测电路、静电释放保护电路和电池保护芯片。

背景技术:

1、随着如集成电路等电路系统的日益精密、复杂以及多功能化,电路系统易受如射频、电磁干扰的影响,使得其性能和电路稳定性受到影响。

2、现有的电路系统无法快速自检出干扰信号,依靠外部的干扰检测仪来检测干扰信号,不仅存在干扰检测的准确性和及时性的问题,还致使后端电路的抗干扰电路设计受到挑战。

技术实现思路

1、本发明实施例提供一种干扰检测电路、静电释放保护电路和电池保护芯片,至少可以快速自检出干扰信号,克服前述问题。

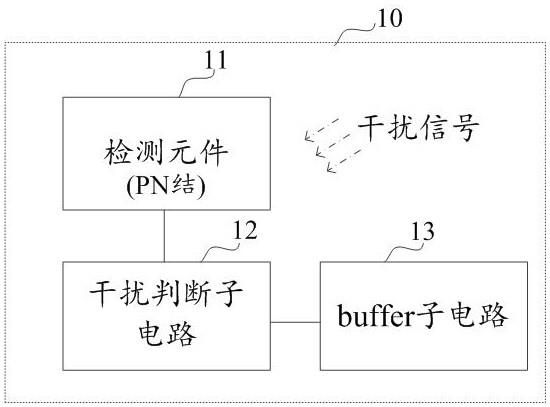

2、从第一方面,本发明实施例公开了一种干扰检测电路,包括:

3、用于接收干扰信号的包括pn结的检测元件;

4、干扰判断子电路,基于检测元件截止时的漏电大小判断检测元件是否受到干扰。

5、在本发明一实施例中,干扰判断子电路包括:采样模块和比较模块;

6、采样模块基于检测元件截止时漏电产生检测信号;

7、比较模块基于检测信号与检测阈值判断检测元件是否受到干扰,并在确定检测元件受到干扰时输出干扰标志信号。

8、在本发明一实施例中,采样模块包括与检测元件串联的第一电阻元件,基于第一电阻元件与检测元件截止时漏电以产生检测信号。

9、在本发明一实施例中,其中,第一电阻元件与检测元件之间的连接节点用于产生检测信号。

10、在本发明一实施例中,采样模块包括与检测元件串联的第一mos元件,基于第一mos元件与检测元件截止时漏电以产生检测信号。

11、在本发明一实施例中,第一mos元件的漏端或源端用于与检测元件串联,第一mos元件的栅端用于接其漏端或接能使第一mos元件导通的外部输入电压vb;

12、其中,基于第一mos元件与检测元件截止时漏电产生检测信号。

13、在本发明一实施例中,其中,第一mos元件用于与检测元件连接的漏端或源端用于产生该检测信号。

14、在本发明一实施例中,采样模块包括电容元件和复位单元;

15、电容元件与检测元件串联,电容元件接收检测元件流出的漏电流产生检测信号;

16、复位单元按照预设时间间隔将电容元件的电压复位至初始状态。

17、在本发明一实施例中,比较模块包括负载元件和第二mos元件;其中,检测阈值为第二mos元件的导通阈值;

18、负载元件与第二mos元件的源端或漏端连接形成串联电路,第二mos元件的栅端基于检测信号与导通阈值控制串联电路是否导通,以输出干扰标志信号。

19、在本发明一实施例中,负载元件为电阻。

20、在本发明一实施例中,比较模块包括:

21、阈值电压产生子单元,用于产生检测阈值;

22、比较器,用于将检测信号与检测阈值进行比较,以输出干扰标志信号。

23、在本发明一实施例中,干扰检测电路还包括:buffer子电路;

24、buffer子电路用于将干扰判断子电路在确定检测元件受到干扰时输出的干扰标志信号增强后输出。

25、从第二方面,本发明实施例还公开了一种静电释放保护电路,包括:

26、用于对目标电压进行静电释放保护的一个或多个esd模块;

27、如本发明实施例所述的干扰检测电路,其中,干扰检测电路输出的干扰标志信号用于表征esd模块有受干扰信号影响的风险;

28、以及,与目标电压相关的功能模块,功能模块在接收到干扰标志信号时停止工作或切换工作状态。

29、在本发明一实施例中,干扰检测电路中的检测元件与esd模块的结构相同。

30、在本发明一实施例中,检测元件的尺寸小于esd模块。

31、在本发明一实施例中,在干扰检测电路中,采样模块与检测元件串联后所连接的高电压或低电压为目标电压。

32、在本发明一实施例中,在干扰检测电路中,采样模块与检测元件串联后所连接的高电压和低电压与目标电压不相关。

33、从第三方面,本发明实施例还公开了一种电池保护芯片,包括:如本发明实施例所述的静电释放保护电路;其中,目标电压为所述芯片的过流检测端的电压。

34、在本发明一实施例中,功能模块为充电过流检测模块、放电过流检测模块以及短路检测模块中至少一者。

35、本发明实施例包括以下优点:

36、本发明实施例提供了一种干扰检测电路,包括:用于接收干扰信号的包括pn结的检测元件以及干扰判断子电路,当检测元件的pn结受到干扰信号时,pn结的漏电流快速增大,本发明基于这一特性将现有包括pn结的半导体元件作为检测元件,干扰判断子电路基于检测元件截止时的漏电大小判断检测元件是否受到干扰,以此快速自检出电路受到干扰信号影响的情况;

37、本发明实施例提供了一种静电释放保护电路,包括:用于对目标电压进行静电释放保护的一个或多个esd模块;如本发明实施例所述的干扰检测电路,其中,干扰检测电路输出的干扰标志信号用于表征esd模块有受干扰信号影响的风险;以及,与目标电压相关的功能模块,该功能模块在接收到干扰标志信号时停止工作或切换工作状态,以此降低了干扰信号对功能模块的工作稳定性以及相关检测结果的准确性的影响。

技术特征:

1.一种干扰检测电路,其特征在于,包括:

2.根据权利要求1所述的干扰检测电路,其特征在于,

3.根据权利要求2所述的干扰检测电路,其特征在于,所述采样模块包括与所述检测元件串联的第一电阻元件,基于所述第一电阻元件与所述检测元件截止时漏电以产生所述检测信号。

4.根据权利要求3所述的干扰检测电路,其特征在于,

5.根据权利要求2所述的干扰检测电路,其特征在于,所述采样模块包括与所述检测元件串联的第一mos元件,基于所述第一mos元件与所述检测元件截止时漏电以产生所述检测信号。

6.根据权利要求5所述的干扰检测电路,其特征在于,

7.根据权利要求6所述的干扰检测电路,其特征在于,

8.根据权利要求2所述的干扰检测电路,其特征在于,

9.根据权利要求2-8任一项所述的干扰检测电路,其特征在于,

10.根据权利要求9所述的干扰检测电路,其特征在于,

11.根据权利要求2-8任一项所述的干扰检测电路,其特征在于,

12.根据权利要求1或2所述的干扰检测电路,其特征在于,

13.一种静电释放保护电路,其特征在于,包括:

14.根据权利要求13所述的静电释放保护电路,其特征在于,

15.根据权利要求13或14所述的静电释放保护电路,其特征在于,

16.根据权利要求13所述的静电释放保护电路,其特征在于,

17.根据权利要求13所述的静电释放保护电路,其特征在于,

18.一种电池保护芯片,其特征在于,包括:如权利要求13-17任一项所述的静电释放保护电路;其中,所述目标电压为所述芯片的过流检测端的电压。

19.根据权利要求18所述的电池保护芯片,其特征在于,

技术总结

本发明实施例提供了一种干扰检测电路、静电释放保护电路和电池保护芯片,涉及集成电路技术领域,该干扰检测电路包括:用于接收干扰信号的包括PN结的检测元件以及干扰判断子电路,当检测元件的PN结受到干扰信号时,PN结的漏电流快速增大,本发明基于这一特性将现有包括PN结的半导体元件作为检测元件,干扰判断子电路基于检测元件截止时的漏电大小判断检测元件是否受到干扰,以此快速自检出电路受到干扰信号影响的情况。

技术研发人员:高兴波,唐永生,黄立

受保护的技术使用者:成都利普芯微电子有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!