一种时钟频率监测电路和方法与流程

本发明属于集成电路设计领域,具体属于一种时钟频率监测电路和方法。

背景技术:

1、现有的时钟频率监测电路包括数字电路实现以及定制模拟电路实现两种方案。例如在专利《时钟检测电路、时钟检测方法、时钟校准装置及时钟校准方法》(cn115549654a)中,基于分频器、倍频器、fifo存储器、计数器等数字电路实现频率检测,要求基准时钟和待测时钟的频率为整倍数。另一种常用的数字电路实现时钟监测的方案,是采用高速的已知时钟,采样低速的待测时钟,通过计算低速时钟沿中包含多少个高速时钟周期,实现时钟频率的监测。通常要求已知时钟的频率是待测时钟的二倍以上,且在已知和被测时钟的频率相差不大时候,监测误差很大。

2、例如论文《基于单稳态结构的时钟丢失检测电路设计》采用定制的单稳态模拟电路实现时钟频率过低监测预警,该结构需要通过定制模拟电路实现,当时钟周期大于258us时可产生异常预警信号,但是只能监测时钟频率低于3.88khz这种情况。

3、综上所述,现有技术中的时钟频率监测电路存在监测误差大、适用范围窄以及输入信号要求严苛的问题。

技术实现思路

1、为了解决现有技术中存在的问题,本发明提供一种时钟频率监测电路和方法,用于解决现有技术中监测误差大,适用范围窄以及输入信号要求严苛的问题。本发明提出的方法和结构不要求已知参考时钟必须比待测时钟频率高,且在频率相当的情况下误差很小,应用灵活性以及误差控制均优于传统结构。

2、为实现上述目的,本发明提供如下技术方案:

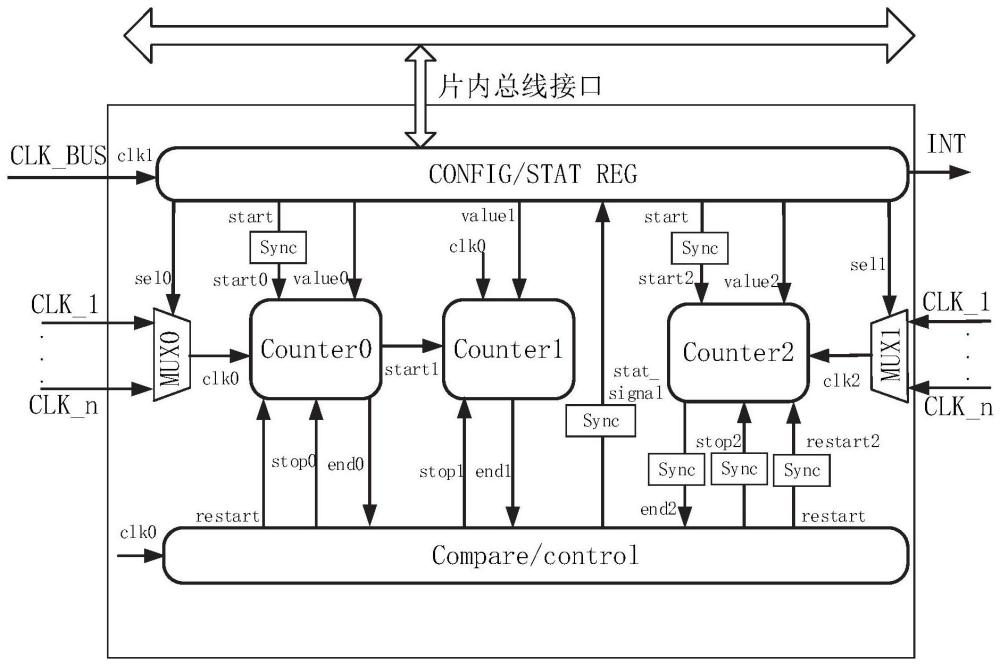

3、一种时钟频率监测电路,包括配置状态寄存器、计数器counter0、计数器counter1、计数器counter2、多路选择器mux0、多路选择器mux1和比较控制模块;

4、所述配置状态寄存器与片内总线接口连接进行数据交互;所述配置状态寄存器的输出端连接多路选择器mux0和多路选择器mux1控制计数器输入时钟选择;所述配置状态寄存器的输出端分别连接计数器counter0、计数器counter1和计数器counter2;计数器counter0的输出端连接计数器counter1的输入端;所述比较控制模块分别与计数器counter0、计数器counter1和计数器counter2进行数据交互连接;所述比较控制模块的输入端连接参考时钟clk0;

5、所述多路选择器mux0的输入端分别连接配置状态寄存器的输出端和时钟域clk_1~clk_n;多路选择器mux0的输出端连接计数器counter0提供计数时钟;所述多路选择器mux1的输入端分别连接配置状态寄存器的输出端和时钟域clk_1~clk_n;多路选择器mux1的输出端连接计数器counter2提供计数时钟。

6、优选的,还包括信号同步模块,所述信号同步模块用于进行start信号同步、end信号同步、stop信号同步、restart信号同步以及stat_signal信号同步。

7、进一步的,所述信号同步模块采用pls2pls结构。

8、优选的,所述计数器counter0、计数器counter1和计数器counter2为自减计数器。

9、优选的,计数器counter0、计数器counter1、比较控制模块工作在clk0下,clk0在初始化阶段通过多路选择器mux0的sel0信号选通,选择模块外部输入的clk_1~clk_n的任意一个作为时钟源;

10、所述计数器counter0和计数器counter1的计数初值value0和value1由配置状态寄存器模块输出;

11、所述计数器counter0的启动信号start0由配置状态寄存器模块在初始化之后输出并经过同步到达;计数器counter0的重载信号restart由比较控制模块控制输出,计数器counter0的单循环计数结束信号end0输出给比较控制模块;

12、所述计数器counter1的启动信号start1由计数器counter0模块输出,计数器counter0自减到0后输出start1信号启动计数器counter1的自减计数,计数器counter1自减计数到0之后,输出单循环计数结束信号end1给比较控制模块。

13、优选的,所述计数器counter2工作在clk2时钟域下,clk2在初始化阶段通过mux1的sel1信号选通,选择模块外部输入的clk_1~clk_n的任一个作为时钟源;

14、计数初值value2由配置状态寄存器模块输出,计数器counter2的启动信号start2由配置状态寄存器模块在初始化之后输出并经过同步到达;计数器counter2的重载信号restart2由比较控制模块控制输出并经过同步到达,计数器counter2的单循环计数结束信号end2输出经过同步后给比较控制模块。

15、优选的,比较控制模块接收计数器counter0、计数器counter1、计数器counter2的结束标志,判断被测时钟clk2计数过程是否满足预期目标,当clk2频率符合预期时输出restart信号控制计数器重载,当clk2频率异常时发送stop信号给三个计数器,并发送stat_signal给配置状态寄存器模块,用于产生工作正常或异常的状态及中断;所述比较控制模块工作在clk0时钟域下,与不同时钟域下控制逻辑的信号交互均进行同步处理。

16、优选的,在初始化阶段,时钟频率监测电路接收总线接口信号,完成clk0、clk2输入时钟选择,完成计数器counter0、计数器counter1、计数器counter2的计数初值配置,之后总线主机配置start位开始工作流程。

17、优选的,在循环工作阶段,总线主机配置start之后,配置状态寄存器模块基于start产生同步后的输出start0和start2给计数器counter0和计数器counter2,启动计数实现频率监测。

18、一种时钟频率监测方法,基于上述任意一项所述的一种时钟频率监测电路,包括以下过程,

19、时钟频率监测电路接收来自片内总线的配置信息,完成初始化;

20、初始化完成后,接收总线上启动工作信号start,经过同步后分别为start0和start2,开始循环工作;计数器counter0和计数器counter2一起开始自减计数,当计数器counter0自减到0时候,触发计数器counter1启动自减计数;三个计数器的计数状态保存和控制由比较控制模块来完成,设定计数器counter0自减到0之后时刻为t1,计数器counter1自减到0的时刻为t2,如果t1到t2此段时间内比较控制模块接收到计数器counter2的自减到0的标志,则认为被测时钟clk2的频率符合预期;否则,则认为clk2的频率不符合预期,比较控制模块输出stop0、stop1、stop2信号控制计数器停止工作,通过int信号输出错误中断告知处理器来进行处理,同时计数器停止工作;

21、未发生错误的正常工作情况下,每个循环计数完毕均以计数器counter1计数到0之后开始,比较控制模块发送重载控制信号给计数器counter0和计数器counter2。

22、与现有技术相比,本发明具有以下有益的技术效果:

23、本发明提供一种时钟频率监测电路,通过对两个时钟域下的计数逻辑进行实时精确控制,实现用户预定义频率波动范围的时钟频率监测,同时输出频率监测异常或正常的监测结果信号。本发明使用纯数字电路实现,不涉及模拟电路,实现方法明确,控制逻辑简单,相较于传统的解决方案具有低开销、易实现以及高灵活性的特点。本发明采用数字电路实现,易于soc设计实现和集成;实现效果更有优势,可实现频率过高或过低情况的监测和预警。本发明提出的方法和结构不要求已知参考时钟必须比待测时钟频率高,且在频率相当的情况下误差很小,应用灵活性以及误差控制均优于传统结构。本发明与上述传统的技术相比,技术方案不同,实现效果具有优势,设计结构明确,可方便的集成到不同架构的soc、mcu系统中,使用灵活且通用性较强。

24、本发明提供一种时钟频率监测方法,可根据实际应用需求和系统架构,方便的集成到不同架构的soc/mcu中,结构明确,控制逻辑简单,计数宽度不同可实现不同波动范围和精度下时钟频率的实时监测,不需要定制模拟电路,节省研制周期和流片成本,便于应用。本发明支持soc/mcu片内各个时钟的频率监测,参考时钟和被测时钟选择可配置;本发明支持较慢参考时钟clk0监测较快被测时钟clk1,同样支持较快已知时钟clk0监测较慢的被测时钟clk1,对频率快慢及整数倍比例无要求,优于传统的数字电路时钟监测结构;本发明支持预定义波动范围的时钟频率监测,基于对三个计数器计数初值的配置,可灵活定义被测时钟频率波动范围。这是本发明优于传统的单稳态定制模拟电路时钟监测结构的特点。

- 还没有人留言评论。精彩留言会获得点赞!