芯片测试系统和方法与流程

本发明涉及芯片领域,具体涉及一种芯片测试系统和方法。

背景技术:

1、随着电子工业自动化的发展,各行业对芯片的需求量也越来越大,伴随着芯片的大批量生产,在芯片正式销售、应用之前,需要对芯片的特性、功能等进行详细的测试,对于芯片验证相关的工作,首批生产回来的芯片为盲封芯片,未做过一些芯片属性相关的配置和校准,需要人工对每一颗用于验证的芯片进行相应操作,芯片数量少则百颗,多则上千颗,而且一颗芯片就有很多项配置,配置后的芯片还需要验证和确认。

2、对于电子产品量产的工作,批量生产期间有一个环节就是对电子产品的控制芯片进行程序下载和功能验证,工厂下载一般使用批量下载器提前下载好程序在进行焊接,申请人发现,通过这种方式未针对芯片做数据的验证工作,坏片会被焊接到电路板,导致后面出现返工,从而导致芯片从盲封到量产阶段时测试成本高、周期长的问题。

技术实现思路

1、本发明提供一种芯片测试系统和方法,该系统集合了多量下载、自动测试、记录验证结果等功能,可通用多种芯片以及自定义操作流程,极大地缩短了芯片的测试流程,解决了芯片从盲封到量产阶段时测试成本高、周期长的问题。

2、为实现上述有益效果,本发明实施例提供以下技术方案:

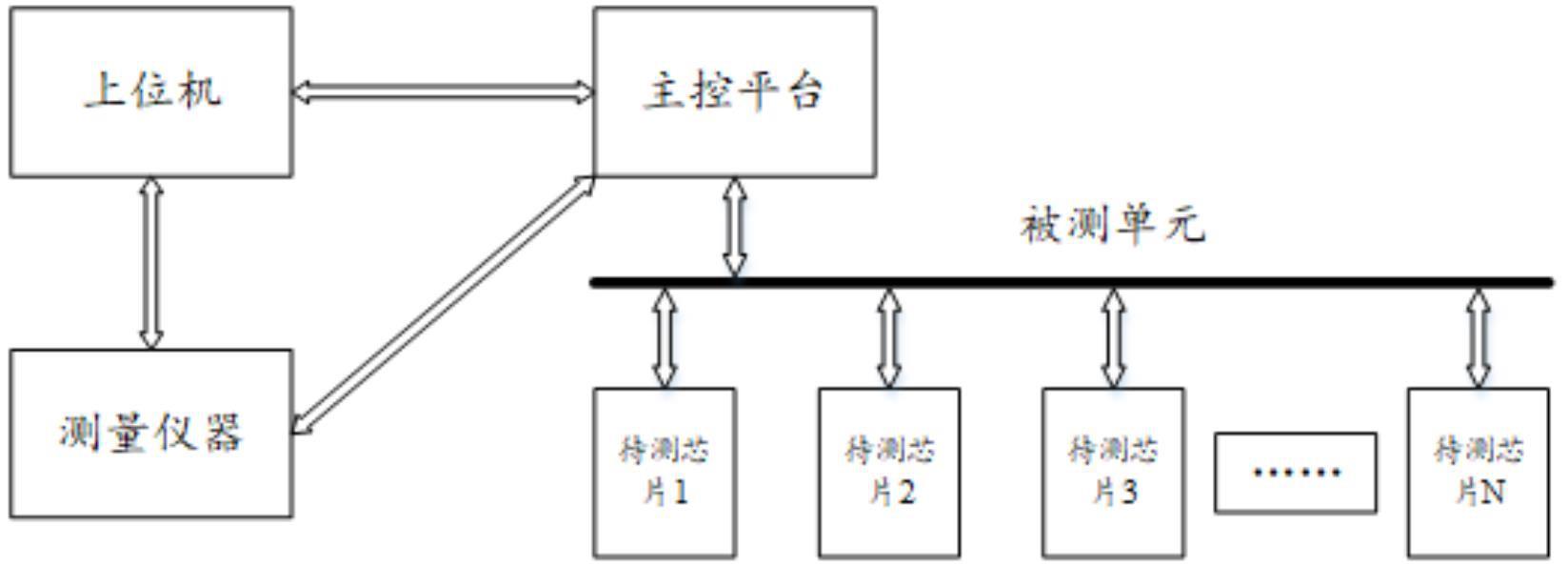

3、第一方面,本申请提供一种芯片测试系统,包括依次连接的上位机、主控平台以及被测单元;

4、所述上位机,用于根据测试工程加载测试指令,将所述测试指令发送至主控平台,并接收所述主控平台返回的测试结果;

5、所述主控平台,用于解析接收到的测试指令,配置与所述测试指令对应的测试操作,以对所述被测单元中的目标端口上的待测芯片进行测试,并查询测试结果;

6、所述被测单元,包括多个统一接口的芯片连接板,分别接入多个待测芯片,所述被测单元用于在上电后执行对应的测试操作。

7、在一实施例中,所述芯片测试系统还包括:

8、测量仪器,所述测量仪器分别与所述上位机和被测单元连接,用于检测所述被测单元中待测芯片的测量值,所述测量仪器包括温箱、频率计以及万用表。

9、在一实施例中,所述上位机还用于根据所述待测芯片导入对应的测试工程,并将所述测试工程中的测试程序发送至所述主控平台;

10、所述主控平台,还用于配置下载模式,并控制所述被测单元中的待测芯片根据所述下载模式下载所述测试程序。

11、在一实施例中,所述上位机通过通用异步收发器与所述主控平台进行连接。

12、在一实施例中,所述主控平台包括继电器,所述继电器用于控制所述被测单元的供电开关以及所述用异步收发器的开关状态。

13、在一实施例中,所述主控平台通过通用输入输出端口连接所述被测单元中待测芯片的引脚,并通过电压调节单元调节所述被测单元中待测芯片的供电电压。

14、在一实施例中,所述主控平台包括多路选择器,所述多路选择器用于在所述被测单元中选取目标待测芯片。并将所述目标待测芯片的mco引脚连接至所述测量仪器。

15、第二方面,本申请提供一种芯片测试方法,所述方法包括:

16、上位机根据待测芯片的规格导入测试工程,并通过主控平台将测试程序发送至被测单元;

17、上位机加载测试指令发送至主控平台;

18、主控平台解析接收到的测试指令,配置与所述测试指令对应的测试操作,以对所述被测单元中的目标端口上的待测芯片进行测试,并查询测试结果返回至上位机。

19、在一实施例中,被测单元包括多个统一接口的芯片连接板,分别接入多个待测芯片,通过主控平台将测试程序发送至被测单元的步骤,包括:

20、当待测芯片通过安全启动模式方式进行测试程序的下载时,所述主控平台配置所述待测芯片的boot pin;

21、当待测芯片通过串行线调试接口进行测试程序的下载时,所述主控平台控制所述待测芯片输出swd序列进入下载模式;

22、当待测芯片通过系统内编程进行测试程序的下载时,所述主控平台控制所述待测芯片使用预设接口和协议进入程序升级模式。

23、在一实施例中,所述方法还包括:

24、接收测试仪器针对所述被测单元中待测芯片的测量值,并将所述测量值返回至上位机。

25、本申请实施例提供的芯片测试系统包括依次连接的上位机、主控平台以及被测单元,上位机用于根据测试工程加载测试指令,将测试指令发送至主控平台,并接收主控平台返回的测试结果,主控平台用于解析接收到的测试指令,配置与测试指令对应的测试操作,以对被测单元中的目标端口上的待测芯片进行测试,并查询测试结果,被测单元包括多个统一接口的芯片连接板,分别接入多个待测芯片,被测单元用于在上电后执行对应的测试操作。本申请实施例构建了一种集合了多量下载、自动测试、记录验证结果等功能的芯片测试系统,可通用多种芯片以及自定义操作流程,极大地缩短了芯片的测试流程,解决了芯片从盲封到量产阶段时测试成本高、周期长的问题。

技术特征:

1.一种芯片测试系统,其特征在于,包括依次连接的上位机、主控平台以及被测单元;

2.根据权利要求1所述的芯片测试系统,其特征在于,所述芯片测试系统还包括:

3.根据权利要求1所述的芯片测试系统,其特征在于,所述上位机还用于根据所述待测芯片导入对应的测试工程,并将所述测试工程中的测试程序发送至所述主控平台;

4.根据权利要求1-3任一项所述的芯片测试系统,其特征在于,所述上位机通过通用异步收发器与所述主控平台进行连接。

5.根据权利要求4所述的芯片测试系统,其特征在于,所述主控平台包括继电器,所述继电器用于控制所述被测单元的供电开关以及所述用异步收发器的开关状态。

6.根据权利要求1-3任一项所述的芯片测试系统,其特征在于,所述主控平台通过通用输入输出端口连接所述被测单元中待测芯片的引脚,并通过电压调节单元调节所述被测单元中待测芯片的供电电压。

7.根据权利要求2所述的芯片测试系统,其特征在于,所述主控平台包括多路选择器,所述多路选择器用于在所述被测单元中选取目标待测芯片,并将所述目标待测芯片的mco引脚连接至所述测量仪器。

8.一种芯片测试方法,其特征在于,所述方法包括:

9.根据权利要求8所述的芯片测试方法,其特征在于,被测单元包括多个统一接口的芯片连接板,分别接入多个待测芯片,其特征在于,通过主控平台将测试程序发送至被测单元的步骤,包括:

10.根据权利要求8所述的芯片测试方法,其特征在于,所述方法还包括:

技术总结

本申请公开了一种芯片测试系统和方法。芯片测试系统包括依次连接的上位机、主控平台以及被测单元,上位机用于根据测试工程加载测试指令,将测试指令发送至主控平台,并接收主控平台返回的测试结果,主控平台用于解析接收到的测试指令,配置与测试指令对应的测试操作,以对被测单元中的目标端口上的待测芯片进行测试,并查询测试结果,被测单元包括多个统一接口的芯片连接板,分别接入多个待测芯片,被测单元用于在上电后执行对应的测试操作。本申请实施例构建了一种集合了多量下载、自动测试、记录验证结果等功能的芯片测试系统,可通用多种芯片以及自定义操作流程,极大地缩短了芯片的测试流程。

技术研发人员:刘吉平,陈筠,王翔,郑增忠

受保护的技术使用者:深圳市航顺芯片技术研发有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!