一种半导体器件的UIS测试电路和UIS测试方法与流程

本发明涉及半导体器件测试,尤其是涉及一种半导体器件的uis测试电路和uis测试方法。

背景技术:

1、在电力电子电路中,mos或igbt器件经常与感性负载连接,如果感性负载两端没有并联续流二极管,则器件在每次关断时都会使储存在电感中的高电压和大电流流入mos管,由于此时栅极已关闭,则mos管会短暂处于击穿状态,这一过程为非钳位感性负载开关过程(uis)。

2、uis能力是衡量功率器件可靠性的重要指标。通常用eas(单脉冲雪崩击穿能量)和ear(重复雪崩能量)来衡量mos管耐受uis的能力。uis测试可以模拟mos管在系统应用中遭遇极端电热应力,通过这种测试,可以得到mos器件耐受能量的能力。

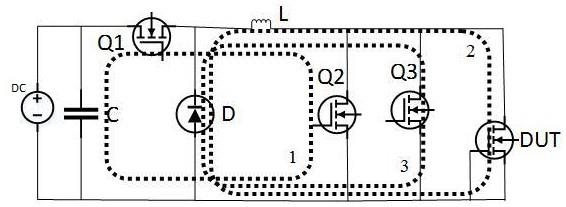

3、图1示出了传统uis测试电路图。如图1所示,电感储能通道1为c1、q1、l、陪测管q2(q1和陪测管q2沟道导通)回路,电感放电通道2为d1、l和dut (q1和陪测管q2沟道关断,dut驱动gs短接,dut一直关断)回路。当陪测管q2用高压igbt单管时,由于拖尾电流存在,导致关断损耗大,关断温升高,再加上陪测管q2的导通损耗,陪测管温升剧烈,导致单管陪测管方案难以实现。如果选用高电压和大电流的陪测模块则会大大增加测试成本。

技术实现思路

1、为了降低陪测管温升和uis测试成本,本方案提供了一种半导体器件的uis测试电路和uis测试方法,通过将陪测管电路分为两部分,使陪测管的损耗由两部分电路承担,电感储能和电感续流由高压单管构成,电感续流通道向电感放电通道切换由低压单管(低压单管可串联实现高压)切换实现,能够降低器件温升。相比于模块化陪测管方案,便于电路扩充,降低陪测管选择成本和uis测试成本。

2、根据本发明的一个方面,提供了一种半导体器件的uis测试电路,包括:电源、电容、第一开关管、电感、续流二极管、被测器件和陪测管电路。其中,陪测管电路包括并联的第一陪测管和第二陪测管,第一陪测管为高压单管,第二陪测管为低压单管。

3、第一陪测管、第二陪测管和被测器件并联;电感的一端分别连接第一开关管、续流二极管,另一端分别连接第一陪测管、第二陪测管和被测器件的一端;

4、电容并联在电源两侧,用于存储并提供稳定的电压源,电容的一端连接第一开关管,另一端分别连接续流二极管、第一陪测管、第二陪测管、被测器件的另一端。

5、可选地,在本发明提供的半导体器件的uis测试电路中,第一陪测管能够承受的电压范围高于第二陪测管能够承受的电压范围;第一陪测管和第二陪测管为采用硅或碳化硅材料的单管器件,被测器件为mosfet管或igbt管。

6、可选地,在本发明提供的半导体器件的uis测试电路中,uis测试电路还包括时序控制电路,时序控制电路用于控制第一开关管、第一陪测管、第二陪测管的导通和关断。

7、可选地,在本发明提供的半导体器件的uis测试电路中,时序控制电路用于在第一开关管关断时,控制第一陪测管和第二陪测管导通,延迟第一预设时间后控制第一陪测管关断,延迟第二预设时间后控制第二陪测管关断,第一预设时间和第二预设时间为微秒级。

8、可选地,在本发明提供的半导体器件的uis测试电路中,当第一开关管和第一陪测管导通时,电容、第一开关管、电感、第一陪测管构成电感储能回路;当第一开关管和第一陪测管关断、第二陪测管导通时,续流二极管、电感、第二陪测管构成电感续流回路;当第一开关管、第一陪测管、第二陪测管关断时,续流二极管、电感和被测器件构成电感放电回路。

9、可选地,在本发明提供的半导体器件的uis测试电路中,陪测管电路包括并联的第一数量的第一陪测管和串联的第二数量的第二陪测管,第一数量和第二数量根据被测器件的雪崩电流和雪崩电压测试需求确定。

10、根据本发明的另一方面,提供了一种半导体器件的uis测试方法,可以通过上述半导体器件的uis测试电路实现,包括:

11、控制第一开关管和第一陪测管导通,使电容、第一开关管、电感和第一陪测管构成电感储能回路;

12、控制第一开关管关断,第二陪测管导通,延时第一预设时间后控制第一陪测管关断,使续流二极管、电感和第二陪测管构成电感续流回路;

13、延时第二预设时间后控制第二陪测管关断,使续流二极管、电感和被测器件构成电感放电回路。

14、可选地,在本发明提供的半导体器件的uis测试方法中,可以根据被测器件的雪崩电流最大值确定并联的第一陪测管的数量;根据被测器件的雪崩电压最大值确定串联的第二陪测管的数量。

15、根据本发明提供的半导体器件的uis测试电路和测试方法,通过两个陪测管回路分别承担导通损耗和关断损耗(传统uis测试中,陪测管需要承担同时导通损耗和关断损耗),能够降低uis测试过程中的器件温升,便于扩充电感电流和雪崩电压,降低uis测试成本。

16、上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

技术特征:

1.一种半导体器件的uis测试电路,包括:电源、电容、第一开关管、电感、续流二极管、被测器件和陪测管电路,其特征在于,所述陪测管电路包括并联的第一陪测管和第二陪测管,第一陪测管为高压单管,第二陪测管为低压单管;

2.根据权利要求1所述的半导体器件的uis测试电路,其特征在于,所述第一陪测管和第二陪测管为采用硅或碳化硅材料的单管器件,所述第一陪测管能够承受的电压范围高于所述第二陪测管能够承受的电压范围,所述被测器件为mosfet管或igbt管。

3.根据权利要求1所述的半导体器件的uis测试电路,其特征在于,所述uis测试电路还包括时序控制电路,所述时序控制电路用于控制所述第一开关管、第一陪测管、第二陪测管的导通和关断。

4.根据权利要求3所述的半导体器件的uis测试电路,其特征在于,所述时序控制电路用于在第一开关管关断时,控制所述第一陪测管和第二陪测管导通,延迟第一预设时间后控制所述第一陪测管关断,延迟第二预设时间后控制所述第二陪测管关断,所述第一预设时间和所述第二预设时间为微秒级。

5.根据权利要求4所述的半导体器件的uis测试电路,其特征在于,当所述第一开关管和第一陪测管导通时,所述电容、第一开关管、电感、第一陪测管构成电感储能回路;当所述第一开关管和第一陪测管关断、第二陪测管导通时,所述续流二极管、电感、第二陪测管构成电感续流回路;当第一开关管、第一陪测管、第二陪测管关断时,所述续流二极管、电感和被测器件构成电感放电回路。

6.根据权利要求1所述的半导体器件的uis测试电路,其特征在于,所述陪测管电路包括并联的第一数量的第一陪测管和串联的第二数量的第二陪测管,所述第一数量和第二数量根据被测器件的雪崩电流和雪崩电压测试需求确定。

7.一种半导体器件的uis测试方法,用于通过如权利要求1-6任意一项中所述的半导体器件的uis测试电路实现,其特征在于,包括:

8.根据权利要求7所述的半导体器件的uis测试方法,其特征在于,还包括:

技术总结

本申请涉及半导体检测领域,公开了一种半导体器件的UIS测试电路和UIS测试方法,该UIS测试电路包括:电源、电容、第一开关管、电感、续流二极管、被测器件和陪测管电路,其中,陪测管电路包括并联的第一陪测管和第二陪测管,第一陪测管为高压单管,第二陪测管为低压单管;第一陪测管、第二陪测管和被测器件并联,电感的一端分别连接第一开关管、续流二极管,另一端分别连接第一陪测管、第二陪测管和被测器件的一端;电容并联在电源两侧,用于储能并提供电压源,电容的一端连接第一开关管,另一端分别连接续流二极管、第一陪测管、第二陪测管、被测器件的另一端。本方案能够降低陪测管温升,便于根据器件测试需求进行扩充,降低UIS测试成本。

技术研发人员:赵旭,毛赛君,刘弘耀

受保护的技术使用者:忱芯电子(苏州)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!