芯片内部信号监测方法、设备、系统及存储介质与流程

本发明涉及集成电路,具体涉及一种芯片内部信号监测方法、设备、系统及存储介质。

背景技术:

1、芯片在完成生产、封装后,会变成一个内部信号无法直接观测的“黑盒”,仅有极少的可复用的io引脚上的信号可以进行测试和观测。在芯片工作异常或者测试异常时,则需要技术人员采用多路选择器来实现通过io引脚对于内部信号的观测,且各级的多路选择器之间,均采用的是全连接的方式,因此所需要的连线资源数量巨大,且布线拥塞和互连线之间的串扰,给芯片的布线、功耗及性能等可靠性的提升造成了较大阻碍。

技术实现思路

1、有鉴于此,本发明提供了一种芯片内部信号监测方法、设备、系统及存储介质,以解决现有芯片工作异常或者测试异常时,则需要技术人员采用多路选择器来实现通过io引脚对于内部信号的观测,且各级的多路选择器之间,均采用的是全连接的方式,因此所需要的连线资源数量巨大,且布线拥塞和互连线之间的串扰,给芯片的布线、功耗及性能等可靠性的提升造成了较大阻碍的问题。

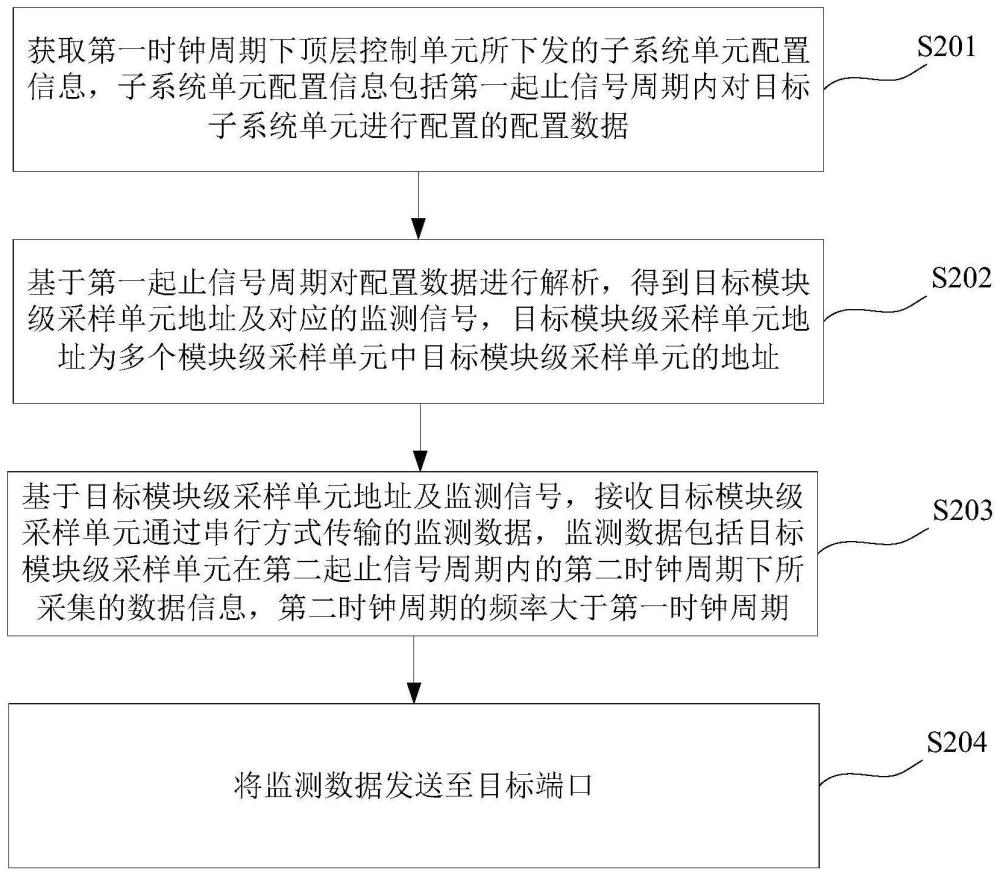

2、第一方面,本发明提供了一种芯片内部信号监测方法,应用于所述芯片内的目标子系统单元,所述芯片包括多个子系统单元,以及与所述子系统单元全连接的顶层控制单元和多个对应的模块级采样单元,所述方法包括:获取第一时钟周期下所述顶层控制单元所下发的子系统单元配置信息,所述子系统单元配置信息包括第一起止信号周期内对目标子系统单元进行配置的配置数据;基于所述第一起止信号周期对所述配置数据进行解析,得到目标模块级采样单元地址及对应的监测信号,所述目标模块级采样单元地址为多个所述模块级采样单元中目标模块级采样单元的地址;基于所述目标模块级采样单元地址及所述监测信号,接收所述目标模块级采样单元通过串行方式传输的监测数据,所述监测数据包括所述目标模块级采样单元在第二起止信号周期内的第二时钟周期下所采集的数据信息,所述第二时钟周期的频率大于所述第一时钟周期;将所述监测数据通过串行的方式发送至目标端口。通过上述过程,可以按层级进行串行输出并缓存,且采用低频的第一时钟作为子系统单元配置信息的时钟,避免了待监测信号频率过高时需要分频等操作,在保障了信号可以灵活选择的前提下,大幅降低了连线资源的占用。

3、在一些可选的实施方式中,所述获取第一时钟周期下所述顶层控制单元所下发的子系统单元配置信息,包括:

4、获取与所述顶层控制单元连接的子系统配置接口;

5、通过所述子系统配置接口接收所述顶层控制单元所发送的信号监测请求;

6、对所述信号监测请求进行解析,得到解析结果;

7、基于所述解析结果确定第一时钟周期下用于获取所述子系统单元配置信息的目标子系统单元,并进行所述子系统单元配置信息的获取。

8、在一些可选的实施方式中,所述解析结果包括第一时钟周期下的子系统单元地址,所述基于所述解析结果确定第一时钟周期下用于获取所述子系统单元配置信息的目标子系统单元,包括:

9、获取所述多个子系统单元的地址列表;

10、将所述子系统单元地址的地址长度与所述地址列表中单元地址的地址长度进行比对,得到长度比对结果;

11、当所述长度比对结果表征所述子系统单元地址的地址长度与所述单元地址的地址长度相同时,分别从所述子系统单元地址的两端截取预设步长的第一地址信息,并组合得到第一组合地址;

12、分别从所述单元地址的两端截取预设步长的第二地址信息,并组合得到第二组合地址;

13、当所述子系统单元地址两端小于所述预设步长时,对所述子系统单元地址两端进行补位,以使所述子系统单元地址两端达到所述预设步长;

14、当所述单元地址两端小于所述预设步长时,对所述单元地址两端进行补位,以使所述单元地址两端达到所述预设步长;

15、对比所述第一组合地址的内容与所述第二组合地址的内容,得到内容比对结果;

16、当所述内容比对结果表征所述第一组合地址的内容与所述第二组合地址的内容相同时,将所述单元地址作为目标单元地址;

17、基于所述目标单元地址查询所述地址列表,得到第一时钟周期下用于获取所述子系统单元配置信息的目标子系统单元。

18、在一些可选的实施方式中,所述基于所述目标模块级采样单元地址及所述监测信号,接收所述目标模块级采样单元通过串行方式传输的监测数据,包括:

19、基于所述目标模块级采样单元地址及所述监测信号,取消对所述目标模块级采样单元所采集的监测数据的屏蔽,以进行所述监测数据的接收;

20、当接收到的所述监测数据的数据量等于第一数据量阈值时,再次对所述目标模块级采样单元通过串行方式所发送的监测数据进行屏蔽,并生成一数据屏蔽标签,所述目标模块级采样单元采用串行的方式输出所述监测数据;

21、当所述第一数据量阈值的所述监测数据全部从所述目标子系统单元输出时,取消对所述监测数据的屏蔽,并更新所述数据屏蔽标签。

22、在一些可选的实施方式中,所述取消对所述目标模块级采样单元所采集的监测数据的屏蔽,以进行所述监测数据的接收,包括:

23、获取第三时钟周期下所述目标模块级采样单元所发送的监测数据,所述第三时钟的频率大于所述第二时钟;

24、在第三起止信号周期内对所述监测数据进行接收并进行数据量统计。

25、在一些可选的实施方式中,所述芯片还包括与所述子系统单元通信连接的顶层输出单元,所述将所述监测数据通过串行的方式发送至目标端口,包括:

26、在所述第三时钟周期下将所述监测数据以串行的方式发送至所述顶层输出;

27、当发送至所述顶层输出单元监测数据的数据量等于第二数据量阈值时,将所述顶层输出单元的空标识置为空,停止所述监测数据的写入,并将所述监测数据通过串行的方式发送至目标端口;

28、当所述顶层输出单元的空标识为非空时,继续所述监测数据的写入。

29、在一些可选的实施方式中,所述停止所述监测数据的写入,包括:

30、获取第三时钟周期下所述目标子系统单元所发送的监测数据;

31、在第四起止信号周期内对所述监测数据进行接收并进行数据量统计。

32、第二方面,本发明提供了一种芯片内部信号监测装置,所述装置包括:多个子系统单元,以及与所述子系统单元通信连接的顶层控制单元和多个对应的模块级采样单元;其中,所述顶层控制单元,用于在第一时钟周期下进行子系统单元配置信息下发,所述子系统单元配置信息包括第一起止信号周期内对目标子系统单元进行配置的配置数据;所述子系统单元,用于基于所述第一起止信号周期对所述配置数据进行解析,得到目标模块级采样单元地址及对应的监测信号,所述目标模块级采样单元地址为多个所述模块级采样单元中目标模块级采样单元的地址;所述模块级采样单元,用于进行监测数据的采集,所述监测数据包括所述目标模块级采样单元在第二起止信号周期内的第二时钟周期下所采集的数据信息,所述第二时钟的频率大于所述第一时钟;所述子系统单元,还用于基于所述目标模块级采样单元地址及所述监测信号,接收所述目标模块级采样单元通过串行方式传输的所采集的监测数据。可以按层级进行串行输出并缓存,且采用低频的第一时钟作为子系统单元配置信息的时钟,避免了待监测信号频率过高时需要分频等操作,在保障了信号可以灵活选择的前提下,大幅降低了连线资源的占用。

33、在一些可选的实施方式中,所述装置还包括与所述子系统单元通信连接的顶层输出单元;所述顶层输出单元,用于接收在所述子系统单元在第三时钟周期下以串行方式所发送的所述监测数据,并将所述监测数据通过串行的方式发送至目标端口;所述顶层输出单元包括依次连接的顶层串并转换模块、顶层掩码寄存器、顶层缓存寄存器堆及顶层端口输出模块;其中,所述顶层串并转换模块的输入端与所述串行输出模块的输出端连接。

34、第三方面,本发明提供了一种芯片,包括:

35、上述的芯片内部信号的监测装置,

36、片上处理器,与所述顶层控制单元连接,所述片上处理器用于与所述芯片内部信号的监测装置通信连接,并接收所述监测数据。

37、第四方面,本发明提供了一种计算机可读存储介质,该计算机可读存储介质上存储有计算机指令,计算机指令用于使计算机执行上述第一方面或其对应的任一实施方式的芯片内部信号监测方法。

- 还没有人留言评论。精彩留言会获得点赞!