一种检测不良电导体二维材料单层薄膜覆盖度的方法

本发明涉及纳米材料检测,尤其涉及一种检测不良电导体二维材料单层薄膜覆盖度的方法。

背景技术:

1、纳米材料与宏观材料相比,因其存在表面与界面效应、小尺寸效应以及宏观量子隧道效应的存在,从而在力、电、磁和热等方面都表现出了奇特的性质。二维纳米材料由于具有独特的二维结构、晶体完整度好、机械柔韧性高、比表面积大以及导电性优异等特点而成为传感、电池、医疗等多领域的热门材料。

2、二维纳米材料可以通过纳米技术(例如:langmuir-blodgett镀膜沉积、旋涂、自组装或电泳)沉积在基底表面上,同时通过控制工艺参数可以控制二维纳米材料在基底表面上的沉积情况,这些纳米薄膜在晶体薄膜生长以及电子待测结构制造等领域都有极大的应用优势。但是所得二维纳米材料薄膜的覆盖度很难获取,限制了该类材料的实际应用。目前对于纳米材料的检测手段还十分有限,存在着很大的局限性,使用原子力显微镜(afm)、扫描电子显微镜(sem)和透射电子显微镜(tem)等检测手段也只能对某一微小区域进行检测,其中使用sem检测纳米材料时由于会将入射电子轰击到样品的表面,从而会对材料造成损害。亟需一种能够在大面积范围内对二维纳米材料薄膜覆盖度进行无损检测的方法。

3、为此,本发明提供一种检测不良电导体二维材料单层薄膜覆盖度的方法。

技术实现思路

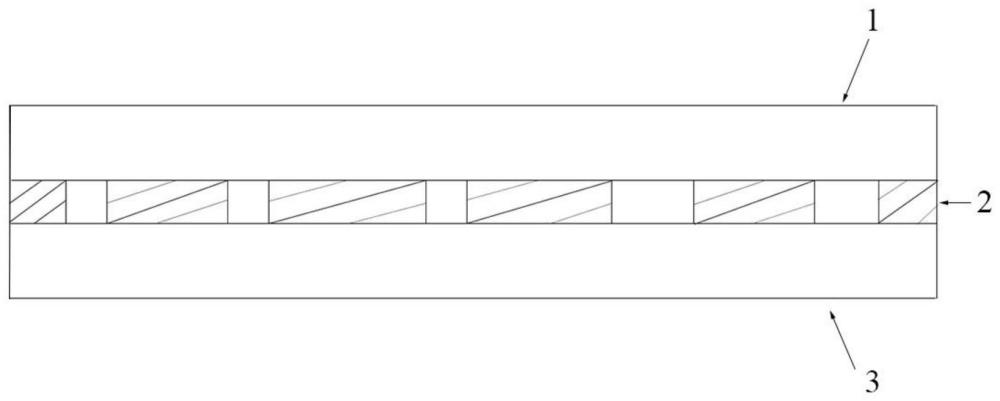

1、为了解决上述现有技术中针对目前二维纳米材料薄膜大面积范围检测的难题,本发明提供一种检测不良电导体二维材料单层薄膜覆盖度的方法。本发明通过将不良电导体的待测二维材料沉积于良导电基底上,形成表面沉积有二维材料单层薄膜的待测基底;再在所述待测基底上平行覆盖一个导电基底,使导电基底与所述二维材料单层薄膜相接触,封装以形成由两个导电基底夹持的三明治结构的待测结构,该待测结构的理论等效电路是由两个导电基底的电阻和两导电基底之间接触电阻串联而成,由于二维材料本身是不良导体,待测结构接触电阻远大于两个导电基底本身电阻,待测结构随压力的增加而产生的电流响应主要由接触电阻变化引起,故待测结构的总电阻近似为接触电阻,进而能够通过测试上述待测结构的压力-电流响应曲线,通过结合理论模型公式对其拟合,以获得最终薄膜覆盖度。

2、本发明的一种检测不良电导体二维材料单层薄膜覆盖度的方法是通过以下技术方案实现的:

3、一种检测不良电导体二维材料单层薄膜覆盖度的方法,包括以下步骤:

4、将待测二维材料沉积于导电基底a上,形成表面沉积有二维材料单层薄膜的待测基底;随后,在所述待测基底上平行覆盖导电基底b,使导电基底b与所述二维材料单层薄膜相接触,封装处理,以形成由上至下依次为导电基底b、二维材料单层薄膜、导电基底a的三明治结构的待测结构,即获得待测结构;

5、其中,所述导电基底a为良导电基底;

6、在施加电压的条件下,以恒定的压缩速率下对所述待测结构均匀施加压力,记录所述待测结构的电流随受到的压力的变化,得到压力-电流响应数据;

7、利用理论模型公式对得到的压力-电流响应数据进行拟合,拟合得出二维材料单层薄膜的压力-电流响应曲线,拟合度r2>0.98000;以拟合结果得到的amax与二维材料单层薄膜与所述导电基底b的重叠面积的比值作为薄膜覆盖度:

8、所述理论模型公式为:

9、其中,amax为两个导电基底之间穿过二维材料单层薄膜的最大接触面积,r是反映灵敏度的参数,p0为压力阈值,u为电压,ρ为接触电阻电阻率,i为待测结构响应电流。

10、优选地,所述封装处理采用聚酰亚胺胶带进行封装。

11、优选地,所述二维材料单层薄膜为不良电导体。

12、优选地,所述二维材料单层薄膜为非连续的半导体或非连续的绝缘体材料。

13、优选地,所述良导电基底为ni/si、ito/pet中的任意一种。

14、优选地,所述导电基底b为柔性基底。

15、优选地,所述柔性基底为ito/pet。

16、优选地,测试过程中,施加的电压为0.5~1.5v。

17、优选地,对待测结构均匀施加压力,且所述压缩速率为5~25mm/min。

18、本发明与现有技术相比,具有以下有益效果:

19、本发明通过将待测二维材料沉积于导电基底a上,形成表面沉积有二维材料单层薄膜的待测基底;再在所述待测基底上平行覆盖一个导电基底b,使导电基底b与所述二维材料单层薄膜相接触,封装以形成由上至下依次为导电基底b、二维材料单层薄膜、导电基底a的三明治结构的待测结构。本发明的构思基于该待测结构的工作原理,当该待测结构受到压力时,待测结构中的导电基底b发生变形从而穿过不连续的二维材料单层薄膜与导电基底a发生接触,从而产生电流的响应。并且具有该结构的待测结构导电基底b与导电基底a之间的接触面积会随着压力的增加而增加,待测结构产生的电流响应也会随之增加,直至导电基底b在压力的作用下穿过不连续的二维材料单层薄膜与导电基底a之间的接触面积达到饱和,故待测结构的理论等效电路是由两个导电基底的电阻和两导电基底之间接触电阻串联而成,由于二维材料本身是不良导体,待测结构接触电阻远大于两个导电基底本身电阻,待测结构随压力的增加而产生的电流响应主要由接触电阻变化引起,故待测结构的总电阻近似为接触电阻,进而能够通过测试上述待测结构的压力-电流响应曲线,通过结合理论模型公式对其拟合,以获得最终薄膜覆盖度。

20、本发明的检测方法能够通过理论模型公式对待测结构的压力-电流数据拟合来检测二维材料单层薄膜的覆盖度,且本发明的检测方法能够满足在大面积范围(厘米级)内检测二维材料单层薄膜的覆盖度,对比目前现有的检测手段的检测范围(微米级)具有很大的优势;并且检测过程中不会对二维材料单层薄膜造成损伤,不会对薄膜进一步的应用造成影响;而且测试过程简单,成本低,没有复杂的测试步骤,便于操作且检测准确度高。

技术特征:

1.一种检测不良电导体二维材料单层薄膜覆盖度的方法,其特征在于,包括以下步骤:

2.如权利要求1所述的方法,其特征在于,所述封装处理采用聚酰亚胺胶带进行封装。

3.如权利要求1所述的方法,其特征在于,所述二维材料单层薄膜为不良电导体。

4.如权利要求3所述的方法,其特征在于,所述二维材料单层薄膜为非连续的半导体或非连续的绝缘体材料。

5.如权利要求1所述的方法,其特征在于,所述良导电基底为ni/si、ito/pet中的任意一种。

6.如权利要求1所述的方法,其特征在于,所述导电基底b为柔性基底。

7.如权利要求6所述的方法,其特征在于,所述柔性基底为ito/pet。

8.如权利要求1所述的方法,其特征在于,施加的电压为0.5~1.5v。

9.如权利要求1所述的方法,其特征在于,所述压缩速率为5~25mm/min。

技术总结

本发明属于纳米材料检测技术领域,公开一种检测不良电导体二维材料单层薄膜覆盖度的方法,包括以下步骤:将待测二维材料沉积于导电基底A上,形成表面沉积有二维材料单层薄膜的待测基底;在待测基底上平行覆盖导电基底B,封装处理,以形成三明治结构的结构;在一定电压条件下,以恒定的压缩速率下对所述待测结构结构均匀施加压力,得到压力‑电流响应曲线;利用理论模型公式对得到的压力‑电流响应数据进行拟合,拟合得出二维材料单层薄膜的覆盖面积;检验拟合结果,选取拟合度R<supgt;2</supgt;>0.98000的覆盖率作为最终薄膜覆盖度。本发明的检测方法能够检测大面积范围内二维材料单层薄膜的覆盖度。

技术研发人员:原会雨,汤桂君,殷柯柯

受保护的技术使用者:郑州大学

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!