用于测试开漏芯片的方法及装置、集成电路自动测试机与流程

本申请涉及芯片测试,例如涉及一种用于测试开漏芯片的方法及装置、集成电路自动测试机。

背景技术:

1、目前,芯片的结构越来越复杂,随着对芯片性能的要求越来越高,芯片在测试过程中需要测试的项目也越来越多。open drain(开漏)芯片在测试过程中需要上拉开漏管脚,使得开漏管脚可以输出高电平,从而使得芯片能够正常通信,实现open drain芯片的通信功能测试。

2、为了上拉open drain芯片的开漏管脚,相关技术中利用ate(automatic testequipment,集成电路自动测试机)进行测试,通过在针卡对应管脚或者机台lb(loadboard,负载板)上加定值电阻的方式来实现开漏管脚的上拉,使得开漏管脚可以输出高电平,进而进行open drain芯片的通信功能测试。

3、在实现本公开实施例的过程中,发现相关技术中至少存在如下问题:

4、不同的芯片以及不同的测试项目对于上拉的需求不同,采用在针卡对应管脚或lb外挂的电阻都为定值电阻,为了满足测试过程中对于上拉的不同需求,采用相关技术测试不同的芯片或项目时,可能需要外挂不同阻值的电阻,降低了芯片测试的效率,也增加了测试的成本。

5、需要说明的是,在上述背景技术部分公开的信息仅用于加强对本申请的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、为了对披露的实施例的一些方面有基本的理解,下面给出了简单的概括。所述概括不是泛泛评述,也不是要确定关键/重要组成元素或描绘这些实施例的保护范围,而是作为后面的详细说明的序言。

2、本公开实施例提供了一种用于测试开漏芯片的方法及装置、集成电路自动测试机,能够提高开漏芯片测试的效率,也能够降低开漏芯片的测试成本。

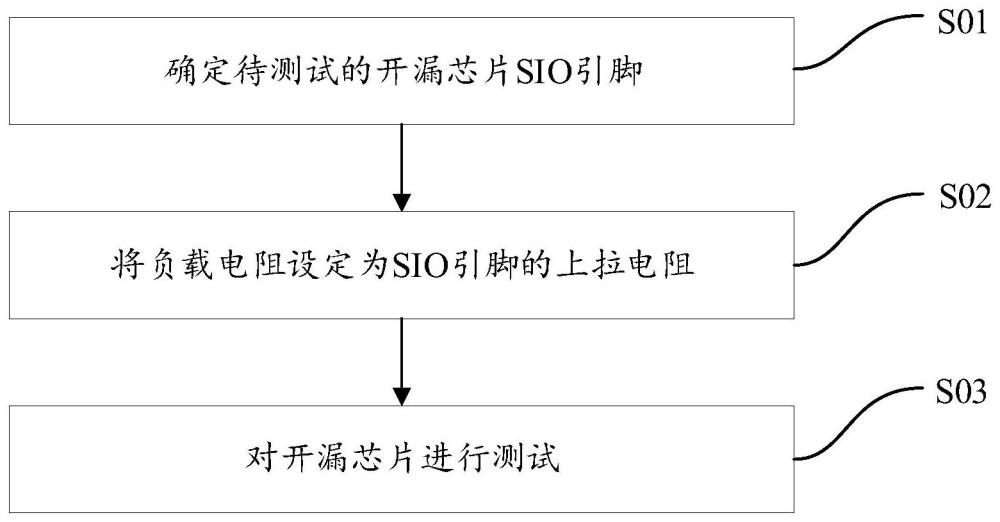

3、在一些实施例中,所述方法应用于ate,ate具有负载电阻,包括:确定待测试的开漏芯片sio(serial input/output,串行输入/输出)引脚;将负载电阻设定为sio引脚的上拉电阻;对开漏芯片进行测试。

4、可选地,负载电阻包括多个可选的电阻值。

5、可选地,将负载电阻设定为sio引脚的上拉电阻,包括:获取推荐阻值;将负载电阻设定为与推荐阻值相对应的电阻值。

6、可选地,对开漏芯片进行测试,包括:获取测试数据,其中,测试数据包括上电电压、时钟频率和预测测试值;根据测试数据测试开漏芯片,获得输出结果;将输出结果与预测测试值进行对比,获得测试结果。

7、可选地,根据测试数据测试开漏芯片,包括:调用测试程序,其中,测试程序包括上电函数、时钟函数和通信功能测试向量;将上电电压输入上电函数,使得开漏芯片和负载电阻通电;在开漏芯片和负载电阻通电的情况下,输入通信功能验证向量,获得输出结果。

8、可选地,将输出结果与预测测试值进行对比,包括:将时钟频率输入时钟函数;根据时钟函数,对输出结果进行采样,获得第一测试值;将第一测试值与预测测试值进行对比,获得第一测试结果。

9、可选地,根据时钟函数,对输出结果进行采样,包括:根据时钟函数,获取第一采样点;根据第一采样点,对输出结果进行采样。

10、在一些实施例中,所述方法还包括:根据时钟函数,获取第二采样点;根据第二采样点,对输出结果进行采样,获得第二测试值;将第二测试值与预测测试值进行对比,获得第二测试结果。

11、在一些实施例中,所述装置包括:处理器和存储有程序指令的存储器,其特征在于,所述处理器被配置为在运行所述程序指令时,执行上述的用于测试开漏芯片的方法。

12、在一些实施例中,所述集成电路自动测试机包括:集成电路自动测试机本体;上述的用于测试开漏芯片的装置,安装于所述集成电路自动测试机本体。

13、本公开实施例提供的用于测试开漏芯片的方法及装置、集成电路自动测试机,可以实现以下技术效果:

14、本公开实施例通过获取负载电阻的推荐阻值,使得ate能够根据推荐阻值选取对应的负载电阻,进而能够在开漏芯片的开漏引脚增加负载电阻,实现开漏芯片的测试。相较于相关技术,本公开实施例能够利用ate中自带的负载电阻,不需要在针卡对应管脚或者机台lb上加定值电阻,也能够实现芯片电压的上拉,使得芯片能够输出高电平,进而完成对芯片的测试。因此,本公开实施例在芯片测试过程中无需增加额外的定值电阻,提高了开漏芯片测试的效率,降低了开漏芯片测试的成本。

15、以上的总体描述和下文中的描述仅是示例性和解释性的,不用于限制本申请。

技术特征:

1.一种用于测试开漏芯片的方法,应用于集成电路自动测试机ate,ate具有负载电阻,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,负载电阻包括多个可选的电阻值。

3.根据权利要求1所述的方法,其特征在于,将负载电阻设定为sio引脚的上拉电阻,包括:

4.根据权利要求1所述的方法,其特征在于,对开漏芯片进行测试,包括:

5.根据权利要求4所述的方法,其特征在于,根据测试数据测试开漏芯片,包括:

6.根据权利要求5所述的方法,其特征在于,将输出结果与预测测试值进行对比,包括:

7.根据权利要求6所述的方法,其特征在于,根据时钟函数,对输出结果进行采样,包括:

8.根据权利要求5至7任一项所述的方法,其特征在于,还包括:

9.一种用于测试开漏芯片的装置,包括处理器和存储有程序指令的存储器,其特征在于,所述处理器被配置为在运行所述程序指令时,执行如权利要求1至8任一项所述的用于测试开漏芯片的方法。

10.一种集成电路自动测试机,其特征在于,包括:

技术总结

本申请涉及芯片测试技术领域,公开一种用于测试开漏芯片的方法,包括:确定待测试的开漏芯片SIO引脚;将负载电阻设定为SIO引脚的上拉电阻;对开漏芯片进行测试。通过获取负载电阻的推荐阻值,使得ATE能够根据推荐阻值选取对应的负载电阻,进而能够在开漏芯片的开漏引脚增加负载电阻,实现开漏芯片的测试。因此,本公开实施例在芯片测试过程中无需增加额外的定值电阻,提高了开漏芯片测试的效率,降低了开漏芯片测试的成本。本申请还公开一种用于测试开漏芯片的装置及集成电路自动测试机。

技术研发人员:金梦辉,邹欢

受保护的技术使用者:紫光同芯微电子有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!