一种比例读出电路及MEMS电容型加速度计的制作方法

本发明涉及加速度计领域,具体涉及一种比例读出电路及mems电容型加速度计。

背景技术:

1、mems(micro-electro-mechanical system微机电系统)电容型加速度计在汽车和物联网的监测系统中发挥着重要作用。例如,感应汽车事故引起的加速度,以触发安全气囊;感应地震引起的加速度,以自动关闭天然气管道,防止火灾。mems电容型加速度计还可以用于生物和工业测量的压力传感器和液位监测仪等装置中。

2、mems电容型加速度计的开环读出电路是基于电压控制的δc接口电路,其通过测量质量块位移变化导致的传感电容的电容差值来测量加速度信号。δc接口电路具有成本低、功耗低的优势。该δc接口电路仅需要一个传感模块和一个运算放大器。并且,相较于闭环加速度计的δc接口电路,开环加速度计的δc接口电路不需要高增益设计和环路补偿设计。但是,由于开环加速度计的δc接口电路的传感模块的传递函数是反比例函数,且读出结构的线性度受到静电力调制的影响,从而导致线性度差的问题,且非线性度误差也随着输入加速度信号的增大而增大,从而使开环读出电路的线性范围受限。

3、为了解决线性度差和线性范围受限的问题,目前常见的mems电容型加速度计是采用电荷控制的具有比例传递函数的全差分结构接口电路来实现。具有比例传递函数的全差分结构接口电路能够很好地抵消传感模块的反比例函数特性,但是所采用的全差分结构接口电路需要两个传感模块,增加了制造成本。并且,由于全差分结构接口电路的运算放大器输出摆幅的限制,mems电容型加速度计的开环读出电路能够输出的加速度信号的线性范围受限。

技术实现思路

1、本发明所要解决的技术问题是提供一种比例读出电路及mems电容型加速度计,可以降低制造成本以及减少由于静电力调制而引起的非线性误差。

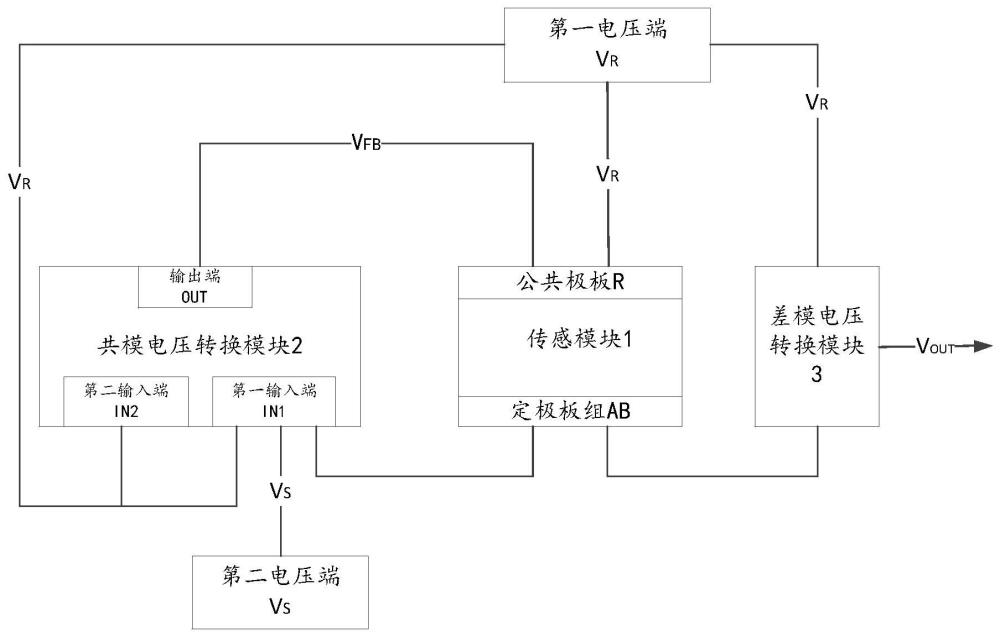

2、本发明解决上述技术问题的技术方案如下:一种比例读出电路,包括:

3、用于提供参考电压的第一电压端和用于提供激励电压的第二电压端;

4、传感模块和共模电压转换模块,其中所述传感模块包括公共极板和定极板组;所述公共极板交替连接所述第一电压端或所述共模电压转换模块的输出端;所述共模电压转换模块包括第一输入端和第二输入端;所述第一输入端连接所述定极板组,且交替连接所述第一电压端或所述第二电压端;所述第二输入端连接所述第一电压端;

5、在第一时钟阶段,基于所述共模电压转换模块接入所述参考电压,通过所述传感模块根据所述参考电压将外部加速度信号转换为初步传感电容信号;及在第二时钟阶段,通过所述共模电压转换模块根据所述激励电压,获取所述初步传感电容信号中的共模电压,且产生反馈电压输出,进而使所述传感模块在所述参考电压和所述反馈电压的交替激励下,根据所述共模电压将外部加速度信号转换为最终传感电容信号;

6、差模电压转换模块,连接所述定极板组及所述第一电压端,在所述第一时钟阶段和所述第二时钟阶段的交替下,并基于所述参考电压,用于对所述初步传感电容信号和所述最终传感电容信号交替进行差分转换,以生成与外部加速度信号成比例的差模输出电压。

7、在上述技术方案的基础上,本发明还可以做如下改进。

8、进一步,所述比例读出电路还包括非交叠时钟模块,用于在所述第一时钟阶段产生第一时钟信号,和在所述第二时钟阶段产生第二时钟信号;所述共模电压转换模块包括:

9、第一开关组和反馈电容组,其中所述第一开关组的一端连接所述第一电压端和所述第二电压端;所述反馈电容组连接于所述第一开关组的另一端和所述第一输入端之间;所述第一开关组用于在所述第一时钟信号和所述第二时钟信号的交替控制下,使所述参考电压和所述激励电压交替激励所述反馈电容组;

10、运算放大器,其正向输入端连接所述第一电压端,负向输入端连接所述反馈电容组和所述定极板组,所述运算放大器用于根据受激励的所述反馈电容和所述初步传感电容信号,以产生所述共模电压,并根据所述共模电压和所述参考电压,以产生所述反馈电压;

11、第二开关组,其一端连接所述第一电压端和所述运算放大器的输出端,另一端连接所述公共极板,用于在所述第一时钟信号和所述第二时钟信号的交替控制下,使所述参考电压和所述反馈电压交替激励所述传感模块的公共极板。

12、进一步,所述非交叠时钟模块还用于在第三时钟阶段产生第三时钟信号和在第四时钟阶段产生第四时钟信号;所述共模电压转换模块还包括第一输出摆幅增强网络和第一增益补偿网络;其中,所述第一摆幅增强网络连接所述运算放大器的输出端、所述第二开关组,用于在所述第二时钟信号、所述第三时钟信号和所述第四时钟信号的交替控制下,增强所述运算放大器的输出摆幅;所述第一增益补偿网络连接所述运算放大器的负向输入端及输出端,用于在所述第一时钟信号和所述第二时钟信号的交替控制下,补偿所述运算放大器的增益。

13、进一步,所述定极板组包括第一定极板和第二定极板;

14、所述反馈电容组包括第一反馈电容和第二反馈电容;所述第一反馈电容的一端连接所述第一定极板,所述第二反馈电容的一端连接所述第二定极板,所述第一反馈电容的另一端和所述第二反馈电容的另一端共同连接至所述第一开关组;

15、所述第一开关组包括第一开关和第二开关;所述第一开关连接于所述第一反馈电容和所述第二反馈电容的另一端,与所述第一电压端之间,用于根据所述第一时钟信号,使所述参考电压激励所述第一反馈电容以及所述第二反馈电容;所述第二开关连接于第一反馈电容和第二反馈电容的另一端,与所述第二电压端之间,用于根据所述第二时钟信号,使所述激励电压激励所述第一反馈电容以及所述第二反馈电容;

16、所述第二开关组包括第三开关和第四开关;所述第三开关连接于所述公共极板与所述运算放大器的输出端之间,用于根据所述第二时钟信号,使所述反馈电压激励所述公共极板;所述第四开关连接于所述公共极板与所述第一电压端之间,用于根据所述第一时钟信号,使所述参考电压激励所述公共极板。

17、进一步,所述第一输出摆幅增强网络包括:

18、受控于所述第三时钟信号的第五开关和受控于所述第四时钟信号的所述第六开关,依次串联于所述第一电压端与所述运算放大器的输出端之间;

19、受控于所述第二时钟信号的第七开关,连接于所述运算放大器的输出端和所述第一开关组之间;

20、第一辅助电容,一端连接于所述第五开关和所述第六开关之间,另一端连接于所述第七开关和所述第一开关组之间,所述第一辅助电容用于根据所述第二时钟信号、所述第三时钟信号和所述第四时钟信号,以增强所述运算放大器的输出摆幅;

21、所述第一增益补偿网络包括:

22、受控于所述第一时钟信号的第八开关,一端连接所述运算放大器的负向输入端;

23、受控于所述第二时钟信号的第九开关,一端连接所述第一电压端,另一端连接所述第八开关的另一端;

24、第一采样电容和第一保持电容;所述第一采样电容连接于所述定极板组和所述运算放大器的负向输入端之间;所述第一保持电容的一端连接于所述第八开关和所述第九开关之间,另一端连接所述运算放大器的输出端;所述第一采样电容和所述第一保持电容相互配合,以根据所述第一时钟信号和所述第二时钟信号补偿所述运算放大器的增益。

25、进一步,所述比例读出电路还包括非交叠时钟模块,用于在所述第一时钟阶段产生第一时钟信号,和在所述第二时钟阶段产生第二时钟信号;所述差模电压转换模块包括:

26、全差分运算放大器,输入端连接所述定极板组;

27、积分电容以及均受控于所述第一时钟信号的第十开关和第十一开关,所述积分电容通过所述第十开关连接于所述第一电压端和所述全差分运算放大器的输入端之间,所述第十一开关连接于所述全差分运算放大器的输入端和输出端之间,所述第十开关和所述第十一开关用于根据所述第一时钟信号,以初始化所述初步传感电容信号以及所述积分电容;

28、受控于所述第二时钟信号的第十二开关,一端连接于所述积分电容和所述第十开关之间,另一端连接所述全差分运算放大器的输出端,用于根据所述第二时钟信号,使所述定极板组上产生的最终传感电容信号流入所述积分电容,以在所述积分电容上产生差分电压;

29、所述全差分运算放大器用于对所述差分电压进行放大处理,以产生所述差分输出电压。

30、进一步,所述非交叠时钟模块还用于在第三时钟阶段产生第三时钟信号和在第四时钟阶段产生第四时钟信号;所述差模电压转换模块还包括第二输出摆幅增强网络,所述第二输出摆幅增强网络包括:

31、受控于所述第三时钟信号的第十三开关,一端连接所述第一电压端;

32、受控于所述第四时钟信号的第十四开关,一端连接所述第十三开关的另一端,另一端连接所述全差分运算放大器的输出端;

33、受控于所述第二时钟信号的第十五开关,一端连接所述全差分运算放大器的输出端;

34、第二辅助电容,一端连接于所述第十三开关和所述第十四开关之间,另一端连接于所述第十五开关的另一端,用于根据所述第二时钟信号、所述第三时钟信号和所述第四时钟信号,以增强所述全差分运算放大器的输出摆幅。

35、进一步,所述差模电压转换模块还包括第二增益补偿网络,所述第二增益补偿网络包括:

36、受控于所述第一时钟信号的第十六开关,一端连接所述第一电压端,另一端连接所述全差分运算放大器的输入端;

37、受控于所述第二时钟信号的第十七开关,一端连接所述第一电压端,另一端通过所述第十一开关连接所述全差分运算放大器的输入端;

38、第二采样电容和第二保持电容,所述第二采样电容连接于所述第十一开关和所述第十六开关之间,所述第二保持电容连接于所述第十一开关和所述全差分运算放大器的输入端之间,所述第二采样电容和所述第二保持电容相互配合,以根据所述第一时钟信号和所述第二时钟信号补偿所述全差分运算放大器的增益。

39、进一步,所述第一时钟信号和所述第二时钟信号互为反向信号,且所述第一时钟信号与所述第二时钟信号的边沿不重叠,所述第二时钟信号的有效电平时间位于所述第一时钟信号的无效电平时间内;

40、所述第三时钟信号和所述第四时钟信号互为反向信号,且所述第三时钟信号与所述第四时钟信号的边沿不重叠,所述第三时钟信号以及所述第四时钟信号的有效电平时间均位于所述第二时钟信号的有效电平时间内,所述第三时钟信号的上升沿与所述第二时钟信号的上升沿重叠,所述第四时钟信号的下降沿与所述第二时钟信号的下降沿重叠。

41、基于上述一种比例读出电路,本发明还提供一种mems电容型加速度计。

42、一种mems电容型加速度计,包括如上述所述的比例读出电路。

43、本发明的有益效果是:本发明提供的一种比例读出电路及mems电容型加速度计。比例读出电路包括用于提供参考电压的第一电压端和用于提供激励电压的第二电压端及传感模块、共模电压转换模块、差模电压转换模块。在第一时钟阶段,通过传感模块根据参考电压将外部加速度信号转换为初步传感电容信号;及在第二时钟阶段,通过共模电压转换模块根据激励电压,获取初步传感电容信号中的共模电压,且产生反馈电压输出,进而使传感模块在参考电压和反馈电压的交替激励下,根据共模电压将外部加速度信号转换为最终传感电容信号。进一步差模电压转换模块在第一时钟阶段和第二时钟阶段的交替下,并基于参考电压,对初步传感电容信号和最终传感电容信号交替进行差分转换,以生成与外部加速度信号成比例的差模输出电压。如此,通过传感模块、共模电压转换模块和差模电压转换模块共同形成全差分共模电荷控制比例读出结构,以实现传感模块的传递函数线性化,相较于传统技术中采用多个传感模块的方案,本发明中仅需单个传感模块即可实现全差分架构,有效降低制造成本;同时,在第一时钟阶段和第二时钟阶段使参考电压和随传感模块的变化而变化的反馈电压交替激励传感模块的公共极板,减少了静电力调制,从而提高了比例读出电路的线性度。

- 还没有人留言评论。精彩留言会获得点赞!