同步测试信号生成系统及同步测试信号生成方法与流程

本技术涉及器件测试,特别是涉及一种同步测试信号生成系统及同步测试信号生成方法。

背景技术:

1、常用的测试机数字板卡中,单片fpga包含pg(pattern generater,测试向量生成模块)、tg(timing generater,时序生成模块)、结果处理、外设管理等多个功能模块。这些功能模块之间互相连接,以实现数据的实时通信,产生的数据和信号具有严格的时间同步要求。然而,由于这些功能模块都集成在一片fpga中,导致fpga的资源消耗过大,且多个功能模块的信号时序相互影响难以收敛,增大了调试的时间和人力成本。

2、针对相关技术中存在的测试机数字板卡的fpga芯片资源紧张且信号时序相互影响难以收敛的问题,目前还没有提出有效的解决方案。

技术实现思路

1、在本实施例中提供了一种同步测试信号生成系统及同步测试信号生成方法,以解决相关技术中存在的测试机数字板卡的fpga芯片资源紧张且信号时序相互影响难以收敛的问题。

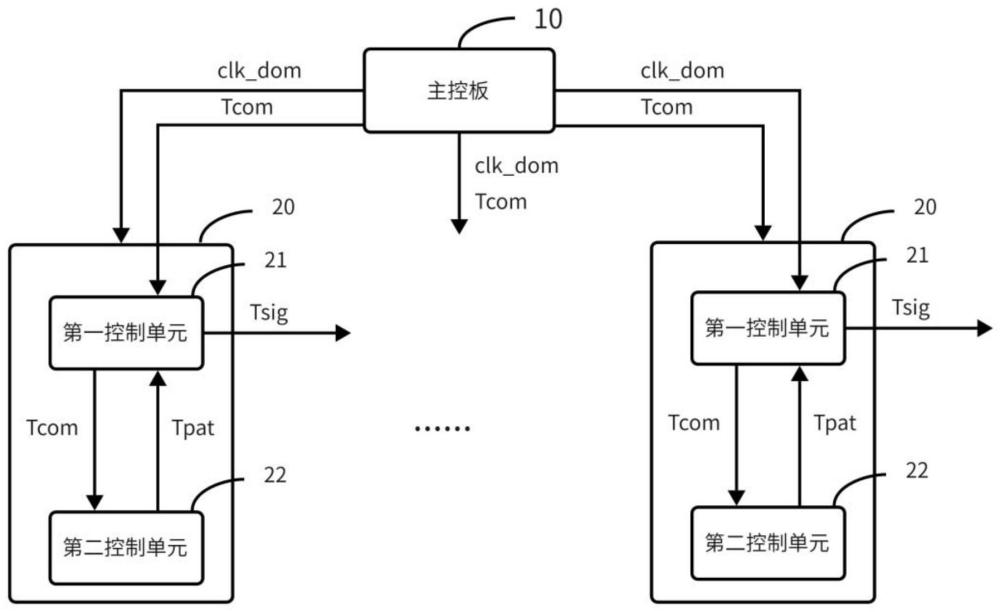

2、第一个方面,在本实施例中提供了一种同步测试信号生成系统,所述系统包括主控板和多个测试板,所述测试板包括第一控制单元和第二控制单元,

3、所述主控板向所述多个测试板发送同步时钟信号;

4、基于所述同步时钟信号,所述主控板向所述多个测试板的第一控制单元下发测试指令;

5、基于所述同步时钟信号,所述第一控制单元将所述测试指令发送至所述第二控制单元,所述第二控制单元将所述测试指令转换为对应的测试向量并发送至所述第一控制单元,所述第一控制单元将所述测试向量转换为对应的同步测试信号输出;所述多个测试板输出的多个同步测试信号用于执行被测器件的并行测试。

6、在其中的一些实施例中,所述测试板基于所述测试指令的下发时间、所述测试指令从所述第一控制单元传输到所述第二控制单元的第一传输时间、所述测试向量在所述第二控制单元内部传输的第二传输时间,以及所述测试向量从所述第二控制单元传输到所述第一控制单元的第三传输时间,确定所述同步测试信号的输出时间。

7、在其中的一些实施例中,所述第一控制单元包括内存模块,所述第二控制单元包括测试向量生成模块,

8、所述测试板基于所述测试指令的下发时间、所述测试指令从所述内存模块传输到所述测试向量生成模块的第一传输时间,确定所述测试向量生成模块的启动时间;

9、所述测试向量生成模块启动后将所述测试指令转换为对应的测试向量。

10、在其中的一些实施例中,所述第二控制单元还包括缓存模块,所述第一控制单元还包括测试信号生成模块;

11、所述缓存模块用于缓存所述测试向量生成模块生成的测试向量,并将所述测试向量按照存储顺序依次发送至所述测试信号生成模块;

12、所述测试板基于所述测试指令的下发时间、所述第一传输时间、所述测试向量从所述测试向量生成模块传输到所述缓存模块的第二传输时间,以及所述测试向量从所述缓存模块传输到所述测试信号生成模块的第三传输时间,确定所述测试信号生成模块的启动时间;

13、所述测试信号生成模块启动后将所述测试向量转换为对应的同步测试信号输出。

14、在其中的一些实施例中,所述缓存模块还用于:

15、在缓存的所述测试向量的数量达到预先设置的数量阈值的情况下,启动所述测试向量的发送。

16、在其中的一些实施例中,所述测试向量生成模块在暂停运行时,向所述缓存模块持续发送无效数据,直至所述测试向量生成模块恢复运行,所述无效数据包含无效标识;

17、所述缓存模块缓存所述无效数据并依次发送至所述测试信号生成模块;

18、所述测试信号生成模块基于所述无效标识丢弃所述无效数据。

19、在其中的一些实施例中,所述第一控制单元和第二控制单元包括同步计数模块,

20、所述同步计数模块基于所述同步时钟信号获取同步计数值;

21、所述第二控制单元基于所述测试指令的下发时间对应的同步计数值和第一传输时间对应的第一传输计数值,确定所述测试向量的输出时间对应的同步计数值;

22、所述第一控制单元基于所述测试指令的下发时间对应的同步计数值、所述第一传输时间对应的第一传输计数值、第二传输时间对应的第二传输计数值、第三传输时间对应的第三传输计数值,确定所述同步测试信号的输出时间对应的同步计数值。

23、在其中的一些实施例中,所述第一控制单元还包括与对应同步计数模块连接的内存模块和测试信号生成模块,所述第二控制单元还包括与对应同步计数模块连接的测试向量生成模块和缓存模块;

24、所述内存模块基于接收到测试指令时的同步计数值,获取基准计数值;

25、所述测试向量生成模块基于所述基准计数值和预先获取的第一传输计数值,获取第一判定值;在所述同步计数值达到所述第一判定值的情况下,启动所述测试向量输出;

26、所述测试信号生成模块基于所述基准计数值和预先获取的第一传输计数值、第二传输计数值、第三传输计数值,获取第二判定值;在所述同步计数值达到所述第二判定值的情况下,启动所述同步测试信号输出。

27、在其中的一些实施例中,所述测试板包括多个第一控制单元,

28、基于所述同步时钟信号,所述多个第一控制单元将对应的测试指令发送至所述第二控制单元,所述测试指令包含单元标识;

29、所述第二控制单元将所述测试指令转换为对应的测试向量,并基于所述单元标识将所述测试向量发送至对应的第一控制单元。

30、第二个方面,在本实施例中提供了一种同步测试信号生成方法,所述方法应用于测试板,所述测试板包括第一控制单元和第二控制单元,所述方法包括:

31、基于接收到的同步时钟信号,将所述第一控制单元接收到的测试指令发送至所述第二控制单元,所述同步时钟信号和所述测试指令由主控板下发;

32、基于所述同步时钟信号,将所述第二控制单元基于所述测试指令对应生成的测试向量发送至所述第一控制单元;

33、基于所述同步时钟信号,将所述第一控制单元基于所述测试向量对应生成的同步测试信号输出;多个测试板输出的多个所述同步测试信号用于执行被测器件的并行测试。

34、在其中的一些实施例中,所述基于所述同步时钟信号,将所述第一控制单元基于所述测试向量对应生成的同步测试信号输出包括:

35、基于所述同步时钟信号,确定所述测试指令的下发时间对应的同步计数值、所述测试指令从所述第一控制单元传输到所述第二控制单元的第一传输时间对应的第一传输计数值、所述测试向量在所述第二控制单元内部传输的第二传输时间对应的第二传输计数值,以及所述测试向量从所述第二控制单元传输到所述第一控制单元的第三传输时间对应的第三传输计数值;

36、基于所述同步计数值、第一传输计数值、第二传输计数值、第三传输计数值,确定所述同步测试信号的输出时间。

37、在其中的一些实施例中,所述基于所述同步时钟信号,将所述第二控制单元基于所述测试指令对应生成的测试向量发送至所述第一控制单元包括:

38、基于所述同步时钟信号,确定所述测试指令的下发时间对应的同步计数值、所述测试指令从所述第一控制单元传输到所述第二控制单元的第一传输时间对应的第一传输计数值;

39、基于所述同步计数值和所述第一传输计数值,确定所述第二控制单元基于所述测试指令对应生成测试向量的启动时间。

40、与相关技术相比,在本实施例中提供的同步测试信号生成系统,通过主控板向多个测试板发送同步时钟信号,为多个测试板提供用于动作同步的基准信号;通过主控板基于同步时钟信号向多个测试板的第一控制单元下发测试指令,以确保各测试板接收的测试指令同步;通过测试板的第一控制单元将测试指令发送至第二控制单元,第二控制单元将测试指令转换为对应的测试向量并发送至第一控制单元,第一控制单元再将测试向量转换为对应的同步测试信号输出,通过第一控制单元和第二控制单元分别承担生成测试向量和生成测试信号的功能,降低了对单个控制单元的资源需求并减少了信号时序的相互影响,解决了相关技术中存在的测试机数字板卡的fpga芯片资源紧张且信号时序相互影响难以收敛的问题。

41、本技术的一个或多个实施例的细节在以下附图和描述中提出,以使本技术的其他特征、目的和优点更加简明易懂。

- 还没有人留言评论。精彩留言会获得点赞!