一种射频前端阻抗控制电路的制作方法

本技术属于电子电路设计和无线通信,本技术涉及一种射频前端阻抗控制电路。

背景技术:

1、近年来,随着集成电路的不断发展,芯片规模越来越大,测试也变得越来越复杂。芯片的集成度的增大,给设计和测试带来了诸多挑战,尤其以射频电路尤为突出。随着射频电路的复杂性越来越大,量产时的筛片所需要的测试时间越来越长,导致成本也越多越大,因此内建自测试电路也表现的愈发重要。

2、为了实现内建自测试功能,通常在射频前端和天线之间增加定向耦合器,来把发射链路中功率放大器的输出信号耦合到自测试电路。自测试电路常工作在量产筛片阶段,此时射频前端不接天线,而低噪声放大器关闭后导致输入阻抗较高,因此会使得功率放大器的输出端看到较高的阻抗,导致无法推出设计的功率,会进一步导致自测试电路无法准确测试出发射链路的性能。

技术实现思路

1、实用新型目的:为解决内建自测试电路在射频电路应用中存在的问题,本实用新型公开了一种射频前端阻抗控制电路。

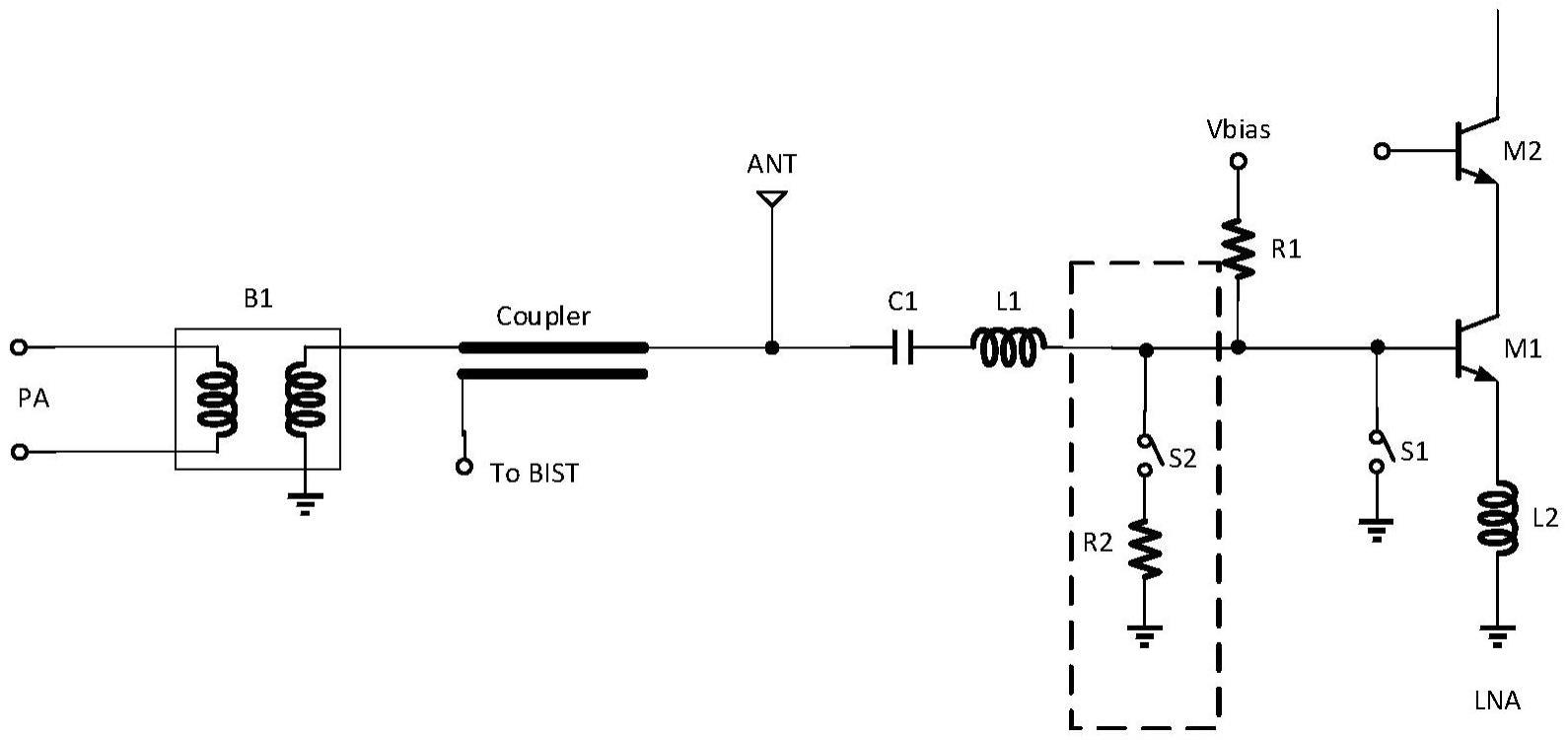

2、技术方案:一种射频前端阻抗控制电路,包括射频前端电路、天线、定向耦合器、低噪声放大器电路、第二开关和第二电阻;所述定向耦合器设置在射频前端电路与天线之间,低噪声放大器电路通过依次串联的第二开关和第二电阻接地;在进入自测试模式时,第二开关关闭,第二电阻直接接地。

3、进一步的,所述低噪声放大器电路包括:第一晶体管、第二晶体管、第一电感、电容、第二电感、第一电阻和第一开关;所述第二晶体管的发射极与第一晶体管的集电极连接,所述第一晶体管的发射极通过第二电感接地,该第一晶体管的基极第一路通过第一开关接地,第一晶体管(m1)的基极第二路通过第一电阻接入偏置电压,第一晶体管的基极第三路通过依次串联的第二开关和第二电阻接地,第一晶体管的基极第四路与第一电感的一端连接,第一电感的另一端与电容的一端连接,电容的另一端同时与天线和定向耦合器连接。

4、进一步的,所述自测试模式为天线不接入且低噪声放大器关闭的模式。

5、进一步的,在进入正常功率发射模式时,天线接入且低噪声放大器关闭,第一开关关闭,第二开关断开。

6、有益效果:本实用新型与现有技术相比,本实用新型的射频前端阻抗控制技术,可确保在内建自测试电路工作时功率放大器能正常且准确的输出设计的功率,保证自测试电路工作的准确性。

技术特征:

1.一种射频前端阻抗控制电路,其特征在于:包括射频前端电路、天线、定向耦合器、低噪声放大器电路、第二开关(s2)和第二电阻(r2);

2.根据权利要求1所述的一种射频前端阻抗控制电路,其特征在于:所述低噪声放大器电路包括:第一晶体管(m1)、第二晶体管(m2)、第一电感(l1)、电容(c1)、第二电感(l2)、第一电阻(r1)和第一开关(s1);

3.根据权利要求1所述的一种射频前端阻抗控制电路,其特征在于:所述自测试模式为天线不接入且低噪声放大器关闭的模式。

4.根据权利要求1所述的一种射频前端阻抗控制电路,其特征在于:在进入正常功率发射模式时,天线接入且低噪声放大器关闭,第一开关(s1)关闭,第二开关(s2)断开。

技术总结

本技术公开了一种射频前端阻抗控制电路,包括射频前端电路、天线、定向耦合器、低噪声放大器电路、第二开关和第二电阻;定向耦合器设置在射频前端电路与天线之间,低噪声放大器电路通过依次串联的第二开关和第二电阻接地;在进入自测试模式时,第二开关关闭,第二电阻直接接地;当进入自测试模式时,第二开关关闭,第二电阻直接接地;当从定向耦合器往接收链路看时,由于第二电阻通过第一电感进行了阻抗转换,等效的输入阻抗会等于50欧姆,因此功率放大器的负载阻抗等于50欧姆,使得功率放大器可以正常工作。

技术研发人员:尹海峰,王永利,黄家乐,李治,姜源

受保护的技术使用者:思诺威科技(无锡)有限公司

技术研发日:20230425

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!