一种低功耗的芯片电源检测电路的制作方法

本技术涉及芯片电源检测,具体涉及一种低功耗的芯片电源检测电路。

背景技术:

1、目前芯片内部都会集成电源检测电路来对芯片的电源电压进行检测,从而判断芯片的电源电压是否过低和是否符合要求,以及在芯片电源电压过低时输出异常信号和芯片电源电压符合要求时输出正常信号。其中异常信号用于让芯片处于复位状态,防止芯片数字电路程序跑飞和进入错误状态;正常信号用于解除芯片的复位状态,让芯片能够正常工作。

2、对于现有的烟雾检测和智能水表等领域,由于需要几年更换一次电池,所以对芯片的功耗提出了很高的要求,往往需要芯片的工作电流小于1ua,所以对内部的电源检测电路的功耗提出了很高的要求,其功耗最好是pa级别。

3、常见的复位电路有rc复位电路,虽然该电路的功耗非常低,但是仅能在芯片电源电压上升时进行检测,不能对芯片电源电压下降进行检测。另外还有通过增加基准电压模块例如带隙基准模块来提供一个稳定的参考电压,通过将该参考电压和芯片的电源电压进行比较,从而能对芯片的电源电压上升和下降都进行检测,但是这种方式存在的缺点是由于需要额外的基准电压模块,并且功耗电流较大,往往是几微安,高的话甚至达到几十微安,并不适用于低功耗芯片。

技术实现思路

1、鉴于背景技术的不足,本实用新型提供了一种低功耗的芯片电源检测电路,能低功耗的对芯片的电源电压上升和下降进行检测。

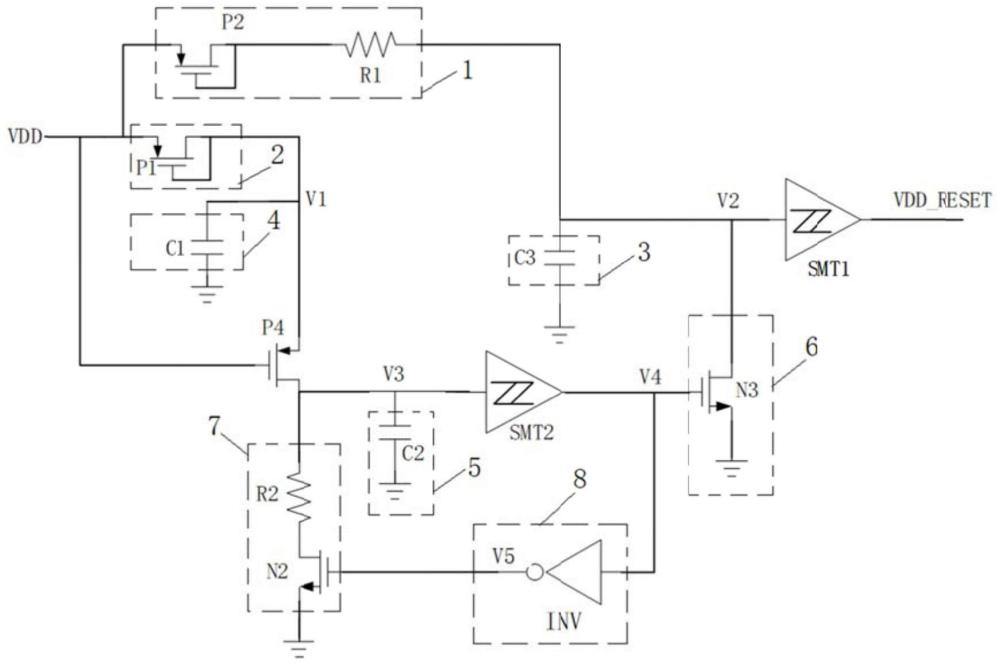

2、为解决以上技术问题,本实用新型提供了如下技术方案:一种低功耗的芯片电源检测电路,包括第一负载支路、第一施密特触发器、第二负载支路、第一储能单元、pmos管p4、第二施密特触发器、第一开关单元、第二开关单元和反相单元;

3、所述第一负载支路的输入端和第二负载支路的输入端电连接,用于输入芯片电源电压,所述第一负载支路在芯片电源电压大于第一阈值时导通,所述第二负载支路在芯片电源电压大于第二阈值时导通;

4、所述第一负载支路的输出端分别与所述第一开关单元的输入端和第一施密特触发器的输入端电连接,所述第一开关单元的输出端接地;

5、所述第二负载支路的输出端分别与第一储能单元和pmos管p4的源极电连接,pmos管p4的栅极用于输入所述芯片电源电压,pmos管p4的漏极分别与第二开关单元的输入端和第二施密特触发器的输入端电连接;

6、所述第二施密特触发器的输出端分别与第一开关单元的控制端和反相单元的输入端电连接,在输出高电平信号时驱动第一开关单元导通;反相单元的输出端与第二开关单元的控制端电连接,在输出高电平信号时驱动第二开关单元导通,第二开关单元的输出端接地。

7、在某种实施方式中,所述第一负载支路包括至少一个第二pmos管和电阻r1,每个第二pmos管的栅极与其漏极电连接;

8、当第二pmos管的数量为一个时,第二pmos管的源极用于输入所述芯片电源电压,第二pmos管的漏极与电阻r1一端电连接,电阻r1另一端为第一负载支路的输出端;

9、当第二pmos管的数量大于一时,所有第二pmos管依次串联,所述串联为前端的第二pmos管的漏极与后端的第二pmos管的源极电连接,首端第二pmos管的源极用于输入所述芯片电源电压,末端第二pmos管的漏极与电阻r1一端电连接,电阻r1另一端为第一负载支路的输出端。

10、在某种实施方式中,所述第二负载支路包括至少一个第三pmos管,每个第三pmos管的栅极与其漏极电连接;

11、当第三pmos管的数量为一个时,第三pmos管的源极用于输入所述芯片电源电压,第三pmos管的漏极为第二负载支路的输出端;

12、当第三pmos管的数量大于一时,所有第三pmos管依次串联,所述串联为前端的第三pmos管的漏极与后端的第三pmos管的源极电连接,首端第三pmos管的源极用于输入所述芯片电源电压,末端第三pmos管的漏极为第二负载支路的输出端。

13、在某种实施方式中,所述第一储能单元包括电容c1,所述第二负载支路的输出端与电容c1一端电连接,电容c1另一端接地。

14、在某种实施方式中,所述第一开关单元包括nmos管n3,nmos管n3的漏极为第一开关单元的输入端,nmos管n3的栅极为第一开关单元的控制端,nmos管n3的源极为第一开关单元的输出端。

15、在某种实施方式中,所述第二开关单元包括电阻r2和nmos管n2,电阻r2一端为第二开关单元的输入端,与pmos管p4的漏极电连接,电阻r2另一端与nmos管n2的漏极,nmos管n2的栅极为第二开关单元的控制端,nmos管n2的源极为第二开关单元的输出端。

16、在某种实施方式中,所述反相单元包括反相器inv,反相器inv的输入端为反相单元的输入端,反相器inv的输出端为反相单元的输出端。

17、在某种实施方式中,本实用新型还包括第一滤波单元和第二滤波单元,所述第一负载支路的输出端与所述第一滤波单元电连接,所述pmos管p4的漏极与第二滤波单元电连接。

18、在某种实施方式中,所述第一滤波单元包括电容c3,所述第二滤波单元包括电容c2;所述第一负载支路的输出端与电容c3一端电连接,电容c3另一端接地;pmos管p4的漏极与电容c2一端电连接,电容c2另一端接地。

19、本实用新型与现有技术相比所具有的有益效果是:对于本实用新型,当芯片电源电压上升到第一施密特触发器的翻转电压时,第一施密特触发器输出翻转,从而实现芯片电源电压上升检测;另外由于pmos管p4关断,因此在芯片电源电压上升时第一开关单元、第二开关单元、和第二滤波单元均不工作,从而能降低功耗;

20、当芯片电源电压下降至pmos管p4导通时,第二滤波单元开始充电,第二施密特触发器的输入端电压上升,当第二滤波单元的电荷使第二施密特触发器的输出翻转时,第一开关单元导通,反相单元将第二开关单元关断,而第一开关单元导通后会将第一施密特触发器的输入端的电压拉低,从而使第一施密特触发器的输出翻转,从而实现芯片电源电压下降检测。

技术特征:

1.一种低功耗的芯片电源检测电路,其特征在于,包括第一负载支路、第一施密特触发器、第二负载支路、第一储能单元、pmos管p4、第二施密特触发器、第一开关单元、第二开关单元和反相单元;

2.根据权利要求1所述的一种低功耗的芯片电源检测电路,其特征在于,所述第一负载支路包括至少一个第二pmos管和电阻r1,每个第二pmos管的栅极与其漏极电连接;

3.根据权利要求1所述的一种低功耗的芯片电源检测电路,其特征在于,所述第二负载支路包括至少一个第三pmos管,每个第三pmos管的栅极与其漏极电连接;

4.根据权利要求1所述的一种低功耗的芯片电源检测电路,其特征在于,所述第一储能单元包括电容c1,所述第二负载支路的输出端与电容c1一端电连接,电容c1另一端接地。

5.根据权利要求1所述的一种低功耗的芯片电源检测电路,其特征在于,所述第一开关单元包括nmos管n3,nmos管n3的漏极为第一开关单元的输入端,nmos管n3的栅极为第一开关单元的控制端,nmos管n3的源极为第一开关单元的输出端。

6.根据权利要求1所述的一种低功耗的芯片电源检测电路,其特征在于,所述第二开关单元包括电阻r2和nmos管n2,电阻r2一端为第二开关单元的输入端,与pmos管p4的漏极电连接,电阻r2另一端与nmos管n2的漏极,nmos管n2的栅极为第二开关单元的控制端,nmos管n2的源极为第二开关单元的输出端。

7.根据权利要求1所述的一种低功耗的芯片电源检测电路,其特征在于,所述反相单元包括反相器inv,反相器inv的输入端为反相单元的输入端,反相器inv的输出端为反相单元的输出端。

8.根据权利要求1所述的一种低功耗的芯片电源检测电路,其特征在于,还包括第一滤波单元和第二滤波单元,所述第一负载支路的输出端与所述第一滤波单元电连接,所述pmos管p4的漏极与第二滤波单元电连接。

9.根据权利要求1所述的一种低功耗的芯片电源检测电路,其特征在于,所述第一滤波单元包括电容c3,所述第二滤波单元包括电容c2;所述第一负载支路的输出端与电容c3一端电连接,电容c3另一端接地;pmos管p4的漏极与电容c2一端电连接,电容c2另一端接地。

技术总结

本技术涉及芯片电源检测技术领域,公开了一种低功耗的芯片电源检测电路,包括第一负载支路、第一施密特触发器、第二负载支路、第一储能单元、PMOS管P4、第二施密特触发器、第一开关单元、第二开关单元和反相单元;对于本技术,当芯片电源电压上升到第一施密特触发器的翻转电压时,第一施密特触发器输出翻转,从而实现芯片电源电压上升检测;另外由于PMOS管P4关断,因此在芯片电源电压上升时第一开关单元、第二开关单元、和第二滤波单元均不工作,从而能降低功耗。

技术研发人员:孙洋

受保护的技术使用者:无锡矽杰微电子有限公司

技术研发日:20230919

技术公布日:2024/4/29

- 还没有人留言评论。精彩留言会获得点赞!