一种用于边界扫描测试的延时校正处理方法、系统及平台与流程

本发明属于边界扫描测试处理,具体涉及一种用于边界扫描测试的延时校正处理方法、系统及平台。

背景技术:

1、随着芯片的集成度越来越高,待测板的连接关系越来越复杂,引脚数量越来越多,因此需要同步提高测试速率,对边界扫描测试速率的要求提出挑战。

2、在边界扫描测试中,有一种测试类型是通过jtag来产生边界扫描芯片引脚的时序,对eeprom、flash、ddr等存储芯片进行烧录或校验或读取或激励响应测试,这类测试,jtag每发送一笔数据至边界扫描寄存器,都只能使边界扫描芯片的io引脚的数据改变一次,边界扫描芯片内的io引脚与存储芯片的引脚相连,为了驱动这些存储芯片,发送数据的笔数是庞大的,需要极高的测试速率来改变边界扫描芯片的io引脚的电平进而达到驱动存储芯片引脚的目的,因此需要提升测试速率满足这一需求,降低测试时间。

3、此外,专利(申请号2023117616471)提出一种用于边界扫描测试的数据延时控制方法、系统及平台,提出的方法为一种克服延时的高速率测试方法,克服了延时的影响,进行正确的测试,该方法没有从根本上对延时进行校正,tck采集的位置在数据距离波形边缘1/2至1/4的位置不定,不能保证tck采集的位置在数据最佳的1/2的中间位置,当因tck频率太高或延时太大发生错位时,每一笔数据需要多发送一至几位,而且上位机软件和fpga都需要提取关心的数据并进行判断,在处理步骤上和人员紧密配合上更为繁琐,另外该发明也没有考虑边界扫描链内芯片之间可能加入的驱动芯片或电平转换芯片所带来的延时因素,当驱动芯片或电平转换芯片存在时,虽然能够提升测试速率,并没有达到最佳的提升速率效果。

4、因此,针对以上能够提升测试速率,并没有达到最佳的提升速率效果的技术问题缺陷,急需设计和开发一种用于边界扫描测试的延时校正处理方法、系统及平台。

技术实现思路

1、为克服上述现有技术存在的不足及困难,本发明方案提供一种用于边界扫描测试的延时校正处理方法、系统及平台,结合边界扫描驱动电路,从根本上对延时进行校正,提升边界扫描测试速率。

2、本发明的第一目的在于提供一种用于边界扫描测试的延时校正处理方法;本发明的第二目的在于提供一种用于边界扫描测试的延时校正处理系统;本发明的第三目的在于提供一种用于边界扫描测试的延时校正处理平台。

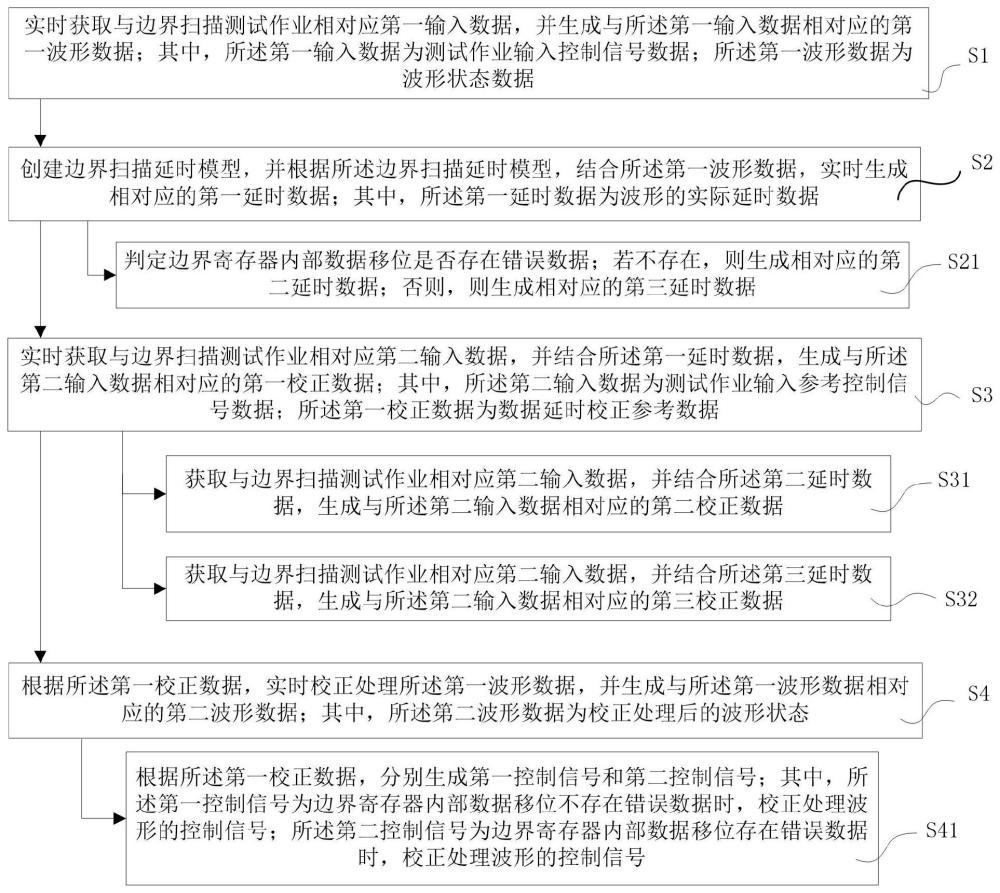

3、本发明的第一目的是这样实现的:所述方法包括如下步骤:

4、实时获取与边界扫描测试作业相对应第一输入数据,并生成与所述第一输入数据相对应的第一波形数据;其中,所述第一输入数据为测试作业输入控制信号数据;所述第一波形数据为波形状态数据;

5、创建边界扫描延时模型,并根据所述边界扫描延时模型,结合所述第一波形数据,实时生成相对应的第一延时数据;其中,所述第一延时数据为波形的实际延时数据;

6、实时获取与边界扫描测试作业相对应第二输入数据,并结合所述第一延时数据,生成与所述第二输入数据相对应的第一校正数据;其中,所述第二输入数据为测试作业输入参考控制信号数据;所述第一校正数据为数据延时校正参考数据;

7、根据所述第一校正数据,实时校正处理所述第一波形数据,并生成与所述第一波形数据相对应的第二波形数据;其中,所述第二波形数据为校正处理后的波形状态。

8、进一步地,所述测试作业输入控制信号数据为排针形式呈现的信号数据;所述信号数据包括时钟数据、状态信号数据和发送信号数据;

9、所述第一波形数据为进入边界扫描链前的波形状态数据;所述第二波形数据为进入边界扫描链前且经过校正处理的波形状态数据。

10、进一步地,所述第一延时数据包括第二延时数据和第三延时数据;

11、所述创建边界扫描延时模型,并根据所述边界扫描延时模型,结合所述第一波形数据,实时生成相对应的第一延时数据,还包括:

12、判定边界寄存器内部数据移位是否存在错误数据;若不存在,则生成相对应的第二延时数据;否则,则生成相对应的第三延时数据。

13、进一步地,所述第一校正数据包括第二校正数据和第三校正数据;

14、所述实时获取与边界扫描测试作业相对应第二输入数据,并结合所述第一延时数据,生成与所述第二输入数据相对应的第一校正数据,还包括:

15、获取与边界扫描测试作业相对应第二输入数据,并结合所述第二延时数据,生成与所述第二输入数据相对应的第二校正数据;

16、获取与边界扫描测试作业相对应第二输入数据,并结合所述第三延时数据,生成与所述第二输入数据相对应的第三校正数据。

17、进一步地,所述边界扫描延时模型中,设置有边界扫描驱动电路;

18、所述电路中包括第一控制芯片;所述第一控制芯片的ps端和第一数模转换器的输入端连接;

19、所述第一数模转换器的输出端和第一比较器的正输入端连接;所述第一比较器的输出端分别和所述第一比较器的负输入端、第三控制芯片的vref_a引脚连接;

20、所述第一控制芯片的pl端依次和第二控制芯片的b0引脚、b1引脚、b2引脚连接;所述第二控制芯片的a0引脚、a1引脚、a2引脚依次和所述第三控制芯片的b1引脚、b2引脚、b3引脚连接;所述第三控制芯片的a1引脚、a2引脚、a3引脚依次和边界扫描测试口信号端一侧连接;所述边界扫描测试口信号端另一侧和边界扫描测试链连接;

21、所述边界扫描测试链的数据输出接口和所述边界扫描测试口的数据输出接口连接;所述边界扫描测试口的数据输出接口和第二比较器的正输入端连接;所述第二比较器的输出端和所述第一控制芯片中pl端的信号接收接口连接;

22、所述第一控制芯片的pl端还设置有用于输入第二输入数据的延时预设端口。

23、进一步地,所述第一控制芯片为fpga芯片,型号为xc7z020-2clg484i;

24、所述第二控制芯片的型号为gtl2014pw;所述第三控制芯片的型号为lsf0102dcur;

25、所述第一数模转换器的型号为ad5667rbrmz-1;所述第一比较器的型号为lmv358a;所述第二比较器的型号为ltv3603。

26、进一步地,所述根据所述第一校正数据,实时校正处理所述第一波形数据,并生成与所述第一波形数据相对应的第二波形数据,还包括:

27、根据所述第一校正数据,分别生成第一控制信号和第二控制信号;其中,所述第一控制信号为边界寄存器内部数据移位不存在错误数据时,校正处理波形的控制信号;所述第二控制信号为边界寄存器内部数据移位存在错误数据时,校正处理波形的控制信号。

28、本发明的第二目的是这样实现的:所述系统应用于所述的延时校正处理方法,所述系统包括:

29、第一数据生成单元,用于实时获取与边界扫描测试作业相对应第一输入数据,并生成与所述第一输入数据相对应的第一波形数据;其中,所述第一输入数据为测试作业输入控制信号数据;所述第一波形数据为波形状态数据;

30、创建生成单元,用于创建边界扫描延时模型,并根据所述边界扫描延时模型,结合所述第一波形数据,实时生成相对应的第一延时数据;其中,所述第一延时数据为波形的实际延时数据;

31、第二数据生成单元,用于实时获取与边界扫描测试作业相对应第二输入数据,并结合所述第一延时数据,生成与所述第二输入数据相对应的第一校正数据;其中,所述第二输入数据为测试作业输入参考控制信号数据;所述第一校正数据为数据延时校正参考数据;

32、校正处理单元,用于根据所述第一校正数据,实时校正处理所述第一波形数据,并生成与所述第一波形数据相对应的第二波形数据;其中,所述第二波形数据为校正处理后的波形状态。

33、进一步地,所述测试作业输入控制信号数据为排针形式呈现的信号数据;所述信号数据包括时钟数据、状态信号数据和发送信号数据;

34、所述第一波形数据为进入边界扫描链前的波形状态数据;所述第二波形数据为进入边界扫描链前且经过校正处理的波形状态数据;

35、所述第一延时数据包括第二延时数据和第三延时数据;

36、和/或,所述创建生成单元,还包括:

37、数据判定模块,用于判定边界寄存器内部数据移位是否存在错误数据;

38、所述第一校正数据包括第二校正数据和第三校正数据;

39、和/或,所述第二数据生成单元,还包括:

40、第一生成模块,用于获取与边界扫描测试作业相对应第二输入数据,并结合所述第二延时数据,生成与所述第二输入数据相对应的第二校正数据;

41、第二生成模块,用于获取与边界扫描测试作业相对应第二输入数据,并结合所述第三延时数据,生成与所述第二输入数据相对应的第三校正数据;

42、所述边界扫描延时模型中,设置有边界扫描驱动电路;

43、所述电路中包括第一控制芯片;所述第一控制芯片的ps端和第一数模转换器的输入端连接;

44、所述第一数模转换器的输出端和第一比较器的正输入端连接;所述第一比较器的输出端分别和所述第一比较器的负输入端、第三控制芯片的vref_a引脚连接;

45、所述第一控制芯片的pl端依次和第二控制芯片的b0引脚、b1引脚、b2引脚连接;所述第二控制芯片的a0引脚、a1引脚、a2引脚依次和所述第三控制芯片的b1引脚、b2引脚、b3引脚连接;所述第三控制芯片的a1引脚、a2引脚、a3引脚依次和边界扫描测试口信号端一侧连接;所述边界扫描测试口信号端另一侧和边界扫描测试链连接;

46、所述边界扫描测试链的数据输出接口和所述边界扫描测试口的数据输出接口连接;所述边界扫描测试口的数据输出接口和第二比较器的正输入端连接;所述第二比较器的输出端和所述第一控制芯片中pl端的信号接收接口连接;

47、所述第一控制芯片的pl端还设置有用于输入第二输入数据的延时预设端口;

48、所述第一控制芯片为fpga芯片,型号为xc7z020-2clg484i;

49、所述第二控制芯片的型号为gtl2014pw;所述第三控制芯片的型号为lsf0102dcur;

50、所述第一数模转换器的型号为ad5667rbrmz-1;所述第一比较器的型号为lmv358a;所述第二比较器的型号为ltv3603;

51、和/或,所述校正处理单元,还包括:

52、第三生成模块,用于根据所述第一校正数据,分别生成第一控制信号和第二控制信号;其中,所述第一控制信号为边界寄存器内部数据移位不存在错误数据时,校正处理波形的控制信号;所述第二控制信号为边界寄存器内部数据移位存在错误数据时,校正处理波形的控制信号。

53、本发明的第三目的是这样实现的:包括处理器、存储器以及用于边界扫描测试的延时校正处理平台控制程序;其中在所述的处理器执行所述的用于边界扫描测试的延时校正处理平台控制程序,所述的用于边界扫描测试的延时校正处理平台控制程序被存储在所述存储器中,所述的用于边界扫描测试的延时校正处理平台控制程序,实现所述的用于边界扫描测试的延时校正处理方法。

54、本发明通过方法实时获取与边界扫描测试作业相对应第一输入数据,并生成与所述第一输入数据相对应的第一波形数据;其中,所述第一输入数据为测试作业输入控制信号数据;所述第一波形数据为波形状态数据;创建边界扫描延时模型,并根据所述边界扫描延时模型,结合所述第一波形数据,实时生成相对应的第一延时数据;其中,所述第一延时数据为波形的实际延时数据;实时获取与边界扫描测试作业相对应第二输入数据,并结合所述第一延时数据,生成与所述第二输入数据相对应的第一校正数据;其中,所述第二输入数据为测试作业输入参考控制信号数据;所述第一校正数据为数据延时校正参考数据;

55、根据所述第一校正数据,实时校正处理所述第一波形数据,并生成与所述第一波形数据相对应的第二波形数据;其中,所述第二波形数据为校正处理后的波形状态;以及与所述方法相应的系统、平台,结合边界扫描驱动电路,从根本上对延时进行校正,提升边界扫描测试速率。即保证tck采集的位置在数据波形中间或在波形中间微调整,数据采集更为稳定可靠,保持上位机软件读取tdo的条件不变,简化了步骤。

- 还没有人留言评论。精彩留言会获得点赞!