基于FPGA的大带宽复杂扫频干扰信号生成方法及装置

本发明属于信号生成,具体涉及一种基于fpga的大带宽复杂扫频干扰信号生成方法及装置。

背景技术:

1、当前的扫频干扰信号的生成方案原理均是利用上位机下发频率控制字,经过直接数字频率合成器(direct digital frequency synthesis,dds)生成对应频率的数字信号。

2、方案一是通过上位机更新下发的频率控制字参数,生成多频段的信号,完成扫频工作;该方案是基于dds可快速生成数字信号,完成干扰信号之间的频率跳转。但这种方案在实际工程中,极其消耗资源的调度。

3、方案二是对传统方法的一种改进,是基于dds的双向线性扫频方法。但是这种方法生成的实际扫频信号的调制形式只有三角波调制。虽然这种方法能够实现扫频信号的相位连续,并且该调制方式相较于传统的线性调制方式较为复杂,但并不能实现更加复杂调制方式,如:正弦波调制、余弦波调制等。这导致扫频干扰信号频率变化单一,扫频干扰信号极其容易被检测出来。

4、因此,当前的扫频干扰信号的产生方法产生的信号复杂度较低,导致信号容易被识别。

技术实现思路

1、本发明实施例提供了一种基于fpga的大带宽复杂扫频干扰信号生成方法及装置,可以解决当前扫频干扰信号的产生方法产生的信号复杂度较低,导致信号容易被识别的问题。

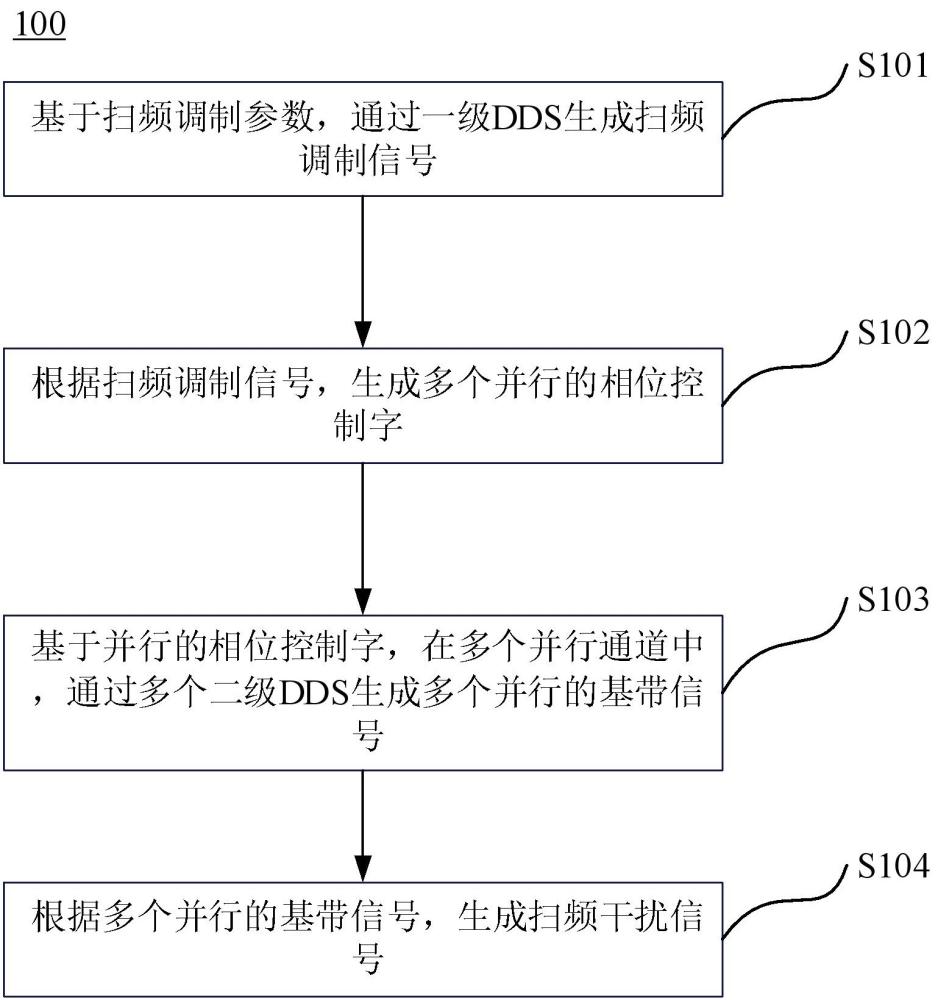

2、第一方面,本发明实施例提供的一种基于fpga的大带宽复杂扫频干扰信号生成方法,所述方法包括:

3、基于扫频调制参数,通过一级dds生成扫频调制信号;

4、根据扫频调制信号,生成多个并行的相位控制字;

5、基于并行的相位控制字,在多个并行通道中,通过多个二级dds生成多个并行的基带信号;

6、根据多个并行的基带信号,生成扫频干扰信号。

7、在第一方面的一种可能的实现方式中,扫频调制参数可以包括扫频调制函数的频率,可以将扫频调制函数的频率作为扫频调制信号的频率控制字输入至一级dds,得到扫频调制信号。

8、在第一方面的一种可能的实现方式中,可以根据扫频调制信号,确定频率控制字和初始相位控制字;根据初始相位控制字和频率控制字,确定多个并行的相位控制字。

9、在第一方面的一种可能的实现方式中,可以根据频率控制字和第时刻第个并行通道的相位控制字,确定第时刻第个并行通道的相位控制字。根据频率控制字和第时刻第个并行通道的相位控制字,确定第时刻第1个并行通道的相位控制字。

10、示例性的,,为并行通道的总数。

11、示例性的,,第时刻为扫频驻留时间内的最后一刻。

12、示例性的,第1时刻第1个并行通道的相位控制字为初始相位控制字。

13、在第一方面的一种可能的实现方式中,可以将频率控制字与第时刻第个并行通道的相位控制字之和,确定为第时刻第个并行通道的相位控制字。

14、在第一方面的一种可能的实现方式中,可以将频率控制字与第时刻第个并行通道的相位控制字之和,确定为第时刻第1个并行通道的相位控制字。

15、在第一方面的一种可能的实现方式中,可以将频率控制字和第个并行通道第时刻的相位控制字输入至第个并行通道中的二级dds,得到第个基带信号第时刻的数据;

16、在第一方面的一种可能的实现方式中,扫频驻留时间可以满足下述公式:

17、,

18、其中,为扫频驻留时间,为扫频周期,为并行通道的总数。

19、在第一方面的一种可能的实现方式中,可以分别对基带信号进行上变频处理,得到中频信号。通过与基带信号的瞬时带宽匹配的射频噪声干扰信号对中频信号进行混频处理,得到多个射频干扰信号;对多个射频干扰信号进行并串转换处理,生成扫频干扰信号。

20、第二方面,本发明实施例提供了一种基于fpga的大带宽复杂扫频干扰信号生成装置,所述装置包括处理单元、一级dds及二级dds;

21、一级dds用于基于扫频调制参数,生成扫频调制信号;

22、处理单元用于根据扫频调制信号,生成多个并行的相位控制字;

23、在装置中的多个并行通道中的二级dds用于基于并行的相位控制字,生成并行的基带信号;

24、处理单元还用于根据多个并行的基带信号,生成扫频干扰信号。

25、本发明实施例与现有技术相比存在的有益效果是:相较于只通过一级dds进行映射的传统方法,本发明提供的方法通过两级dds的映射最终得到扫频干扰信号的基带信号,能够提高扫频干扰信号的调制方式的复杂度。进一步的,通过在装置中根据串行的扫频调制参数和扫频调制信号得到并行的相位控制字,并根据并行的相位控制字生成大带宽的扫频干扰信号,无需模拟器件的参与,能够简化fpga系统的结构,降低系统复杂度。

26、以下将结合附图及实施例对本发明做进一步详细说明。

技术特征:

1.一种基于fpga的大带宽复杂扫频干扰信号生成方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,所述扫频调制参数包括扫频调制函数的频率;

3.根据权利要求2所述的方法,其特征在于,所述根据所述扫频调制信号,生成多个并行的相位控制字,包括:

4.根据权利要求3所述的方法,其特征在于,所述根据所述初始相位控制字和所述频率控制字,确定多个并行的所述相位控制字,包括:

5.根据权利要求4所述的方法,其特征在于,所述根据所述频率控制字和第时刻第个并行通道的相位控制字,确定第时刻第个并行通道的相位控制字,包括:

6.根据权利要求4所述的方法,其特征在于,所述根据所述频率控制字和第时刻第个并行通道的相位控制字,确定第时刻第1个并行通道的相位控制字,包括:

7.根据权利要求4所述的方法,其特征在于,所述基于所述并行的相位控制字,在多个并行通道中,通过多个二级dds生成多个并行的基带信号,包括:

8.根据权利要求4所述的方法,其特征在于,所述扫频驻留时间满足下述公式:

9.根据权利要求1所述的方法,其特征在于,所述根据多个并行的所述基带信号,生成扫频干扰信号,包括:

10.一种基于fpga的大带宽复杂扫频干扰信号生成装置,其特征在于,所述装置包括处理单元、一级dds及多个二级dds;

技术总结

本发明公开了一种基于FPGA的大带宽复杂扫频干扰信号生成方法及装置。所述方法包括:基于扫频调制参数,通过一级DDS生成扫频调制信号;根据扫频调制信号,生成多个并行的相位控制字;基于并行的相位控制字,在多个并行通道中,通过多个二级DDS生成多个并行的基带信号;根据多个并行的基带信号,生成扫频干扰信号。相较于只通过一级DDS进行映射的传统方法,本发明提供的方法通过两级DDS的映射最终得到扫频干扰信号的基带信号,能够提高扫频干扰信号的调制方式的复杂度。

技术研发人员:郭亮,杨林超,荆丹,许晴,吕艳,白剑,赵杨,汤恒仁,邢孟道

受保护的技术使用者:西安电子科技大学

技术研发日:

技术公布日:2024/3/12

- 还没有人留言评论。精彩留言会获得点赞!