一种基于FPGA的抽头延迟链型TDC

本发明是关于一种基于fpga(field-programmable-gate-arrays,现场可编程逻辑门阵列)的抽头延迟链型tdc(time-to-digit converter,时间数字转换器编码器结构),涉及核探测。

背景技术:

1、在核探测领域处理高速信号是至关重要的。随着科技进步,核探测器能够以更高精度和更快响应捕捉到更多粒子信息,同时也带来了挑战即如何处理高速信号。高时间分辨率的定时系统可以提高探测系统对于高速信号的处理能力。抽头延迟链型tdc是一种具有快时间响应、低死时间和低资源占用特点的时间数字化方法,其时间分辨能力取决于组成抽头延迟链的逻辑单元的尺寸大小和均匀性。

2、现有抽头延迟链的编码器实现原理是定位延迟链所产生的温度计码中0-1界线的位置,一种方法是通过级联的全加器将温度计码的所有位相加,从而得到信号在延迟链中传输距离对应的二进制位置码;另一种方法是将温度计码的所有位分成若干组,在每一组中并行判选是否存在0-1界限从而快速定位,并根据判选结果输出对应的二进制位置码。

3、上述两种延迟链编码器结构均存在各自的问题,级联加法器方法计算过程中为避免时序冲突和亚稳态,需要使用多级流水线,资源消耗量大。且由于锁存时间的随机性,造成高位位置码所对应的逻辑资源的利用率低;分组判选方法利用并行处理选通输出的结构,节省了逻辑资源,同时避免了高位位置编码对应逻辑资源利用率低的问题,但是结构复杂,只能针对特定的链长进行设计,稳定性不高。

技术实现思路

1、本发明旨在至少解决现有技术中存在的技术问题之一。为此,针对上述问题,本发明的目的是提供一种基于fpga的抽头延迟链型tdc,能够控制和缩短调度数据时间,减少资源用量。

2、为了实现上概发明目的,本发明采用的技术方案为:

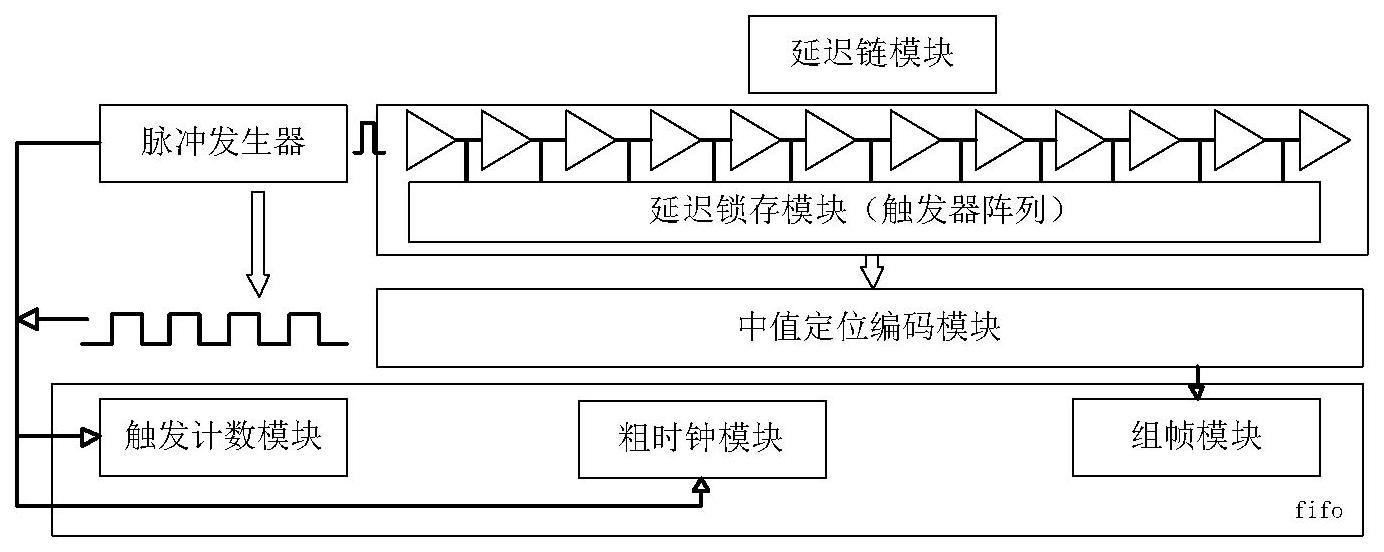

3、第一方面,本发明提供一种基于fpga的抽头延迟链型tdc,包括:

4、脉冲发生器,被配置为在被测信号的触发下产生一个具有变化沿的脉冲输出;

5、延迟链模块,被配置为设置所述fpga中可配置逻辑单元的carry4结构布局,使得对所述脉冲发生器输出的被测信号进行延时传输产生温度计码;

6、延迟锁存模块,被配置为将所述温度计码进行锁存;

7、中值定位编码模块,被配置为对锁存的温度计码进行中值定位处理,输出细时间帧;

8、粗时钟模块,被配置为设置tdc粗时钟,产生被测信号的粗时间戳;

9、触发计数模块,被配置为输出触发count组合,获得触发计数;

10、组帧模块,被配置根据细时间帧与粗时间戳得到时间帧,并与触发计数组合为完整的数据帧输出。

11、进一步地,还包括时钟域隔离处理模块,被配置为将所述组帧模块输出的数据帧输入fifo进行存储和时钟域隔离,以划分tdc的高频率时钟域和外部传输结构的低频率时钟域,其中,fifo为先入先出的存储栈。

12、进一步地,所述中值定位编码模块对每个二进制位的温度计码进行判断和编码,通过将二进制数列分成两半,并根据中间位置的值进行判断,确定编码的位置和形式。

13、进一步地,所述中值定位编码模块确定编码的位置和形式的过程,包括:定位取值结束后高四位逐位乘法运算,被乘数为锁存的1bit逻辑值,乘数为依据每次中值定位之后存入data_pre[n]的位宽,乘法运算之后的结果进行加法运算得到8位二进制数。

14、进一步地,所述中值定位编码模块的具体编码过程,包括:

15、设置data_keep为最终二进制编码输出结果,链长l,位宽[l-1:0],取第位为data_keep第八位,锁存第位数据;

16、进行第1次中值定位,判断raw_data第位是否为1,为1将存入data_pre1为0将存入data_pre1data_pre1为第1次中值比较保留站,位宽为原始温度计码链长一半;取data_pre1第位为data_keep第七位,锁存第位数据;

17、进行第2次中值定位,判断data_pre1第位是否为1,为1将存入data_pre2为0将存入data_pre2data_pre2为第2次中值比较保留站,位宽为第1次中值保留站一半;取data_pre2第位为data_keep第六位,锁存第位数据;

18、进行第3次中值定位,判断data_pre2第位是否为1,为1将存入data_pre3为0将存入data_pre3data_pre3为第3次中值比较保留站,位宽为第2次中值保留站一半;取data_pre3第位为data_keep第六位,锁存第位数据;

19、进行第4次中值定位,判断data_pre3第位是否为1,为1将存入data_pre4为0将存入data_pre4

20、剩余的温度计码逐位相加,每一位作为独立的数,从最低位向最高位逐位相加,存入data_keep最低4bit。

21、进一步地,中值定位的次数与链长呈相关性,关联公式如下:

22、

23、其中,n为中值定位次数,整数类型;a为常数,实数类型。

24、进一步地,设置fpga中可配置逻辑单元的carry4结构布局,包括:单个carry4结构有4个延迟链,延迟链通过手动添加至芯片任意位置,由于延迟链需要线性摆放,通过画一个框或者手动拖拽的方式将链放置在一条直线上;同时,需要将延迟链放置于一个时钟域中。

25、本发明由于采取以上技术方案,其具有以下特点:

26、1、本发明的编码器采用中值定位编码,该编码器采用二分法的思想,在每个二进制位上进行判断和编码,通过将二进制数列分成两半,并根据中间位置的值进行判断,可以快速确定编码的位置和形式,链长位数可不用固定,例如256时,可不用通过定位乘法运算,中值为第127位,直接置入8bit二进制码的最高位即可表示是否为有效位,因此本发明通过划分和逐步判断二进制位,能够快速而有效地进行编码。

27、2、本发明的编码器具有流水线处理能力,可以同时处理多个二进制位的编码,流水线处理相对于传统串行处理来说能够在时间复杂度上更小,是由二分法的中值温度码判选之后进行的操作,通过流水线处理,可以大大提高编码速度和系统吞吐量,除tdc锁存4ns死时间外,其余结构均为流水线处理,后续处理时间不等同于死时间的范围内,不会占用额外的带宽。

28、3、本发明的编码器具有快速响应的特点,由于采用了二分法的思想,编码器对于不同位上的变化能够快速响应,并在短时间内完成编码过程,有助于减小系统的延迟和响应时间,且能够快速定位并且避免“气泡错误”。

29、4、本发明不使用相对于其他tdc的优先级编码或者级联加法器,不需要对编码数据进行预编码,对于k7芯片来说lut资源量比ff资源量小,在使用同等数量的lut情况下减少了乘法器运算和ff的使用,缩减触发器的资源用量,为工程应用提供资源保障。

30、5、本发明的编码器具有可编程性,可以根据特定应用的需求进行灵活配置和优化,相对于固定链长的tdc只能适用于特定的频率,对设计的可移植性差,本发明在不同时钟频率情况下tdc链长呈现不同的长度,可以通过调整编码器输入链长参数实现不同链长的tdc编码处理,以实现不同精度和效率的编码过程。

31、综上,本发明可以适用于各种数字系统和应用场景,包括数字信号处理、通信系统、计算机存储等,它可以在高速数据传输和处理中起到重要作用,提高系统的效率和性能,对持续研究和改进高速信号处理技术对于核探测领域具有重要意义。

- 还没有人留言评论。精彩留言会获得点赞!