一种管脚电平控制方法、系统、设备及存储介质与流程

本发明属于集成电路,具体涉及一种管脚电平控制方法、系统、设备及存储介质。

背景技术:

1、可编程逻辑器件(programablelogicdevice,pld)是数字系统设计的主要硬件平台,用户通过硬件描述语言和相关电子设计自动化软件对其编程和配置,cpld具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进、设计制造成本低、保密性强等优点,已成为电子产品不可缺少的组成部分,因此被广泛应用于产品的原型设计和产品生产之中。

2、现有技术中可编程逻辑器件在利用jtag(jointtestactiongroup,联合测试工作组)升级配置时,当进入到升级配置过程中,管脚电平状态无法保持会回到出厂默认状态,有的会回到厂家预设的高电平状态,有的会回到厂家预设的低电平状态,存在复位异常等问题,设计者不得不在硬件上增加强上下拉电阻来维持配置过程中各管脚的电平状态,这无疑增加了硬件设计的复杂程度和成本,因此如何在升级配置过程中维持各管脚电平状态,是一个亟待解决的问题。

技术实现思路

1、本发明提供了一种管脚电平控制方法、系统、设备及存储介质,用以解决如何在升级配置过程中维持各管脚电平状态的问题。

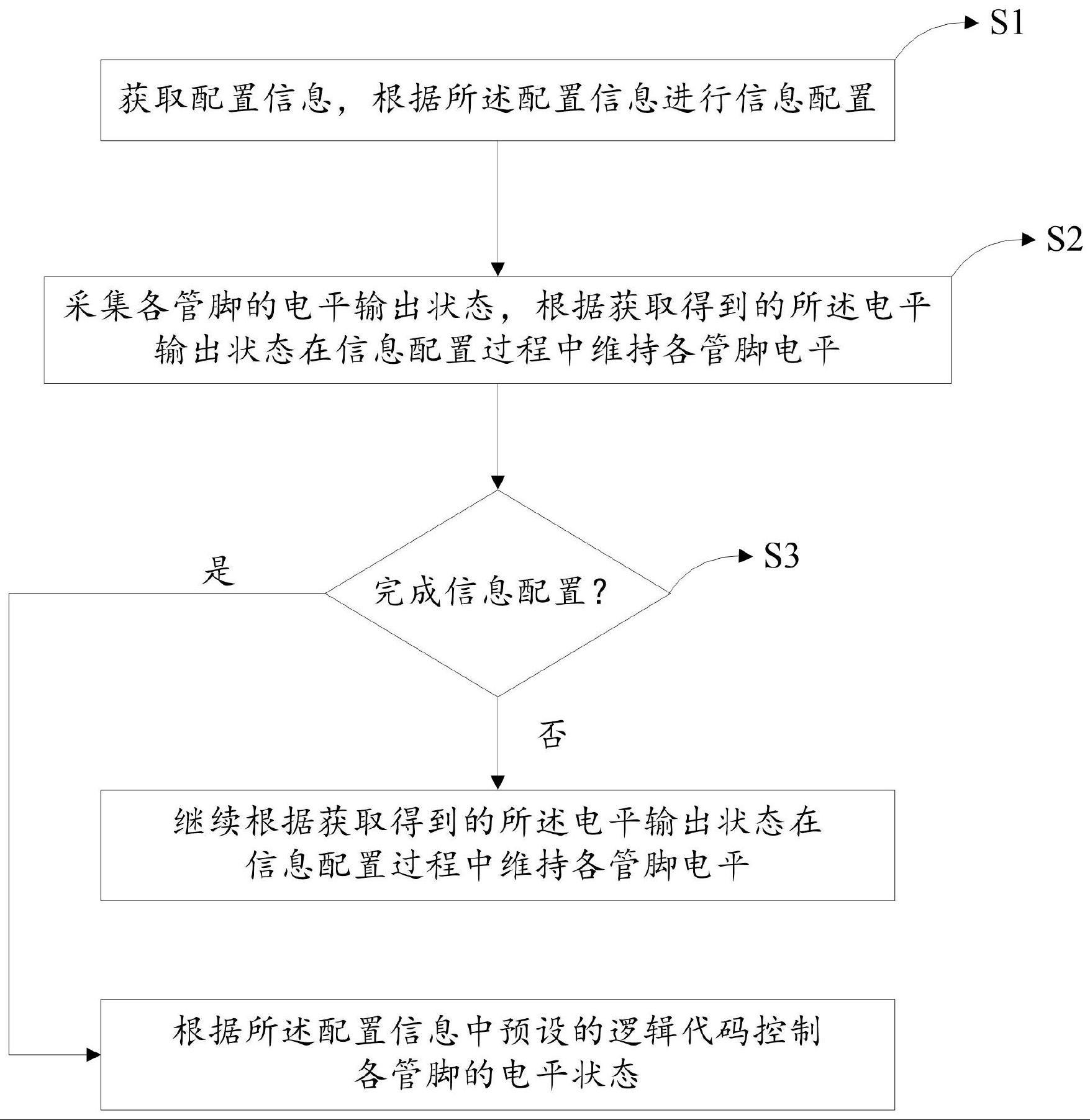

2、为了解决上述技术问题,本发明提供了一种管脚电平控制方法,包括:

3、获取配置信息,根据所述配置信息进行信息配置;

4、采集各管脚的电平输出状态,根据获取得到的所述电平输出状态在信息配置过程中维持各管脚电平;

5、判断是否完成信息配置,若未完成信息配置,则继续根据获取得到的所述电平输出状态在信息配置过程中维持各管脚电平;

6、若完成信息配置,则根据所述配置信息中预设的逻辑代码控制各管脚的电平状态。

7、进一步地,所述方法应用于处理器和挂接在所述处理器上的可编程逻辑器件,其特征在于,所述获取配置信息,根据所述配置信息进行信息匹配包括:

8、所述处理器通过配置总线获取挂接在所述处理器上的可编程逻辑器件的配置信息,将所述配置信息通过所述配置总线写入所述处理器进行信息配置。

9、进一步地,所述采集各管脚的电平状态,包括:

10、所述可编程逻辑器件根据所述处理器通过jtag接口发送的配置控制指令进入配置控制模式,所述处理器通过jtag接口进行边界扫描,将所述各管脚的电平输出状态采集到所述处理器的边界扫描寄存器中。

11、进一步地,所述根据获取得到的所述电平输出状态在信息配置过程中维持各管脚电平,包括:

12、所述边界扫描寄存器根据获取得到的所述电平输出状态,在信息配置过程中维持所述可编程逻辑器件的各管脚电平。

13、进一步地,所述判断是否完成信息配置,若未完成信息配置,则继续根据获取得到的所述电平输出状态在信息配置过程中驱动各管脚电平,包括:

14、所述可编程逻辑器件根据所述处理器通过jtag接口发送的复位指令,进入复位模式;

15、所述处理器判断所述可编程逻辑器件是否完成信息配置,若未完成信息配置,则所述边界扫描寄存器继续根据获取得到的所述电平输出状态,在信息配置过程中维持所述可编程逻辑器件的各管脚电平。

16、进一步地,所述若完成信息配置,则根据所述配置信息中预设的逻辑代码控制各管脚的电平状态,包括:

17、所述处理器判断所述可编程逻辑器件是否完成信息配置,若完成信息配置,

18、则所述可编程逻辑器件根据所述处理器通过jtag接口发送的退出复位指令退出所述复位模式,再根据所述处理器通过jtag接口发送的退出配置控制指令退出配置控制模式,由所述配置信息中预设的逻辑代码继续控制所述可编程逻辑器件的各管脚的电平状态。

19、进一步地,所述处理器为装设有jtag线缆的计算机,或微处理器芯片;

20、所述可编程逻辑器件为现场可编程的门阵列fpga,或复杂可编程逻辑器件cpld。

21、本发明还提供了一种管脚电平控制系统,所述系统包括配置信息获取模块、管脚电平驱动模块、配置信息判断模块;

22、所述配置信息获取模块用于获取配置信息,根据所述配置信息进行信息配置;

23、所述管脚电平驱动模块用于采集各管脚的电平输出状态,根据获取得到的所述电平输出状态在信息配置过程中维持各管脚电平;

24、所述配置信息判断模块用于判断是否完成信息配置,若未完成信息配置,则继续根据获取得到的所述电平输出状态在信息配置过程中维持各管脚电平;

25、若完成信息配置,则根据所述配置信息中预设的逻辑代码控制各管脚的电平状态。

26、本发明还提供了一种管脚电平控制设备,包括处理器和存储器,其中:

27、所述存储器用于存储计算机程序;

28、所述处理器用于读取所述存储器中的计算机程序,并执行上述任一管脚电平控制方法的步骤。

29、本发明还提供了一种计算机可读存储介质,其上存储有可读的计算机程序,该程序被处理器执行时实现如上述任一管脚电平控制方法的步骤。

30、本发明提供的一种管脚电平控制方法、系统、设备及存储介质,可编程逻辑器件在利用jtag进行升级配置时,利用可编程逻辑器件的jtag接口的边界扫描寄存器,在信息配置前将管脚的电平状态采样到边界扫描寄存器,在升级配置过程中由边界扫描寄存器按照获取的电平状态继续维持配置前的电平状态,当升级配置结束后,再根据设计者的逻辑代码驱动各管脚的电平状态,设计时不需要提前针对某个管脚电平做特别的强上下拉电阻,简化了设计的复杂度,进一步降低了调试和后期维护的成本。

技术特征:

1.一种管脚电平控制方法,其特征在于,包括以下步骤:

2.如权利要求1所述的一种管脚电平控制方法,所述方法应用于处理器和挂接在所述处理器上的可编程逻辑器件,其特征在于,所述获取配置信息,根据所述配置信息进行信息匹配,包括:

3.如权利要求2所述的一种管脚电平控制方法,其特征在于,所述采集各管脚的电平状态,包括:

4.如权利要求3所述的一种管脚电平控制方法,其特征在于,所述根据获取得到的所述电平输出状态在信息配置过程中维持各管脚电平,包括:

5.如权利要求3所述的一种管脚电平控制方法,其特征在于,所述判断是否完成信息配置,若未完成信息配置,则继续根据获取得到的所述电平输出状态在信息配置过程中维持各管脚电平,包括:

6.如权利要求5所述的一种管脚电平控制方法,其特征在于,所述若完成信息配置,则根据所述配置信息中预设的逻辑代码控制各管脚的电平状态,包括:

7.如权利要求2所述的一种管脚电平控制方法,其特征在于,所述处理器为装设有jtag线缆的计算机,或微处理器芯片;

8.一种管脚电平控制系统,其特征在于,包括配置信息获取模块、管脚电平驱动模块、配置信息判断模块;

9.一种管脚电平控制设备,其特征在于,包括处理器和存储器,其中:

10.一种计算机可读存储介质,其特征在于,其上存储有可读的计算机程序,该程序被处理器执行时实现如权利要求1~7所述的任一管脚电平控制方法的步骤。

技术总结

本发明公开了一种管脚电平控制方法、系统、设备及存储介质,其中,所述管脚电平控制方法包括获取配置信息,根据所述配置信息进行信息配置;采集各管脚的电平输出状态,根据获取得到的所述电平输出状态在信息配置过程中维持各管脚电平;判断是否完成信息配置,若未完成信息配置,则继续根据获取得到的所述电平输出状态在信息配置过程中维持各管脚电平;若完成信息配置,则根据所述配置信息中预设的逻辑代码控制各管脚的电平状态。利用本发明公开的一种管脚电平控制方法、系统、设备及存储介质,不需要提前针对某个管脚电平做特别的强上下拉电阻,简化了设计的复杂度,进一步降低了调试和后期维护的成本。

技术研发人员:邱枫,包朝伟,张旭华

受保护的技术使用者:深圳市紫光同创电子有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!