一种带隙基准电压源电路的制作方法

本发明涉及基准电压源电路领域,尤其涉及一种带隙基准电压源电路。

背景技术:

1、传统的带隙基准电压源结构中通常具有至少两个双极型晶体管,且其中的运算放大器采用的是折叠式共源共栅结构。这样的架构存在不少缺点:

2、首先,传统的带隙基准电压源中的两个双极型晶体管涉及两路电流,折叠式共源共栅结构中需要三路电流,造成功耗较大。

3、其次,运算放大器采用折叠式共源共栅结构会造成运算放大器的输入等效失调电压较大,并进而造成带隙基准电压源的输出基准电压精度较差。

4、再次,传统的带隙基准电压源结构中的两个双极型晶体管以及折叠式共源共栅结构占用芯片面积较大。

5、因此,亟需一种功耗低、面积小、精度高的带隙基准电压源结构。

技术实现思路

1、为了解决现有技术中的技术问题,本发明提供了一种新型的带隙基准电压源电路结构,适用于片上系统中低功耗、高精度、低成本的基准电压源的产生。

2、本发明的带隙基准电压源电路包括:

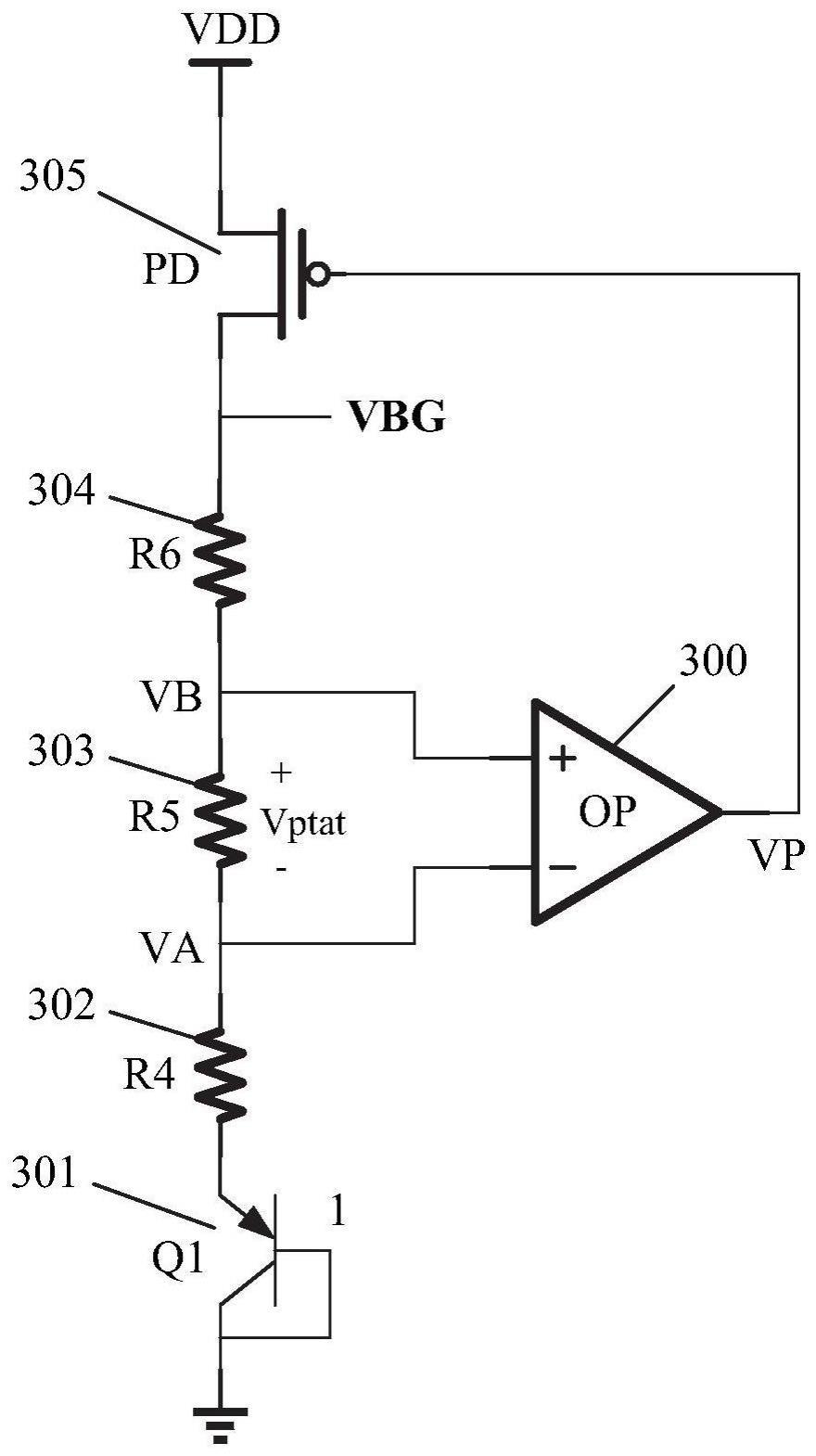

3、运算放大器、第一电阻、第二电阻、第三电阻、pmos管以及一个bjt管;

4、所述运算放大器的正极输入端耦接第二电阻的第二端,所述运算放大器的负极输入端耦接第二电阻的第一端,所述运算放大器的输出端耦接pmos管的栅极;

5、所述pmos管的源极耦接电源电压vdd,漏极耦接所述带隙基准电压源电路的输出端;

6、第三电阻的第二端耦接所述pmos管的漏极,第三电阻的第一端耦接第二电阻的第二端;

7、第二电阻的第一端耦接第一电阻的第二端;

8、第一电阻的第一端耦接所述bjt管的发射极;

9、所述bjt管的基极与集电极耦接并接地。

10、在一个实施例中,所述运算放大器采用套筒式共源共栅结构实现。

11、在一个实施例中,所述运算放大器内的输入对管均工作在亚阈值区,所述输入对管的比例设计为1:n。

12、在一个实施例中,第二电阻的两端的压差vptat=mvt·lnn,其中m为所述亚阈值区的斜率因子,vt为热电势。

13、在一个实施例中,m的值在1到2之间。

14、在一个实施例中,所述带隙基准电压源电路的输出端的输出基准电压vbg的表达式为:

15、

16、其中,vbe(q1)为所述bjt管的基极与发射极之间的电压差,r4为第一电阻的电阻值,r5为第二电阻的电阻值,r6为第三电阻的电阻值,vos为所述运算放大器的输入等效失调电压,为所述输入等效失调电压被放大出现在所述输出端的放大倍数。

17、在一个实施例中,所述运算放大器的输入等效失调电压的值被减小以及所述放大倍数被减小,以提高所述输出基准电压vbg的精度。

18、在一个实施例中,所述带隙基准电压源电路仅包括一个所述bjt管。

19、在一个实施例中,至少第一电阻的存在允许所述运算放大器采用套筒式共源共栅结构。

20、在一个实施例中,所述bjt管为pnp型。

21、本发明具有以下有益效果:

22、本发明的带隙基准电压源结构只需要一个bjt管,并且运算放大器可使用简单的套筒式共源共栅结构,相比于传统结构功耗明显降低,面积大幅减小,并且输出电压精度更高。

技术特征:

1.一种带隙基准电压源电路,其特征在于,包括:

2.如权利要求1所述的带隙基准电压源电路,其特征在于,所述运算放大器采用套筒式共源共栅结构实现。

3.如权利要求2所述的带隙基准电压源电路,其特征在于,所述运算放大器内的输入对管均工作在亚阈值区,所述输入对管的比例设计为1:n。

4.如权利要求3所述的带隙基准电压源电路,其特征在于,第二电阻的两端的压差vptat=mvt·lnn,其中m为所述亚阈值区的斜率因子,vt为热电势。

5.如权利要求4所述的带隙基准电压源电路,其特征在于,m的值在1到2之间。

6.如权利要求5所述的带隙基准电压源电路,其特征在于,所述带隙基准电压源电路的输出端的输出基准电压vbg的表达式为:

7.如权利要求6所述的带隙基准电压源电路,其特征在于,所述运算放大器的输入等效失调电压的值被减小以及所述输入等效失调电压被放大出现在所述输出端的放大倍数被减小,以提高所述输出基准电压vbg的精度。

8.如权利要求1所述的带隙基准电压源电路,其特征在于,所述带隙基准电压源电路仅包括一个所述bjt管。

9.如权利要求1所述的带隙基准电压源电路,其特征在于,至少所述第一电阻的存在允许所述运算放大器采用套筒式共源共栅结构。

10.如权利要求1所述的带隙基准电压源电路,其特征在于,所述bjt管为pnp型。

技术总结

本发明公开了一种带隙基准电压源电路,包括:运算放大器、第一电阻、第二电阻、第三电阻、PMOS管以及一个BJT管。所述运算放大器的正极输入端耦接第二电阻的第二端,所述运算放大器的负极输入端耦接第二电阻的第一端,所述运算放大器的输出端耦接PMOS管的栅极;所述PMOS管的源极耦接电源电压VDD,漏极耦接所述带隙基准电压源电路的输出端;第三电阻的第二端耦接所述PMOS管的漏极,第三电阻的第一端耦接第二电阻的第二端;第二电阻的第一端耦接第一电阻的第二端;第一电阻的第一端耦接所述BJT管的发射极;所述BJT管的基极与集电极耦接并接地。

技术研发人员:于兴宝

受保护的技术使用者:西安中颖电子有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!