一种微控制器与SSI绝对值编码器通信的电路及方法与流程

本发明属于机电控制,尤其涉及一种微控制器与ssi绝对值编码器通信的电路及方法。

背景技术:

1、在工业自动化控制领域,微控制器(mcu)和高精度绝对值编码器是一对常见搭档。采用同步串行接口(synchronous serial interface,简称ssi)协议的绝对值编码器以其连接线少、抗干扰强的优势而得到广泛应用。

2、然而工业领域常见的微控制器芯片,例如ti公司的c2000系列mcu、意法半导体公司的stm32系列mcu,并没有提供专用的ssi接口来适配ssi绝对值编码器。

3、目前,微控制器获取ssi绝对值编码器数据的主要方式有三种:方式一、使用cpld或fpga与ssi编码器直接通信,然后通过总线把数据传给mcu。例如《传感器世界》杂志刊发的论文《多通道ssi接口绝对值编码器信号采集》,以arm为主控制器实现控制算法,fpga为辅助控制器实现6通道ssi绝对值编码器接口。该方法的缺点是需要增加fpga电路器件成本和布板尺寸,且设计人员需要具备一定的fpga编程能力。方式二、使用mcu的通用io口与ssi编码器通信。例如《现代电子技术》杂志刊发的论文《基于dsp的绝对式光电编码器串行接口设计》,用dsp的通用io口gpiof7循环发送高低电平模拟时钟信号,用端口gpiof6接收编码器数据。该方法的缺点是占用微处理器资源多,实施难度较大,同行实现困难。方法三、使用stm32微控制器的spi总线与ssi编码器通信。例如中国专利cn115391241《基于spi总线接收ssi接口编码器数据的系统及传输方法》。该方法的缺点是其仅适用于stm32微控制器,数据帧大小固定为8位,通过中断来产生多组8位时钟脉冲,导致微控制器与编码器通信存在冗余时间。

技术实现思路

1、本发明的目的在于,为克服现有技术缺陷,提供了一种基于微控制器的串行外设接口(serial peripheral interface,简称spi)与ssi绝对值编码器通信的电路及方法,可获取任意圈数、任意分辨率的ssi协议绝对值编码器的数据,且通信时间可达最短。

2、本发明目的通过下述技术方案来实现:

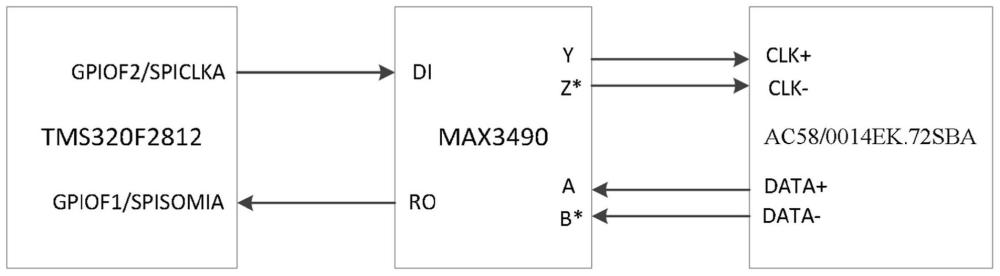

3、一种微控制器与ssi绝对值编码器通信的电路,所述编码器包括编码器时钟端和编码器数据端,所述电路包括:

4、微控制器,所述微控制器包括由芯片控制的串行外设接口,所述串行外设接口包括串行外设接口时钟管脚和串行外设接口主设备输入管脚,所述微控制器数据帧大小可调;

5、差分收发器,所述差分收发器包括由芯片控制的用于连接所述编码器时钟端的差分发送管脚、用于连接所述编码器数据端的差分接收管脚、用于连接所述串行外设接口时钟管脚的单端接收管脚和用于连接所述串行外设接口主设备输入管脚的单端发送管脚。

6、进一步的,所述微控制器包括c2000系列mcu。

7、另一方面,本发明还提供了一种微控制器与ssi绝对值编码器通信的方法,所述方法基于前述任一种的电路实现,所述方法包括:

8、配置微控制器的串行外设接口功能;

9、向微控制器的串行外设接口发送缓存器写入任意数据,使微控制器的串行外设接口时钟管脚产生的时钟信号经差分收发器传输至编码器中;

10、读取微控制器的串行外设接口接收缓存器,获得编码器经差分收发器回传给微控制器串行外设接口主设备输入管脚的缓存数据;

11、当缓存数据仅有一个时,所述缓存数据为接收数据;当缓存数据至少有两个时,拼接所有缓存数据得到接收数据;

12、去除所述接收数据的无效位后得到编码器数据。

13、进一步的,配置微控制器的串行外设接口功能具体包括:

14、配置微控制器的串行外设接口时钟管脚和主设备输入管脚为spi模式;

15、配置串行外设接口功能为主机模式,时钟极性为空闲时高电平;

16、配置数据帧字符长度为m,读写串行外设接口缓存器次数k为[(a+b)/m+1],其中,a为编码器单圈分辨率,b为多圈编码器圈数;

17、配置串行外设接口的波特率:当k=1或串行外设接口的fifo功能使能,串行外设接口时钟周期可设置范围等于编码器时钟周期范围;当k>1且串口外设接口的fifo功能未使能,串行外设接口时钟周期小于编码器两次数据转换间隔时间的1/2。

18、进一步的,所述拼接缓存数据的方法具体包括:

19、读取串口外设接口接收缓存器获得的缓存数据依次记为x1~xk;

20、缓存数据是m位有效的右对齐数据,对读取时排序为i的缓存数据xi,左移m(k-i)位,对移位后的所有新数据求和得到接收数据。

21、进一步的,所述去除无效位的方法具体包括:

22、将所述接收数据右移[km-(a+b+1)]位得到移位数据;

23、移位数据的低(a+b)位即为去除无效位后的编码器数据。

24、本发明的有益效果在于:

25、本发明提供的微控制器与ssi绝对值编码器通信的电路及方法,相比现行用fpga电路处理ssi接口,能降低实现难度,节省器件成本,减小电路布板;相比io口模拟ssi协议与编码器通信,占用微处理器资源少,实施难度小。该方法适用于多种微控制器,适配任意圈数、任意分辨率的ssi绝对值编码器的数据获取及解析,通过灵活配置微控制器允许的串行外设接口数据帧长度,可用最短时长与ssi绝对值编码器通信。

技术特征:

1.一种微控制器与ssi绝对值编码器通信的电路,所述编码器包括编码器时钟端和编码器数据端,其特征在于,所述电路包括:

2.如权利要求1所述的与ssi绝对值编码器通信的电路,其特征在于,所述微控制器包括c2000系列mcu。

3.一种微控制器与ssi绝对值编码器通信的方法,其特征在于,所述方法基于权利要求1或2所述的电路实现,所述方法包括:

4.如权利要求3所述的微控制器与ssi绝对值编码器通信的方法,其特征在于,配置微控制器的串行外设接口功能具体包括:

5.如权利要求4所述的微控制器与ssi绝对值编码器通信的方法,其特征在于,所述拼接缓存数据的方法具体包括:

6.如权利要求4所述的微控制器与ssi绝对值编码器通信的方法,其特征在于,所述去除无效位的方法具体包括:

技术总结

本发明公开了一种微控制器与SSI绝对值编码器通信的电路及方法,该电路包括:微控制器和差分收发器,微控制器包括由芯片控制的串行外设接口,串行外设接口包括串行外设接口时钟管脚和串行外设接口主设备输入管脚;差分收发器包括由芯片控制的用于连接编码器时钟的差分发送管脚、用于连接编码器输出端的差分接收管脚、用于连接串行外设接口时钟管脚的单端接收管脚和用于连接串行外设接口主设备输入管脚的单端发送管脚。本发明适配任意圈数、任意分辨率的SSI协议绝对值编码器的数据获取及解析。

技术研发人员:张文婷,谢伟,赵海,郭祥平

受保护的技术使用者:中国电子科技集团公司第二十九研究所

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!