输出级电路的制作方法

本发明是关于集成电路领域,特别是关于一种输出级电路。

背景技术:

1、classab的输出结构,因其能实现输出轨到轨,被广泛应用于运放产品中;随着芯片集成度的提升,对传输速度的要求提高,电源上的高频扰动越来越受到重视,对产品的高频电源抑制比(psrr@high frequence)有更高的要求。

2、传统的classab输出结构的运算放大器或比较器,电源抑制比会从运算放大器或比较器主极点的位置开始下降,设计上很难将主极点频率做高,因此高频的电源抑制比一般不太高;选择别的输出结构,又会丢失classab的输出轨到轨优势;那么设计一个高频psrr表现优异的classab结构就比较有价值。

3、公开于该背景技术部分的信息仅仅旨在增加对本发明的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现思路

1、本发明的目的在于提供一种输出级电路,其在保留classab输出的特性上,实现电源抑制比开始下降的频点远高于运算放大器或比较器的主极点频点,以此获得较高的高频电源抑制比。

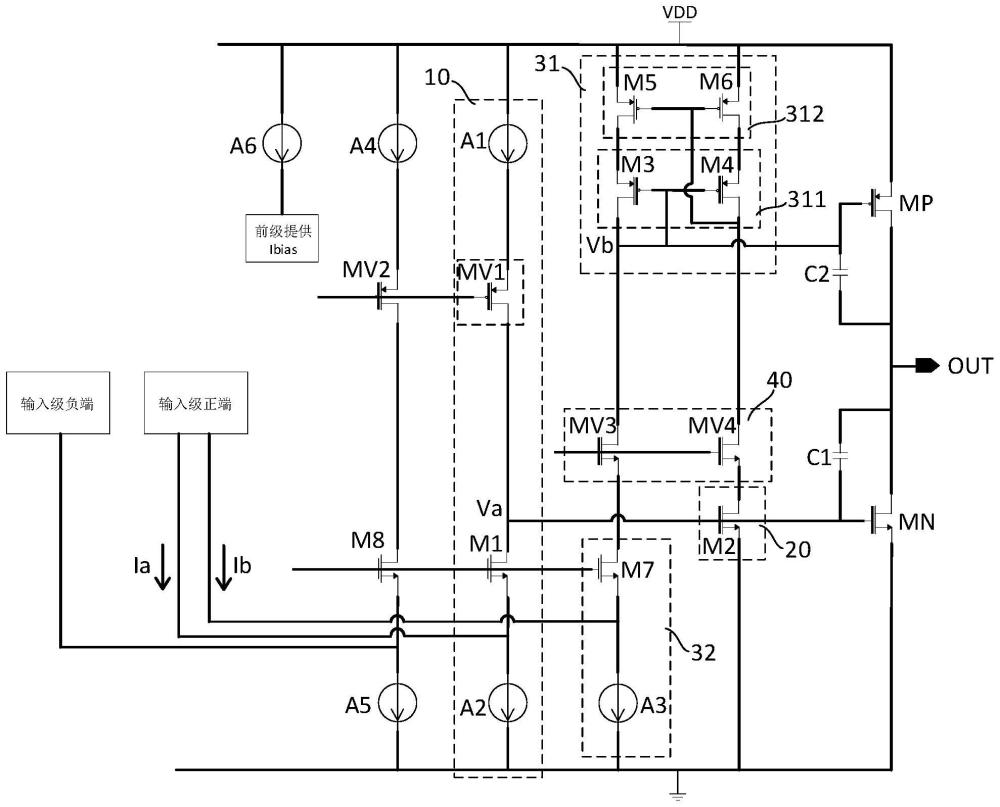

2、为实现上述目的,本发明的实施例提供了一种输出级电路,包括:输出级,所述输出级包括:

3、第一跟随单元,用于基于第一输入电流产生跟随第一输入电流变化的第一控制电压;

4、第一输出管,所述第一输出管的控制端用于接收第一控制电压;

5、采样单元,用于基于第一控制电压产生与第一输出管上的电流呈比例的采样电流;

6、第二跟随单元,用于基于第二输入电流和采样电流产生跟随第二输入电流和采样电流变化的第二控制电压;以及

7、第二输出管,所述第二输出管的控制端用于接收第二控制电压,所述第二输出管的第一端和第一输出管的第一端相连以形成输出级电路的输出端,所述第一输出管的第二端和第二输出管的第二端分别与电源电压和地电压相连。

8、在本发明的一个或多个实施例中,所述第一跟随单元包括第一电流源、第一晶体管和第二电流源,所述第一晶体管的第二端用于接收第一输入电流并同时与第二电流源相连,所述第一晶体管的第一端与第一电流源相连且用于产生第一控制电压。

9、在本发明的一个或多个实施例中,所述采样单元包括第二晶体管,所述第二晶体管的控制端用于接收第一控制电压以在第二晶体管上产生采样电流。

10、在本发明的一个或多个实施例中,所述第二跟随单元包括电流镜像单元和电流跟随电路,所述电流镜像单元与采样单元相连以镜像采样电流而产生第一电流,所述电流跟随电路基于第二输入电流产生跟随第二输入电流变化的第二电流,所述电流镜像单元和电流跟随电路同时与第二输出管的控制端相连以基于第一电流和第二电流产生第二控制电压。

11、在本发明的一个或多个实施例中,所述电流镜像单元包括第一电流镜、或者第一电流镜和偏置单元,所述第一电流镜与采样单元、电流跟随电路和第二输出管的控制端相连以镜像采样电流而产生第一电流并配合第二电流产生第二控制电压,所述偏置单元与第一电流镜相连。

12、在本发明的一个或多个实施例中,所述第一电流镜包括第三晶体管和第四晶体管,所述偏置单元包括第五晶体管和第六晶体管,所述第三晶体管的控制端和第四晶体管的控制端相连,所述第三晶体管的控制端和第三晶体管的第一端相连且与电流跟随电路和第二输出管的控制端相连,所述第四晶体管的第一端与采样单元相连,所述第五晶体管的控制端和第六晶体管的控制端相连,所述第六晶体管的控制端与第四晶体管的第一端或者与第六晶体管的第一端相连,所述第五晶体管的第一端与第三晶体管的第二端相连,所述第六晶体管的第一端与第四晶体管的第二端相连。

13、在本发明的一个或多个实施例中,所述第一电流镜包括第三晶体管和第四晶体管,所述偏置单元包括第一电阻和第二电阻,所述第三晶体管的控制端和第四晶体管的控制端相连,所述第四晶体管的控制端和第四晶体管的第一端相连且与采样单元相连,所述第三晶体管的第一端与电流跟随电路以及第二输出管的控制端相连,所述第三晶体管的第二端与第一电阻相连,所述第四晶体管的第二端与第二电阻相连。

14、在本发明的一个或多个实施例中,所述电流跟随电路包括第七晶体管和第三电流源,所述第七晶体管的第二端用于接收第二输入电流并与第三电流源相连,所述第七晶体管的第一端与电流镜像单元以及第二输出管的控制端相连。

15、在本发明的一个或多个实施例中,所述第二跟随单元还包括设置于电流镜像单元和电流跟随电路之间以及电流镜像单元和采样单元之间的第二高压隔离单元。

16、在本发明的一个或多个实施例中,所述第一跟随单元还包括设置于第一电流源和第一晶体管之间的第一高压隔离单元。

17、与现有技术相比,根据本发明实施例的输出级电路,通过将第一输出管的控制端和第二输出管的控制端分别连接于两个点位,且两个点位之间由高阻结构隔离,在电源电压出现扰动时,第一输出管的控制端不易受到干扰,能够优化高频电源抑制比性能,保持了轨到轨的输出摆幅;本发明实施例的输出级电路能支持高压环境的使用,且与传统classab相比,无明显的成本增加,结构转换性较强,功耗也无额外增加。

技术特征:

1.一种输出级电路,其特征在于,包括:

2.如权利要求1所述的输出级电路,其特征在于,所述第一跟随单元包括第一电流源、第一晶体管和第二电流源,所述第一晶体管的第二端用于接收第一输入电流并同时与第二电流源相连,所述第一晶体管的第一端与第一电流源相连且用于产生第一控制电压。

3.如权利要求1所述的输出级电路,其特征在于,所述采样单元包括第二晶体管,所述第二晶体管的控制端用于接收第一控制电压以在第二晶体管上产生采样电流。

4.如权利要求1所述的输出级电路,其特征在于,所述第二跟随单元包括电流镜像单元和电流跟随电路,所述电流镜像单元与采样单元相连以镜像采样电流而产生第一电流,所述电流跟随电路基于第二输入电流产生跟随第二输入电流变化的第二电流,所述电流镜像单元和电流跟随电路同时与第二输出管的控制端相连以基于第一电流和第二电流产生第二控制电压。

5.如权利要求4所述的输出级电路,其特征在于,所述电流镜像单元包括第一电流镜、或者第一电流镜和偏置单元,所述第一电流镜与采样单元、电流跟随电路和第二输出管的控制端相连以镜像采样电流而产生第一电流并配合第二电流产生第二控制电压,所述偏置单元与第一电流镜相连。

6.如权利要求5所述的输出级电路,其特征在于,所述第一电流镜包括第三晶体管和第四晶体管,所述偏置单元包括第五晶体管和第六晶体管,所述第三晶体管的控制端和第四晶体管的控制端相连,所述第三晶体管的控制端和第三晶体管的第一端相连且与电流跟随电路和第二输出管的控制端相连,所述第四晶体管的第一端与采样单元相连,所述第五晶体管的控制端和第六晶体管的控制端相连,所述第六晶体管的控制端与第四晶体管的第一端或者与第六晶体管的第一端相连,所述第五晶体管的第一端与第三晶体管的第二端相连,所述第六晶体管的第一端与第四晶体管的第二端相连。

7.如权利要求5所述的输出级电路,其特征在于,所述第一电流镜包括第三晶体管和第四晶体管,所述偏置单元包括第一电阻和第二电阻,所述第三晶体管的控制端和第四晶体管的控制端相连,所述第四晶体管的控制端和第四晶体管的第一端相连且与采样单元相连,所述第三晶体管的第一端与电流跟随电路以及第二输出管的控制端相连,所述第三晶体管的第二端与第一电阻相连,所述第四晶体管的第二端与第二电阻相连。

8.如权利要求4所述的输出级电路,其特征在于,所述电流跟随电路包括第七晶体管和第三电流源,所述第七晶体管的第二端用于接收第二输入电流并与第三电流源相连,所述第七晶体管的第一端与电流镜像单元以及第二输出管的控制端相连。

9.如权利要求4所述的输出级电路,其特征在于,所述第二跟随单元还包括设置于电流镜像单元和电流跟随电路之间以及电流镜像单元和采样单元之间的第二高压隔离单元。

10.如权利要求2所述的输出级电路,其特征在于,所述第一跟随单元还包括设置于第一电流源和第一晶体管之间的第一高压隔离单元。

技术总结

本发明公开了一种输出级电路,包括:输出级。输出级包括:第一跟随单元、第一输出管、采样单元、第二跟随单元以及第二输出管。第一跟随单元产生跟随第一输入电流变化的第一控制电压;第一输出管的控制端用于接收第一控制电压;采样单元产生与第一输出管上的电流呈比例的采样电流;第二跟随单元产生跟随第二输入电流和采样电流变化的第二控制电压;第二输出管的控制端用于接收第二控制电压。根据本发明的输出级电路,在电源电压出现扰动时,第一输出管的控制端不易受到干扰,能够优化高频电源抑制比性能,保持了轨到轨的输出摆幅;本发明实施例的输出级电路能支持高压环境的使用,且与传统ClassAB相比,无明显的成本增加,结构转换性较强,功耗也无额外增加。

技术研发人员:龚启善,陈凯亮

受保护的技术使用者:思瑞浦微电子科技(上海)有限责任公司

技术研发日:

技术公布日:2024/2/8

- 还没有人留言评论。精彩留言会获得点赞!