一种数字输入输出处理系统的制作方法

本技术涉及信号处理,尤其涉及一种数字输入输出处理系统。

背景技术:

1、随着工业技术的不断发展,设备需要使用越来越多的传感器,这就使得设备的数字io数量需求越来越多,对数字io的要求也越来越高。

2、市面大部分产品控制输入一般只有单级的rc滤波且滤波精度低,软件通过多次采样进行滤波,控制输出不带自动翻转功能,必须通过软件编程定时再翻转回来,这种控制输入输出方式的输入滤波精度低、输出延时精度低。

3、上述内容仅用于辅助理解本实用新型的技术方案,并不代表承认上述内容是现有技术。

技术实现思路

1、本实用新型的主要目的在于提供了一种数字输入输出处理系统,旨在解决现有技术中数字输入输出处理系统一般只有单级的rc滤波且滤波精度低,软件通过多次采样进行滤波,控制输出不带自动翻转功能,必须通过软件编程定时再翻转回来的技术问题。

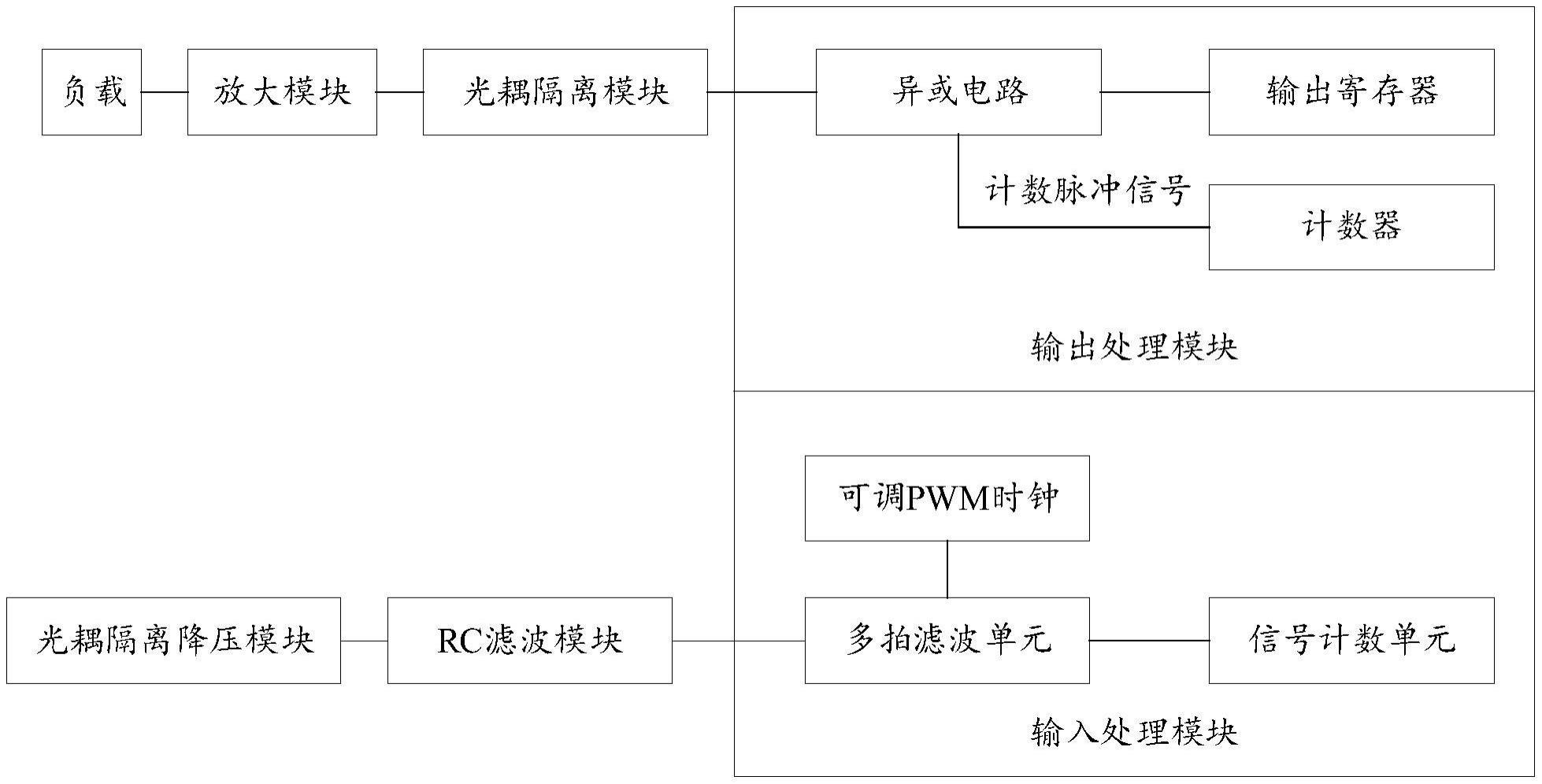

2、为实现上述目的,本实用新型提供了一种数字输入输出处理系统,所述数字输入输出处理系统包括:fpga芯片;

3、所述fpga芯片内设有输入处理模块以及输出处理模块;

4、所述输入处理模块包括:多拍滤波单元;

5、所述多拍滤波单元与所述fpga芯片的外部输入引脚连接;

6、所述输出处理模块包括:计数器和异或电路;

7、所述异或电路分别与所述计数器以及所述fpga芯片的外部输出引脚连接;

8、所述多拍滤波单元,用于对所述外部输入引脚接收到的输入信号进行多拍滤波处理,获得滤波信号,以使外部终端获得滤波信号;

9、所述异或电路,用于基于待处理信号和所述计数器的计数脉冲信号进行异或操作,获得所述待处理信号的翻转信号,并通过所述外部输出引脚将所述翻转信号输出。

10、可选地,所述输入处理模块还包括:可调pwm时钟和信号计数单元;

11、所述多拍滤波单元还分别与所述可调pwm时钟以及所述信号计数单元连接;

12、所述可调pwm时钟,用于根据pwm时钟设置调整多拍滤波单元进行多拍滤波的时间间隔;

13、所述信号计数单元,用于采用fpga寄存器进行输入信号计数。

14、可选地,所述输出处理模块还包括:输出寄存器;

15、所述输出寄存器与所述异或电路连接;

16、所述异或电路,用于基于输出寄存器输出的待处理信号和所述计数器的技术脉冲信号进行异或操作,获得所述待处理信号的翻转信号,并通过所述外部输出引脚将所述翻转信号输出。

17、可选地,所述系统还包括:光耦隔离降压模块和rc滤波模块;

18、所述光耦隔离降压模块与所述rc滤波模块连接,所述rc滤波模块与所述fpga芯片的外部输入引脚连接;

19、所述光耦隔离降压模块,用于对外部输入信号进行电气隔离及降压,获得输入信号,并将所述输入信号发送至所述rc滤波模块;

20、所述rc滤波模块,用于对所述输入信号进行滤波,并将滤波后的输入信号发送至所述fpga芯片。

21、可选地,所述光耦隔离降压模块包括:第一led灯、第一电阻、第一电容、第二电阻以及第一光电耦合器;

22、所述第一led灯的阴极与外部信号的输入端连接,所述第一led灯的阳极与所述第一电阻的第一端连接;

23、所述第一电阻的第二端分别与所述第一电容的第一端、所述第二电阻的第一端以及所述第一光电耦合器的第一端连接;

24、所述第一电容的第二端与输入输出接口连接,所述第二电阻的第二端与所述第一电容的第二端连接;

25、所述第二电阻的第二端、所述第一电容的第二端还与所述第一光电耦合器的第二端连接;

26、所述第一光电耦合器的第三端与所述rc滤波模块连接;

27、所述第一光电耦合器的第四端接地。

28、可选地,所述rc滤波模块包括:第三电阻和第二电容;

29、所述第三电阻的第一端与所述第一光电耦合器的第三端连接,所述第三电阻的第二端与供电电压端连接;

30、所述第二电容的第一端与所述第一光电耦合器的第三端连接,所述第二电容的第二端与所述第一光电耦合器接地的第四端连接。

31、可选地,所述系统还包括:光耦隔离模块与放大模块;

32、所述光耦隔离模块与分别所述fpga芯片的外部输出以及所述放大模块连接,所述放大模块与负载连接;

33、所述光耦隔离模块,用于对所述fpga输出的翻转信号进行电气隔离,并将隔离后的所述翻转信号发送至所述放大模块;

34、所述放大模块,用于对隔离后的所述翻转信号进行放大处理,并将处理后的信号发送至负载。

35、可选地,所述光耦隔离模块包括:第四电阻、第五电阻、第三电容、第六电阻、第二led灯和第二光电耦合器;

36、所述第二光电耦合器的第一端与所述fpga芯片的外部输出引脚连接;

37、所述第四电阻的第一端与供电电压端连接,所述第四电阻的第二端与所述第二光电耦合器的第二端连接;

38、所述第二光电耦合器的第三端分别与放大模块、所述第五电阻的第一端以及输入输出接口连接,所述第二光电耦合器的第四端与所述放大模块连接;

39、所述第五电阻的第二端与所述第三电容的第一端连接,所述第三电容的第二端分别与所述第六电阻的第一端、所述放大模块连接;

40、所述第六电阻的第二端与所述第二led灯的阴极连接,所述第二led灯的阳极连接输入输出接口。

41、可选地,所述放大模块包括:三极管、二极管、第七电阻、第三电容以及第八电阻;

42、所述第七电阻的第一端与所述第二光电耦合器的第四端连接,所述第七电阻的第二端分别与低电平端以及所述三极管的发射极连接;

43、所述第八电阻的第一端所述第二光电耦合器的第四端连接,所述第八电阻的第二端与所述三极管的基极连接;

44、所述二极管的阴极与所述第二光电耦合器的第三端连接,所述二极管的阳极分别与所述三极管的集电极、所述第三电容的第二端以及负载连接。

45、本实用新型提出的数字输入输出处理系统包括fpga芯片,fpga芯片内设有输入处理模块以及输出处理模块;输入处理模块包括:多拍滤波单元;多拍滤波单元与fpga芯片的外部输入引脚连接;输出处理模块包括:计数器和异或电路;异或电路分别与计数器以及fpga芯片的外部输出引脚连接。通过滤波单元对外部输入引脚接收到的输入信号进行多拍滤波处理,获得滤波信号;通过异或电路基于待处理信号和计数器的计数脉冲信号进行异或操作,获得待处理信号的翻转信号,并通过外部输出引脚将翻转信号输出。由于是通过fpga芯片中的多拍滤波单元和异或电路进行输入和输出信号的处理,降低了高频误触发电路,并将软件的工作硬件化,通过fpga芯片对输出信号进行翻转,提高了信号处理效率。

技术特征:

1.一种数字输入输出处理系统,其特征在于,所述系统包括:fpga芯片;

2.如权利要求1所述的数字输入输出处理系统,其特征在于,所述输入处理模块还包括:可调pwm时钟和信号计数单元;

3.如权利要求1所述的数字输入输出处理系统,其特征在于,所述输出处理模块还包括:输出寄存器;

4.如权利要求1所述的数字输入输出处理系统,其特征在于,所述系统还包括:光耦隔离降压模块和rc滤波模块;

5.如权利要求4所述的数字输入输出处理系统,其特征在于,所述光耦隔离降压模块包括:第一led灯、第一电阻、第一电容、第二电阻以及第一光电耦合器;

6.如权利要求5所述的数字输入输出处理系统,其特征在于,所述rc滤波模块包括:第三电阻和第二电容;

7.如权利要求1所述的数字输入输出处理系统,其特征在于,所述系统还包括:光耦隔离模块与放大模块;

8.如权利要求7所述的数字输入输出处理系统,其特征在于,所述光耦隔离模块包括:第四电阻、第五电阻、第三电容、第六电阻、第二led灯和第二光电耦合器;

9.如权利要求8所述的数字输入输出处理系统,其特征在于,所述放大模块包括:三极管、二极管、第七电阻、第三电容以及第八电阻;

技术总结

本技术涉及信号处理技术领域,公开一种数字输入输出处理系统,该系统包括FPGA芯片,FPGA芯片内设有输入处理模块以及输出处理模块;输入处理模块包括:多拍滤波单元;多拍滤波单元与FPGA芯片的外部输入引脚连接;输出处理模块包括:计数器和异或电路;异或电路分别与计数器以及FPGA芯片的外部输出引脚连接。通过滤波单元对外部输入引脚接收到的输入信号进行多拍滤波处理获得滤波信号;通过异或电路基于待处理信号和计数器的计数脉冲信号进行异或操作获得待处理信号的翻转信号,并通过外部输出引脚将翻转信号输出,降低了高频误触发电路,并将软件的工作硬件化,通过FPGA芯片对输出信号进行翻转,提高了信号处理效率。

技术研发人员:肖毅

受保护的技术使用者:深圳市恒昱控制技术有限公司

技术研发日:20230628

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!