利用p-n-p-n二极管的无电源的神经元电路

continuous-time trajectory.

″

ieee transactions on neural networks,vol.7,no.2,pp.346-361,mar.1996,doi:10.1109/72.485671.

技术实现要素:

12.本发明的目的在于,开发如下的简单的神经元模拟器件,即,与以往互补金属氧化物半导体神经元模拟器件相比,可通过更少数量的电极来实现高集成度。

13.本发明的目的在于,开发如下的电路及器件,即,与以往的互补金属氧化物半导体神经元电路相比,以低的待机功耗(standby power consumption)为基础进行工作。

14.本发明的目的在于,开发如下的神经元模拟器件及电路,即,可以使用以往互补金属氧化物半导体工序。

15.本发明的目的在于,开发如下的电路,即,与以往的互补金属氧化物半导体神经元电路相比,可具有更少的晶体管数量并可体现高集成化。

16.本发明的目的在于,开发如下的低功耗神经元电路,即,与必须施加外部偏压的以往的互补金属氧化物半导体神经元电路相比,在没有施加外部偏压的情况下,仅通过来自电路的输入的突触电流进行驱动。

17.本发明的目的在于,开发如下的电路,即,在没有额外的电流及电压信号控制器的情况下,神经元电路内部实现激发和复位。

18.本发明的目的在于,开发如下的神经元模拟器件及电路,即,可以考虑向神经元电路的输入部流动的突触输出电流的突触加权值变化来在脉冲神经网络使用。

19.根据一实施例的神经元电路可通过电容器来将从突触输入的电流进行充电来生成电势(potential),若所生成的上述电势大于阈值,则利用与上述电容器相连接的p-n-p-n二极管来生成与所生成的上述电势相应的脉冲电压并输出。

20.根据一实施例的神经元电路可利用与上述p-n-p-n二极管相连接的至少一个晶体管来复位所生成的上述脉冲电压。

21.在一实施例的上述p-n-p-n二极管中,阳极端可以与上述电容器并联,阴极端与至少一个上述晶体管相连接。

22.在一实施例的至少一个上述晶体管中,在第一晶体管中,栅极端可以与栅极线相连接,漏极端与上述p-n-p-n二极管的阴极端串联,第二晶体管的栅极端及漏极端同时与上述第一晶体管的漏极端和上述p-n-p-n二极管的源极端相连接,在第三晶体管中,漏极端同时与上述电容器及上述p-n-p-n二极管的阳极端相连接,上述第三晶体管的栅极端同时与上述第二晶体管的栅极端及漏极端相连接。

23.一实施例的上述脉冲电压可通过上述第一晶体管与上述p-n-p-n二极管的分压(voltage division)确定。

24.一实施例的上述p-n-p-n二极管可利用雪崩击穿(avalanche breakdown)现象来生成与所生成的上述电势相应的脉冲电压,上述雪崩击穿现象通过阳极电压在二极管器件的内部生成。

25.一实施例的上述脉冲电压可根据对于上述输入脉冲的时宽的变化及上述输入脉冲的大小改变频率。

26.一实施例的上述p-n-p-n二极管具有多个势垒,利用上述多个势垒,在施加上述阳

极电压之前隔断电荷载体的注入。

27.一实施例的神经元电路中,当上述阳极电压增加至已设定的基准电压时,上述p-n-p-n二极管可通过上述阳极电压使上述多个势垒的高度在价带中减少,向在上述多个势垒的高度降低的情况下的势阱注入孔。

28.在一实施例的上述p-n-p-n二极管中,可通过在上述第二晶体管的栅极端发生的电压感应复位电流来减少上述脉冲电压,通过在上述第三晶体管的栅极端发生的电压感应放电电流来释放向电容器充电的电荷来复位脉冲电压。

29.在一实施例的神经元电路中,随着来自前端的突触的电流脉冲集成在电容器,上述阳极电压可将会增加,随着上述漏极电压的增加,通过在上述p-n-p-n二极管的内部形成的反向偏压电平形成的势垒将增加,随着上述势垒的增加,若上述漏极电压增加至发生雪崩击穿的阈值电压以上,则通过p-n-p-n二极管的碰撞电离(impact ionization)机理而发生闩锁效应现象。

30.在一实施例的神经元电路中,由于根据所发生的上述闩锁效应而流动的电流,可根据p-n-p-n二极管与第一晶体管的分压,在输出端子v

spike

发生电激发。

31.在一实施例的神经元电路中,若在上述输出端子v

spike

发生脉冲电压,则通过所上升的第三晶体管和第二晶体管的栅极电压,第三晶体管和第二晶体管均可将开启,并释放分别在电容器充电的电荷和v

spike

的电压来执行复位工作。

32.一实施例的神经元电路可通过电容器来将从突触输入的电流进行充电来生成电势,若所生成的上述电势大于阈值,则利用与上述电容器相连接的p-n-p-n二极管来生成与所生成的上述电势相应的脉冲电压并输出,利用与上述p-n-p-n二极管相连接的至少一个晶体管来复位所生成的上述脉冲电流。

33.根据一实施例,本发明具有如下的效果,即,与以往的的神经元模拟器件相比,可利用通过更少数量的电极来进行工作的简单结构的器件来实现高集成度及低电力神经元电路工作。

34.根据一实施例,本发明具有如下的效果,即,与以往的互补金属氧化物半导体神经元模拟器件相比,可使用因闩锁效应而具有陡峭的开关斜率值的器件来体现低功耗的神经元电路。

35.根据一实施例,本发明具有如下的效果,即,与以往的神经元电路相比,可将晶体管的数量最小化,从而实现高集成度及低电力电路工作。

36.根据一实施例,本发明具有如下的效果,即,与以往的神经元电路相比,在没有施加外部偏压的情况下,可以实现自我驱动的低电力神经元电路工作。

37.根据一实施例,本发明具有如下的效果,即,可以体现基于向神经元电路输入来传递的突触电流的大小及施加时宽的变化的神经元激发频率(firing frequency)特性变化。

38.根据一实施例,本发明具有如下的效果,即,可将能够使用互补金属氧化物半导体工序的神经元电路适用于脉冲神经网络。

附图说明

39.图1a和图1b为说明一实施例的二极管结构体与访问电子器件串联来形成p-n-p-n二极管的结构的图。

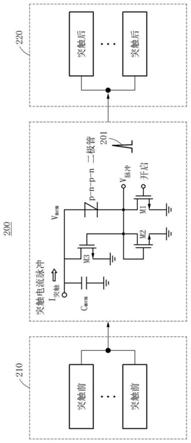

40.图2a至图2f示出一实施例的神经元电路的块框图。

41.图3a说明p-n-p-n二极管的阳极电压的能带图。

42.图3b说明p-n-p-n二极管的阳极电压的电流特性框图。

43.图4a和图4b为说明包括p-n-p-n二极管的多种能带图的神经元电路的脉冲及复位机理的图。

44.图4c为说明以电流模式工作的神经元电路的实施例的图。

45.图4d说明一实施例的神经元电路的模拟的时序图。

46.图5a为示出基于向神经元电路施加的突触电流脉冲的大小变化的输出特性的变化的时序图。

47.图5b为示出基于向神经元电路施加的突触电流脉冲的时间变化的输出特性的变化的时序图。

48.图5c为示出基于向神经元电路施加的突触电流脉冲的大小及时间变化的激发频率变化的框图。

49.附图标记的说明

50.110:二极管结构体

ꢀꢀ

120:访问电子器件

具体实施方式

51.对基于在本说明书中揭示的本发明的概念的实施例,特定结构性或功能性说明仅用于说明本发明的概念的实施例,本发明的概念的实施例可以被实施成多种形态,而并不局限于在本说明书中说明的实施例。

52.本发明的概念的实施例可具有多种变更,并可具有多种形态,因此,在图中例示实施例并在本说明书中进行详细说明。但是,这并非将本发明的概念的实施例限定在特定形态,而是包括本发明的思想及发明要求保护范围中所包括的变更、等同技术方案或代替技术方案。

53.第一或第二等的术语仅可用于说明多种结构要素,上述结构要素并不局限于上述术语。上述术语仅用于区分两种结构要素,例如,在不超出本发明的概念的发明要求保护范围的情况下,第一结构要素可以被命名为第二结构要素,类似地,第二结构要素也可以被命名为第一结构要素。

54.当一个结构要素与其他结构要素

′

连接

′

或

′

联接

′

时,可以与其他结构要素直接连接或联接,也可以在中间存在其他结构要素。相反,当一个结构要素与其他结构要素

′

直接连接

′

或

′

联接

′

时,可以理解为在中间不存在其他结构要素。说明结构要素之间的关系的表现,例如,

′

之间

′

和

′

直接之间

′

或

′

直接相邻

′

等也需要同样地解释。

55.在本说明书中所使用的术语仅用于说明特定实施例,而并非用于限定本发明。只要在文脉上并未明确表示,单数的表现包括复数的表现。在本说明书中,

′

包括

′

或

′

具有

′

等的术语用于指定所说明的特征、数字、步骤、动作、结构要素、部件或这些组合的存在,而并非预先排除一个或一个以上的其他特征、数字、步骤、动作、结构要素、部件或这些组合的存在或附加可能性。

56.只要并未明确定义,包括技术或科学术语在内的在此使用的所有术语的含义与本发明所属技术领域的普通技术人员一般连接的含义相同。通常使用的词典所定义的术语的

synapse)传递。

76.用于无电源的神经元电路200的p-n-p-n二极管可以代替金属氧化物半导体场效应晶体管。

77.如图2a所示,在作为基于互补金属氧化物半导体的无电源的神经元电路200中,作为一个神经元模拟器件的p-n-p-n二极管纳米结构体与三个金属氧化物半导体场效应晶体管及一个蓄电器相连接。在此情况下,p-n-p-n二极管纳米结构体的阳极端与金属氧化物半导体场效应晶体管的漏极及蓄电器并联,从突触前(pre-synapse)接收输入信号。而且,与p-n-p-n二极管纳米结构体的阴极端串联的金属氧化物半导体场效应晶体管m1的栅极在没有施加偏压的情况下以开启(open)状态连接。与p-n-p-n二极管纳米结构体并联的蓄电器集成来自突触前的电流信号,若发生脉冲,则使电流向与蓄电器并联的金属氧化物半导体场效应晶体管(m3)流动,通过上述电流,释放储存在蓄电器的电荷,同时,使电流向与p-n-p-n二极管阴极端串联的金属氧化物半导体场效应晶体管m2流动来执行将脉冲电压信号v

spike

降成0v的复位动作。而且,来自输出的v

spike

向突触后(post-synapse)的输入传递。因此,基于互补金属氧化物半导体工序的神经元电路在没有额外的外部偏压的情况下,仅通过在突触前发生的电流信号执行集成及激发动作,在没有外部电路帮助的情况下,内部自我驱动来执行集成及激发动作。

78.如图2a所示,在神经元电路200的工作中,随着在突触前发生的电流脉冲集成在蓄电器,作为p-n-p-n二极管纳米结构体的阳极电压的v

mem

将会增加。在此情况下,v

mem

将增加至作为如图2a所示的p-n-p-n二极管的2.35v,达到阈值电压的同时,神经元电路200执行激发工作。若在神经元电路200中执行激发,则执行使v

mem

电压再次回到0v的复位工作。在这种神经元电路200中的电集成及激发共工作从时间整合至不应期模仿生物学神经元的集成及激发工作。

79.神经元电路200的各个器件的工作将通过之后的图4a及图4b更加详细地说明。

80.图2a利用1个电容器c

mem

、1个二极管(p-n-p-n二极管)及3个晶体管(金属氧化物半导体场效应晶体管)来体现神经元电路200。

81.在体现神经元模仿电路的过程中,1个电容器c

mem

和1个二极管(p-n-p-n二极管)必然需要电势,在3个晶体管(金属氧化物半导体场效应晶体管)中的至少一个晶体管可以选择性地被其他器件所替代。

82.以下,图2b至图2f为说明可适用本发明的多种神经元电路的实施例的图。

83.首先,图2b中,代替图2a的神经元电路200,仅利用1个电容器c

mem

、1个二极管(p-n-p-n二极管)及1个晶体管m1来体现神经元电路202。

84.神经元电路202可通过突触电流的输入来对电容器c

mem

进行充电并集成电势。

85.并且,若在电容器c

mem

充电的电势达到阈值,则可通过1个二极管(p-n-p-n二极管)的输出端生成输出脉冲。

86.图2c中,代替图2a的神经元电路200,可利用1个电容器c

mem

、1个二极管(p-n-p-n二极管)及2个晶体管m1、m2来体现神经元电路203。

87.神经元电路203可通过突触电流的输入来对电容器c

mem

进行充电并集成电势。

88.并且,若在电容器c

mem

充电的电势达到阈值,则神经元电路203可通过一个二极管(p-n-p-n二极管)的输出端生成输出脉冲。

89.p-n-p-n二极管纳米结构体的阳极端与金属氧化物半导体场效应晶体管的漏极及蓄电器并联,从突触前接收输入信号。而且,与p-n-p-n二极管纳米结构体的阴极端串联的金属氧化物半导体场效应晶体管m2的栅极在没有施加偏压的状态下以开启状态连接。与p-n-p-n二极管纳米结构体并联的蓄电器集成来自突触前的电流信号,若发生脉冲,则使电流向与蓄电器并联的金属氧化物半导体场效应晶体管m1流动,通过上述电路,释放储存于蓄电器的电荷,并执行将脉冲电压信号v

spike

降成0v的复位工作。而且,来自输出的v

spike

向突触后的输入传递。因此,基于互补金属氧化物半导体工序的神经元电路203在没有额外的外部偏压的情况下,仅通过在突触前发生的电流信号来执行集成及激发工作,在没有外部电路帮助的情况下,电路内部自我驱动来执行集成及激发工作。

90.图2d中,代替图2a的神经元电路200,利用1个电容器c

mem

和1个二极管(p-n-p-n二极管)及2个晶体管m1、m2来体现神经元电路204。

91.p-n-p-n二极管纳米结构体的阳极端与金属氧化物半导体场效应晶体管的漏极及蓄电器并联,从突触前接收输入信号。与p-n-p-n二极管纳米结构体并联的蓄电器集成来自突触前的电流信号,若发生脉冲,则使电流向与蓄电器并联的金属氧化物半导体场效应晶体管m1流动,通过上述电流,释放储存于蓄电器的电荷,同时,使电流向与p-n-p-n二极管阴极端串联的金属氧化物半导体场效应晶体管m2流动来执行将脉冲电压信号v

spike

降成0v的复位工作。而且,来自输出的v

spike

向突触后的输入传递。

92.图2e通过将在图2c的实施例中的金属氧化物半导体场效应晶体管m2分别用电阻r1代替来体现神经元电路205,图2f通过将图2c的实施例中的金属氧化物半导体场效应晶体管m2用可变电阻vr1代替来体现神经元电路206的实施例。

93.图3a说明p-n-p-n二极管的阳极电压的能带图310。

94.具有图1a的结构的p-n-p-n二极管在器件的内部形成反向偏压电平,由此,如能带图310所示,当5.9v时的内部势垒的大小将增加。由此,p-n-p-n二极管呈现出基于闩锁效应的神经元模拟器件特性。如图3b所示,神经元模拟器件随着阳极电压的增加,在规定电压发生闩锁效应。即,p-n-p-n二极管可通过与之前的3端子fbfet器件不同的机理工作。

95.图3b为说明p-n-p-n二极管的阳极电压的电流特性框图320的图。如电流特性框图320所示,p-n-p-n二极管纳米结构体呈现出当器件漏极电压约为2.35v时,电流急剧垂直上升的闩锁效应。利用基于作为这种神经元模拟器件的p-n-p-n二极管的闩锁效应特性的低泄漏电流(leakage current)来体现具有极低待机功耗的激发及集成神经元电路。

96.在金属氧化物半导体场效应晶体管神经元电路中,v

mem

向晶体管提供栅极电压,由此,可以作为开启与对应晶体管有关的通道的触发阈值进行工作,且具有2.35v的大小。

97.但是,在小于2.35v的v

mem

的情况下,因子阈值摆动(ss),有可能已经生成v

spike

。因为大于60mv/dec,因此,有可能发生v

spike

时宽大于20μs的问题。

98.并且,为了一个集成及激发工作,金属氧化物半导体场效应晶体管神经元电路以43.0%的能量效率需要1.59mw的功耗(或7.62

×

10-11

j的能量消耗)。

99.当与上述金属氧化物半导体场效应晶体管神经元电路进行比较时,无电源的神经元电路200为了一个集成及激发作业而可以消耗更少的能量。

100.功耗、能量消耗及能量效率分比为0.85mw、1.72

×

10-12

j及99.5%,无电源的神经元电路200的卓越的能量效率可以呈现在v

spike

的小的时宽(约为0.8μs)。对于阳极电流的闩

锁效应及p-n-p-n二极管的关闭电流的阳极电流的高的比例负责减少v

spike

时宽。因此,使用p-n-p-n二极管的无电源的神经元电路200在结构简单性和能量效率侧面比仅由金属氧化物半导体场效应晶体管构成的神经元电路优秀。

101.将在无电源的神经元电路200中执行集成及激发工作的期间的p-n-p-n二极管的电流、电压特性图表与具有实际生物学神经元的集成及激发工作对应呈现。

102.本发明的神经元电路可以使用作为这种神经元模拟器件的p-n-p-n二极管的特性来执行低电力集成及激发功能。

103.在本发明的神经元电路中,随着来自前端的突触的电流脉冲集成在电容器,作为p-n-p-n二极管的漏极电压的v

mem

的电压将会增加。

104.由此,通过在p-n-p-n二极管的内部形成的反向偏压电平形成的势垒逐渐增加。

105.并且,随着势垒的增加,若v

mem

的电压增加至发生雪崩击穿(avalanche breakdown)的阈值电压以上,则通过p-n-p-n二极管的机理发生闩锁效应并发生急剧的电流流动。

106.在此情况下,随着p-n-p-n二极管与第一晶体管的分压,在输出端子v

spike

可发生电激发。

107.另一方面,若在输出端子v

spike

中发生脉冲电压,则通过所上升的m3和m2的栅极电压,m3和m2均将开启并释放分别对电容器进行充电的电荷的v

spike

的电压,由此可以执行复位工作。

108.图4a为说明具有v

mem

的能带图的神经元电路410的脉冲机理的图。

109.图4a和图4b示出包括p-n-p-n二极管的多种能带图的神经元电路410的脉冲及复位机理。

110.神经元电路410可以通过从突触输入的电流来对电容器411进行充电并生成电势(potential)。并且,若所生成的电势大于阈值,则神经元电路410可利用与电容器411相连接的p-n-p-n二极管412,来生成与所生成的电势相应的脉冲电压并输出。并且,神经元电路410可利用与p-n-p-n二极管相连接的多个晶体管413、414、415来复位所生成的上述脉冲电压。

111.在p-n-p-n二极管412中,阳极端可以与电容器411并联,阴极端可以与3个晶体管413、414、415相连接。

112.观察多个晶体管413、414、415之间的连接关系,首先,在第一晶体管m1、413中,栅极端可以与栅极线v

gl

相连接,漏极端可以与p-n-p-n二极管412的源极端串联。

113.并且,第二晶体管m2、414的栅极端及漏极端可以同时与第一晶体管m1、413的漏极端及p-n-p-n二极管412的阴极端相连接。

114.不仅如此,在第三晶体管m3、415中,漏极端可以同时与电容器411及p-n-p-n二极管412的阳极端连接,第三晶体管m3、415的栅极端可以同时与第二晶体管m2、414的栅极端及漏极端相连接。

115.另一方面,p-n-p-n二极管412的阳极端的阈值为了脉冲及复位动作而可以被定义成v

mem

。

116.p-n-p-n二极管412的输出端及第一晶体管的栅极线v

gl

的电压可以确定输出电压v

spike

的适当阈值及脉冲电压。

117.可以改变如用于触发这种电压的阈值、脉冲频率的神经元电路特性。

118.若向p-n-p-n二极管412的输出端及栅极线v

gl

施加规定电压(例如,v

gl

=450mv),则集成及激发工作从基于突触电流输入i

synaptic

的v

mem

的增加体现。

119.若当前的输入脉冲i

synaptic

适用于神经元电路410,则输入电流的总和在电容器411中增加v

mem

电势并被集成(integration)。

120.因此,每当施加电流输入脉冲i

synaptic

,如图4a的附图标记416所示,v

mem

将逐渐增加。

121.若v

mem

大于阈值,则v

spike

发生脉冲并剧增。脉冲电压可通过p-n-p-n二极管412和第一晶体管m1、413的分压(voltage division)确定。

122.图4b为通过依赖于v

mem

的能带图说明神经元电路的复位工作的图。

123.图4b的神经元电路420通过复位工作减少v

mem

,由此,p-n-p-n二极管422的势垒再生成。

124.之后,若v

spike

短时间内增加,则第二晶体管m2、424的栅极电压可以感应复位电流i

reset

。并且,可根据感应的复位电流i

res眦

,v

spike

将会减少。另一方面,与第二晶体管m2、424相连接的第三晶体管m3、425的栅极电压也将减少。随着第三晶体管m3、425的栅极电压减少,则可以感应用于电容器421的放电的电流,结果,p-n-p-n二极管的v

mem

可以减少。

125.由此,如能带图426所示,所充电的p-n-p-n二极管的v

mem

与放电一同逐渐降低。

126.在复位工作后,每当突触输入电流i

synaptic

在神经元电路420流动,发生集成及激发的反复工作。

127.图4c为说明以电流模式工作的神经元电路的实施例的图。

128.神经元电路430可通过从突触输入的电流对电容器431进行充电并生成电势。并且,若所生成的电势大于阈值,则神经元电路430可利用与电容器431相连接的p-n-p-n二极管432来生成与所生成的电势相应的脉冲电流来输出i

out

。并且,神经元电路430可以利用与p-n-p-n二极管相连接的多个晶体管433、434、435来复位所生成的脉冲电流。

129.在p-n-p-n二极管432中,阳极端可以与电容器431并联,阴极端可以与3个晶体管433、434、435相连接。

130.观察多个晶体管433、434、435之间的连接关系,首先,在第一晶体管m1、433中,栅极端可以与栅极线v

gl

相连接,漏极端可以与p-n-p-n二极管432的阴极端串联。

131.并且,第二晶体管m2、434的栅极端及漏极端可以同时与第一晶体管m1、433的漏极端及p-n-p-n二极管432的阴极端相连接。

132.不仅如此,在第三晶体管m3、435中,漏极端可以同时与电容器411及p-n-p-n二极管432的阳极端相连接,第三晶体管m3、435的栅极端可以同时与第二晶体管m2、434的栅极端及漏极端。

133.图4d为说明一实施例的神经元电路的模拟时序图440的图。

134.神经元电路为了集成及激发工作,有可能在p-n-p-n二极管中需要一系列的初始化工作。在神经元电路的初始化工作后,时宽为0.8μs,9.5μa的输入电流脉冲i

synaptic

以10μs的周期向神经元电路施加250μs。每当施加输入脉冲411,v

mem

442将增加0.3v。可通过输入脉冲411第八号,v

mem

442可大于阈值。

135.若vmem442大于阈值,则生成0.0v~1.1v的输出脉冲v

spike

。

136.9.5μa的各个i

synaptic

在时间集成期间,可以将v

mem

增加0.287v。

137.在c

mem

达到8个i

synaptic

之后,若v

mem

达到触发阈值2.3v,则在去极化过程中,v

spike

可以从0迅速变为1.02v。在后续复极(subsequent repolarization)期间,v

mem

和v

spike

均变为0v的初始电压。

138.在去极化和复极的一个期限内,神经元电路可按1.02v的振幅发生v

spike

脉冲。在这种i

synaptic

的情况下,v

spike

可以在11.7khz的频率中反复被激发。另一方面,本发明的神经元电路为了发生集成及激发而需要将p-n-p-n二极管初始化。

139.若完成再设定,则为了集成及激发工作的反复工作,v

spike

及v

mem

可以回到初始值(v

spike

=v

mem

=0.0v)。之后,下一次反复的突触输入脉冲可以再次增加v

mem

,如图4d所示,这种集成及激发工作的循环将正常发生。

140.结果,本发明的一实施例的神经元电路仅可使用4个晶体管来呈现出约为20khz激发频率的集成及激发工作。

141.本发明的神经元电路的性能包括所使用的晶体管的数量、装置类型、突触输入类型、功耗及激发频率,呈现出高于以往的神经元电路的性能。

142.神经元电路的激发频率根据i

synaptic

的振幅和时宽改变。i

synaptic

的更大的振幅或更宽的时宽可以减少v

mem

达到触发阈值的时间。

143.在本发明的神经元电路中,随着具有0.8μs的时宽及10μs的周期的i

synaptic

的振幅从9.5μa按每次0.5μa的速度增加至11μa,激发频率可以从8.1khz增加至15.6khz。而且,随着具有10μa的振幅和10μs的周期的i

synaptic

的时宽t

synaptic

每次增加0.1μs,周期从0.6μs变为0.9μs,激发频率从11.5khz变为24.0khz。这意味着i

synaptic

脉冲的振幅和时宽的调节可以控制对于神经元电路的激发频率。

144.在以往的神经元电路中,使用基于conductance及hindmarsh-rose模型的神经元电路呈现出使用大量的晶体管来以低的激发频率来消耗最高电力的形态。并且,在基于互补金属氧化物半导体的神经元电路的情况下,呈现出优秀的激发频率的izhikevich模型需要14个晶体管和40μw的高功耗。此外,以往的神经元电路在所有装置类型中需要20个以上的晶体管。

145.结果,本发明的神经元电路的电路面积小,功耗和激发频率方面最简单并最有效。

146.图5a为呈现出基于向神经元电路施加的突触电流脉冲的大小变化的输出特性的变化的时序图510。

147.如图5a所示,时序图510呈现出所施加的突触电流脉冲的大小从9.5μa越按10μa、10.5μa,、11μa的顺序增加,激发时间越快的特性。

148.图5b为示出基于向神经元电路施加的突触电流脉冲的时间变化的输出特性的变化的时序图520。

149.如图5b所示,时序图520呈现出对所施加的突触电流脉冲的大小,时间变化从0.6μs越按0.7μs、0.8μs、0.9μs的顺序增加,激发时间越快的特性。

150.图5c为示出基于向神经元电路施加的突触电流脉冲的大小及时间变化的激发频率(firing frequency)变化的时序图530。

151.确认基于向神经元电路施加的突触电流脉冲的大小及时间变化的激发频率特性的变化。如前面说明,突触前电流的大小越增加,电流的发生时宽越长,神经元电路所激发

的时间点越快。这是因为电流的大小及发生时间越长,在单位时间的蓄电器集成的电荷量将增加。因此,如图5c所示,电流的大小i

synaptic

及发生时宽t

synaptic

越增加,激发频率(firing frequency)将会增加。

152.结果,若利用本发明,则与以往互补金属氧化物半导体神经元模拟器件相比,可以开发能够通过更少的电极数量实现高集成度的简单的神经元模拟器件。

153.并且,若利用本发明,与以往互补金属氧化物半导体神经元器件相比,可以开发以低的待机功耗(standby power consumption)为基础进行工作的器件,可以开发能够使用以往互补金属氧化物半导体工序的神经元模拟器件及电路,与以往互补金属氧化物半导体神经元电路相比,可以开发能够同时实现高集成化及低功耗化的电路。

154.不仅如此,若利用本发明,则可以开发在没有额外的控制器的情况下,神经元电路内部实现激发和复位的电路,并可开发能够用于脉冲神经网络的神经元模拟器件及电路。

155.以上说明的装置可体现为硬件结构要素、软件结构要素和/或硬件结构要素及软件结构要素的组合体现。例如,在实施例中说明的装置及结构要素,例如,如处理器、控制器、算术逻辑单元(alu,arithmetic logic unit)数字信号处理器(digital signal processor)、微计算机、现场可编程阵列(fpa,field programmable array)、可编程序逻辑部件(plu,programmable logic unit)、微处理器或可以执行并响应指令(instruction)的其他任何装置,可以利用一个以上的常用计算机或特殊目的计算机来体现。处理装置可以执行操作系统(os)及在上述操作系统上执行的一个以上的软件应用。并且,处理装置响应软件的运行来访问、存储、操作、处理及生成数据。为了方便理解,说明了使用1个处理装置的情况,本发明所属技术领域的普通技术人员可以知道处理装置可以包括多个处理要素(processing element)和/或多种类型的处理要素。例如,处理装置可包括多个处理器或一个处理器及一个控制器。并且,也可以为如并行处理器(parallel processor)的其他处理结构(processing configuration)。

156.软件可以包括计算机程序(computer program)、代码(code)、指令(instruction)或这些中的一个以上的组合,以按需要进行工作的方式构成处理装置或者独立或结合性(collectively)地向处理装置下令。软件和/或数据通过处理装置解释或者向处理装置提供指令或数据而在一种类型的机械、结构要素(component)、物理装置、虚拟装置(virtual equipment)、计算机存储介质或装置或所传送的信号波(signal wave)永久或暂时具体化(embody)。软件分散在网络连接的计算机系统上,从而可通过分散的方法存储或运行。软件及数据可存储于一个以上的计算机可读记录介质。

157.如上所述,虽然通过限定的附图说明了实施例,但只要是本发明所属技术领域的普通技术人员,可从上述记载进行多种修改及变形。例如,所说明的技术可通过按与所说明的方法不同的顺序执行,和/或所说明的系统、结构、装置、电路等的结构要素按与所说明的方法不同的形态结合或组合,或者通过其他结构要素或等同技术方案代替或置换,也可以实现适当的结果。

158.因此,与其他实例、其他实施例及发明要求保护范围等同的内容也属于后述的发明要求保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1