存内计算模块和方法、存内计算网络及构建方法与流程

1.本发明涉及存储器领域。具体而言,本发明涉及存内计算模块和方法、存内计算网络及其构建方法。

背景技术:

2.在现有技术中,处理器厂商与内存厂商相互分离,导致了内存技术与处理器技术的发展不同步。处理器性能快速提升,而内存性能提升速度相对较慢。处理器性能和内存性能的不均衡发展造成了内存的存取速度严重滞后于处理器的计算速度,内存瓶颈导致高性能处理器难以发挥出应有的功效,这对日益增长的高性能计算形成了极大的制约。这种内存性能严重限制处理器性能发挥的现象被称为“内存墙”(memory wall)。

3.随着中央处理单元(cpu)计算能力和应用计算规模的持续快速增长,“内存墙”的问题愈发凸显。

4.为了解决“内存墙”问题,出现了“存内计算”或者说“存算一体”的概念。

5.传统的计算单元和内存单元是分离的,即不在同一个芯片内。因此,在传统的计算过程中,计算单元需要将数据从内存单元中提取出来,处理完成后再写回内存单元。而“存内计算”是把内存单元和计算单元结合在一起,通过让内存单元尽量靠近计算单元,缩短数据传输路径,从而降低了数据访问延迟。同时,“存内计算”设法提高访问带宽,从而有效地提升了计算性能。

6.现有技术中已知的一种“存内计算”结构如图1所示。在该“存内计算”结构中,内存单元采用阻变式存储器rram(resistive random access memory),计算单元为神经网络处理单元npu(neural-network process units)。由于阻变式存储器rram和神经网络处理单元npu使用一体化结构,神经网络处理单元npu的访问延迟低。然而,阻变式存储器rram的工艺领域技术尚未成熟,结构设计不具有可扩展性,难以实现更高性能计算需求。

7.现有技术中,还存在一种采用硅通孔tsv(through silicon via)技术的3d堆叠技术来实现“存内计算”结构。该3d堆叠技术将多个晶片堆叠在一起,使用硅通孔tsv技术将不同的晶片之间互连。这是一种三维的多层堆叠,通过硅通孔tsv实现多个晶片在垂直方向的通信。然而,在该3d堆叠技术中,存在诸多技术难点。例如,硅通孔tsv深孔的填充技术,因为硅通孔tsv深孔的填充效果直接关系到3d堆叠技术的可靠性和良率,这对于3d堆叠技术集成实用化是至关重要的。再例如,硅通孔tsv技术需要在基片减薄过程中保持良好的完整性,避免裂纹扩展。

8.因此,亟需解决现有技术中的上述技术问题。

技术实现要素:

9.本发明涉及存内计算模块和方法、存内计算网络及其构建方法。该存内计算模块包括多个子计算模块,各个子计算模块中的计算单元访问内存单元时能够实现低延迟。多个子计算模块呈现的是层对称设计,这种层对称结构便于构造成拓扑网络,以实现大规模

或超大规模计算。每个子计算模块中的内存单元的存储容量可以定制,设计更灵活。多个子计算模块之间通过键合方式连接,且键合连接的数据位宽可以是计算单元的数据位宽的正整数倍,实现了更高的数据带宽。该存内计算网络利用该存内计算模块,能够满足不同规模的计算需求。

10.根据本发明的第一方面,提供了一种存内计算模块,该存内计算模块包括:

11.至少两个计算子模块,该至少两个计算子模块在一方向依次堆叠,且每一计算子模块和与其相邻的计算子模块连接,且每一计算子模块都包括至少一个计算单元和多个内存单元;

12.其中该至少两个计算子模块位于同一个芯片内。

13.由此,包括多个计算模块的存内计算模块能够在实现同一个芯片内的大规模计算,且计算单元在访问内存单元时能够实现低延迟,提高了计算性能。

14.根据本发明的存内计算模块的一个优选实施方案,每一计算子模块包括:

15.一个计算单元;

16.多个内存单元;

17.一个路由单元,该路由单元与该计算单元连接,且该路由单元与该多个内存单元中的每一内存单元连接,且该路由单元与该路由单元所在的存内计算模块的至少另一计算子模块的路由单元连接,以及该路由单元与至少另一存内计算模块的至少另一计算子模块的路由单元连接;

18.其中该路由单元被配置用于执行该路由单元所在的计算子模块的第一计算单元对该路由单元所在的计算子模块的第一内存单元的访问,对该路由单元所在的存内计算模块的至少另一计算子模块的第二计算单元或第二内存单元的访问,或者对至少另一存内计算模块的至少另一计算子模块的第三计算单元或者第三内存单元的访问。

19.根据本发明的存内计算模块的一个优选实施方案,该路由单元包括:

20.路由接口,该路由接口将该路由单元与该路由单元所在的存内计算模块的至少另一计算子模块的路由单元连接,和/或将该路由单元与至少另一存内计算模块的至少另一计算子模块的路由单元连接;

21.内存控制接口,该内存控制接口将该路由单元与该多个内存单元中的每一内存单元连接。

22.根据本发明的存内计算模块的一个优选实施方案,该路由单元还包括:

23.一个交叉开关单元;

24.一个交换路由计算单元,该交换路由计算单元与该路由接口、该交叉开关单元连接,且该交换路由计算单元至少存储有关于该路由单元所在的存内计算模块和该路由单元所在的计算子模块的计算单元的路由信息,该交换路由计算单元对所接收到的数据访问请求进行解析以及基于经解析的数据访问请求信息来控制交叉开关单元的切换;

25.一个内存控制单元,该内存控制单元与该交叉开关单元、该内存控制接口连接,且该内存控制单元至少存储有关于该多个内存单元的路由信息,该内存控制单元响应于该交叉开关单元切换至该内存控制单元,对从该交叉开关单元所接收到的经解析的数据访问请求进行二次解析,以确定目标内存单元,且经由该内存控制接口来访问该目标内存单元。

26.根据本发明的存内计算模块的一个优选实施方案,该计算单元直接地经由该路由

单元访问至少一个内存单元。即,该路由单元对该计算单元所发出的数据访问请求进行解析,直接地从该至少一个内存单元获取访问数据,以及将该访问数据转发至发出数据访问请求的计算单元,其中该数据访问请求至少包括该至少一个内存单元的地址。

27.根据本发明的存内计算模块的一个优选实施方案,该计算单元间接地经由该路由单元访问至少一个另一内存单元。即,该路由单元对该计算单元所发出的数据访问请求进行解析,将经解析的数据访问请求转发至至少另一计算子模块的路由单元且转发至该至少另一计算子模块的路由单元所连接的另一计算单元,间接地经由该另一计算单元从至少一个另一内存单元获取访问数据,以及将该访问数据转发至发出数据访问请求的计算单元,其中该数据访问请求至少包括该至少一个另一内存单元的地址,其中该另一计算单元能够直接地经由路由单元访问该至少一个另一内存单元。

28.由此,通过路由单元实现了计算单元对于内存单元的访问请求的统一分发,且实现了内存控制功能,能够在计算单元访问内存单元时实现进一步的低延迟。另外,能够通过路由单元实现计算子模块之间的互通。

29.根据本发明的存内计算模块的一个优选实施方案,该路由单元与该路由单元所在的存内计算模块的至少另一计算子模块的路由单元通过键合方式连接。

30.由此,多个子计算模块之间能够通过成熟的键合方式连接,实现所需要的电气性能。

31.根据本发明的存内计算模块的一个优选实施方案,该路由单元与该路由单元所在的存内计算模块的至少另一计算子模块的路由单元之间连接的总数据位宽是该计算单元的数据位宽的n倍,其中n为正整数。

32.由此,通过设定路由单元之间连接的数据位宽与单个计算单元的数据位宽之间的关系,能够实现更高的数据带宽。

33.根据本发明的存内计算模块的一个优选实施方案,该多个内存单元的数目是至少根据该计算单元的数据位宽和单个内存单元的数据位宽来确定的。

34.由于内存单元的数目可以根据需求来选定,所以使得设计更为灵活。

35.根据本发明的存内计算模块的一个优选实施方案,在每一计算子模块中,该计算单元、该多个内存单元和该路由单元在相应的计算子模块中的位置是相同的。

36.根据本发明的存内计算模块的一个优选实施方案,在每一计算子模块中,该计算单元和该路由单元位于相应的计算子模块的中心处,该多个内存单元在该相应的计算子模块中围绕该计算单元和该路由单元分布。

37.根据本发明的存内计算模块的一个优选实施方案,该至少两个计算子模块中的各个计算子模块彼此相同。

38.由此,多个子计算模块呈现的是层对称设计,这种层对称结构便于构造成拓扑网络,以实现大规模或超大规模计算。

39.根据本发明的存内计算模块的一个优选实施方案,每一计算子模块包括:

40.至少两个计算单元;

41.多个内存单元;

42.至少两个路由单元,每一路由单元与至少一个计算单元连接,以及每一路由单元与至少一个内存单元连接;

43.该至少两个路由单元彼此连接,以构成整体路由单元,该整体路由单元与该多个内存单元中的每一内存单元连接,该整体路由单元与该整体路由单元所在的存内计算模块的至少另一计算子模块的整体路由单元连接,以及该整体路由单元与至少另一存内计算模块的至少另一计算子模块的整体路由单元连接;

44.其中该整体路由单元被配置用于执行该整体路由单元所在的计算子模块的第一计算单元对该整体路由单元所在的计算子模块的第一内存单元或第二计算单元的访问,对该整体路由单元所在的存内计算模块的至少另一计算子模块的第二内存单元或第三计算单元的访问,或者对至少另一存内计算模块的至少另一计算子模块的第三内存单元或第四计算单元的访问。

45.根据本发明的存内计算模块的一个优选实施方案,该至少两个路由单元中的每一路由单元包括:

46.路由接口,该路由接口将该路由单元与该路由单元所在的计算子模块的至少另一路由单元连接,和/或将该路由单元与该路由单元所在的存内计算模块的至少另一计算子模块的路由单元连接,和/或将该路由单元与至少另一存内计算模块的至少另一计算子模块的路由单元连接;

47.内存控制接口,该内存控制接口将该路由单元与该多个内存单元中的至少一个内存单元连接。

48.根据本发明的存内计算模块的一个优选实施方案,该至少两个路由单元中的每一路由单元还包括:

49.一个交叉开关单元;

50.一个交换路由计算单元,该交换路由计算单元与该路由接口、该交叉开关单元连接,且该交换路由计算单元至少存储有关于该路由单元所在的存内计算模块和该路由单元所在的计算子模块的至少一个计算单元的路由信息,该交换路由计算单元对所接收到的数据访问请求进行解析以及基于经解析的数据访问请求信息来控制交叉开关单元的切换;

51.一个内存控制单元,该内存控制单元与该交叉开关单元、该内存控制接口连接,且该内存控制单元至少存储有关于该多个内存单元中的至少一个内存单元的路由信息,该内存控制单元响应于该交叉开关单元切换至该内存控制单元,对从该交叉开关单元所接收到的经解析的数据访问请求进行二次解析,以确定目标内存单元,且经由该内存控制接口来访问该目标内存单元。

52.根据本发明的存内计算模块的一个优选实施方案,每一计算单元直接地经由该整体路由单元访问至少一个内存单元。即,该整体路由单元对该计算单元所发出的数据访问请求进行解析,直接地从该至少一个内存单元获取访问数据,以及将该访问数据转发至发出数据访问请求的计算单元,其中该数据访问请求至少包括该至少一个内存单元的地址。

53.根据本发明的存内计算模块的一个优选实施方案,每一计算单元间接地经由该整体路由单元访问至少一个另一内存单元。即,该整体路由单元对该计算单元所发出的数据访问请求进行解析,将经解析的数据访问请求转发至至少另一计算子模块的整体路由单元且转发至该至少另一计算子模块的整体路由单元所连接的另一计算单元,间接地经由该另一计算单元从至少一个另一内存单元获取访问数据,以及将该访问数据转发至发出数据访问请求的计算单元,其中该数据访问请求至少包括该至少一个另一内存单元的地址,其中

该另一计算单元能够直接地经由整体路由单元访问该至少一个另一内存单元。

54.根据本发明的存内计算模块的一个优选实施方案,该整体路由单元与该整体路由单元所在的存内计算模块的至少另一计算子模块的整体路由单元通过键合方式连接。

55.根据本发明的存内计算模块的一个优选实施方案,该整体路由单元与该整体路由单元所在的存内计算模块的至少另一计算子模块的整体路由单元之间连接的总数据位宽是该计算单元的数据位宽的n倍,其中n为正整数。

56.根据本发明的存内计算模块的一个优选实施方案,该多个内存单元的数目是至少根据该至少两个计算单元的数据位宽和单个内存单元的数据位宽来确定的。

57.根据本发明的存内计算模块的一个优选实施方案,在每一计算子模块中,该至少两个计算单元、该多个内存单元和该整体路由单元在相应的计算子模块中的位置是相同的。

58.根据本发明的存内计算模块的一个优选实施方案,在每一计算子模块中,该至少两个计算单元和该整体路由单元位于相应的计算子模块的中心处,该多个内存单元在该相应的计算子模块中围绕该至少两个计算单元和该整体路由单元分布。

59.根据本发明的存内计算模块的一个优选实施方案,该至少两个计算子模块中的各个计算子模块彼此相同。

60.根据本发明的存内计算模块的一个优选实施方案,该内存单元包括动态随机存取存储器,该计算单元包括中央处理器。

61.由于动态随机存取存储器的工艺比较成熟,本发明中优选采用此类存储器。

62.根据本发明的存内计算模块的一个优选实施方案,该至少两个计算子模块为两个计算子模块。

63.根据本发明的存内计算模块的一个优选实施方案,该内存单元的存储容量是可定制的。

64.由于内存单元的存储容量可定制,进一步提高了设计的灵活性。

65.根据本发明的第二方面,提供了一种存内计算方法,该存内计算方法用于上述存内计算模块(在该存内计算模块中,一个计算子模块中存在一个路由单元),该存内计算方法包括:

66.路由单元接收数据访问请求,该数据访问请求由第一计算单元发出且至少包括目标内存单元的地址;以及,

67.该路由单元对数据访问请求进行解析,从该目标内存单元获取访问数据且将该访问数据转发至第一计算单元。

68.在此技术方案中,如果目标内存单元与第一计算单元位于同一个存内计算模块内,则“路由单元”指的是该存内计算模块内的路由单元,如果目标内存单元与第一计算单元不位于同一个存内计算模块内,则“路由单元”指的是第一计算单元与目标内存单元之间进行通信所需要的所有路由单元。

69.根据本发明的存内计算方法的一个实施方案,该存内计算方法还包括:

70.在路由单元对数据访问请求进行解析之后且在从该目标内存单元获取访问数据之前,与该第一计算单元连接的路由单元判断该第一计算单元是否能够直接地经由与该第一计算单元连接的路由单元访问该目标内存单元;

71.当该第一计算单元能够直接地经由与该第一计算单元连接的路由单元访问该目标内存单元时,与该第一计算单元连接的路由单元直接地从该目标内存单元获取访问数据且将该访问数据转发至第一计算单元;以及

72.当该第一计算单元不能够直接地经由与该第一计算单元连接的路由单元访问该目标内存单元时,与该第一计算单元连接的路由单元将经解析的数据访问请求转发至第二计算单元,以及经由该第二计算单元从该目标内存单元获取访问数据且将该访问数据转发至第一计算单元。

73.根据本发明的存内计算方法的一个实施方案,该存内计算方法还包括:

74.当该第一计算单元不能够直接地经由与该第一计算单元连接的路由单元访问该目标内存单元时且在与该第一计算单元连接的路由单元将经解析的数据访问请求转发至第二计算单元之前,与该第一计算单元连接的路由单元判断该目标内存单元与该第一计算单元是否位于同一个存内计算模块中;

75.当该目标内存单元与该第一计算单元位于同一个存内计算模块中时,与该第一计算单元连接的路由单元将经解析的数据访问请求转发至与该第一计算单元所连接的路由单元相连接的另一计算子模块的路由单元且转发至该另一计算子模块的路由单元所连接的第二计算单元,以及经由该第二计算单元从该目标内存单元获取访问数据且将该访问数据转发至第一计算单元,其中该第二计算单元能够直接地经由该另一计算子模块的路由单元访问该目标内存单元;

76.当该目标内存单元与该第一计算单元不位于同一个存内计算模块中时,与该第一计算单元连接的路由单元将经解析的数据访问请求转发至与该第一计算单元所连接的路由单元相连接的另一存内计算模块的另一计算子模块的路由单元且转发至该另一存内计算模块的另一计算子模块的路由单元所连接的第二计算单元,以及经由该第二计算单元从该目标内存单元获取访问数据且将该访问数据转发至第一计算单元,其中该第二计算单元能够直接地经由该另一存内计算模块的另一计算子模块的路由单元访问该目标内存单元。

77.根据本发明的第三方面,提供了一种存内计算方法,该存内计算方法用于上述存内计算模块(在该存内计算模块中,一个计算子模块中存在一个路由单元),该存内计算方法包括:

78.路由单元接收数据访问请求,该数据访问请求由第一计算单元发出且至少包括目标计算单元的地址;以及,

79.该路由单元对数据访问请求进行解析,从该目标计算单元获取访问数据且将该访问数据转发至第一计算单元。

80.在此技术方案中,如果目标计算单元与第一计算单元位于同一个存内计算模块内,则“路由单元”指的是该存内计算模块内的路由单元,如果目标计算单元与第一计算单元不位于同一个存内计算模块内,则“路由单元”指的是第一计算单元与目标计算单元之间进行通信所需要的所有路由单元。

81.根据本发明的存内计算方法的一个实施方案,该存内计算方法还包括:

82.在路由单元对数据访问请求进行解析之后且在从该目标计算单元获取访问数据之前,与该第一计算单元连接的路由单元判断该目标计算单元与该第一计算单元是否位于同一个存内计算模块中;

83.当该目标计算单元与该第一计算单元位于同一个存内计算模块中时,与该第一计算单元连接的路由单元将经解析的数据访问请求转发至与该第一计算单元所连接的路由单元相连接的另一计算子模块的路由单元,以及经由该另一计算子模块的路由单元从该目标计算单元获取访问数据且将该访问数据转发至第一计算单元;

84.当该目标计算单元与该第一计算单元不位于同一个存内计算模块中时,与该第一计算单元连接的路由单元将经解析的数据访问请求转发至与该第一计算单元所连接的路由单元相连接的另一存内计算模块的另一计算子模块的路由单元,以及经由该另一存内计算模块的另一计算子模块的路由单元从该目标计算单元获取访问数据且将该访问数据转发至第一计算单元。

85.根据本发明的第四方面,提供了一种存内计算方法,该存内计算方法用于上述存内计算模块(在该存内计算模块中,一个计算子模块中存在至少两个路由单元),该存内计算方法包括:

86.整体路由单元接收数据访问请求,该数据访问请求由该第一计算单元发出且至少包括目标内存单元的地址;以及,

87.该整体路由单元对数据访问请求进行解析,从该目标内存单元获取访问数据且将该访问数据转发至第一计算单元。

88.在此技术方案中,如果目标内存单元与第一计算单元位于同一个存内计算模块内,则“整体路由单元”指的是该存内计算模块内的整体路由单元,如果目标内存单元与第一计算单元不位于同一个存内计算模块内,则“整体路由单元”指的是第一计算单元与目标内存单元之间进行通信所需要的所有整体路由单元。

89.根据本发明的存内计算方法的一个实施方案,该存内计算方法还包括:

90.在整体路由单元对数据访问请求进行解析之后且在从该目标内存单元获取访问数据之前,与该第一计算单元连接的整体路由单元判断该第一计算单元是否能够直接地经由与该第一计算单元连接的整体路由单元访问该目标内存单元;

91.当该第一计算单元能够直接地经由与该第一计算单元连接的整体路由单元访问该目标内存单元时,与该第一计算单元连接的整体路由单元直接地从该目标内存单元获取访问数据且将该访问数据转发至第一计算单元;以及

92.当该第一计算单元不能够直接地经由与该第一计算单元连接的整体路由单元访问该目标内存单元时,与该第一计算单元连接的整体路由单元将经解析的数据访问请求转发至第二计算单元,以及经由该第二计算单元从该目标内存单元获取访问数据且将该访问数据转发至第一计算单元。

93.根据本发明的存内计算方法的一个实施方案,该存内计算方法还包括:

94.当该第一计算单元不能够直接地经由与该第一计算单元连接的整体路由单元访问该目标内存单元时且在与该第一计算单元连接的整体路由单元将经解析的数据访问请求转发至第二计算单元之前,与该第一计算单元连接的整体路由单元判断该目标内存单元与该第一计算单元是否位于同一个存内计算模块中;

95.当该目标内存单元与该第一计算单元位于同一个存内计算模块中时,与该第一计算单元连接的整体路由单元将经解析的数据访问请求转发至与该第一计算单元所连接的整体路由单元相连接的另一计算子模块的整体路由单元且转发至该另一计算子模块的整

体路由单元所连接的第二计算单元,以及经由该第二计算单元从该目标内存单元获取访问数据且将该访问数据转发至第一计算单元,其中该第二计算单元能够直接地经由该另一计算子模块的整体路由单元访问该目标内存单元;

96.当该目标内存单元与该第一计算单元不位于同一个存内计算模块中时,与该第一计算单元连接的整体路由单元将经解析的数据访问请求转发至与该第一计算单元所连接的整体路由单元相连接的另一存内计算模块的另一计算子模块的整体路由单元且转发至该另一存内计算模块的另一计算子模块的整体路由单元所连接的第二计算单元,以及经由该第二计算单元从该目标内存单元获取访问数据且将该访问数据转发至第一计算单元,其中该第二计算单元能够直接地经由该另一存内计算模块的另一计算子模块的整体路由单元访问该目标内存单元。

97.根据本发明的第五方面,提供了一种存内计算方法,该存内计算方法用于上述存内计算模块(在该存内计算模块中,一个计算子模块中存在至少两个路由单元),该存内计算方法包括:

98.整体路由单元接收数据访问请求,该数据访问请求由该第一计算单元发出且至少包括目标计算单元的地址;以及,

99.该整体路由单元对数据访问请求进行解析,从该目标计算单元获取访问数据且将该访问数据转发至第一计算单元。

100.在此技术方案中,如果目标计算单元与第一计算单元位于同一个存内计算模块内,则“整体路由单元”指的是该存内计算模块内的整体路由单元,如果目标计算单元与第一计算单元不位于同一个存内计算模块内,则“整体路由单元”指的是第一计算单元与目标计算单元之间进行通信所需要的所有整体路由单元。

101.根据本发明的存内计算方法的一个实施方案,该存内计算方法还包括:

102.在整体路由单元对数据访问请求进行解析之后且在从该目标计算单元获取访问数据之前,与该第一计算单元连接的整体路由单元判断该目标计算单元与该第一计算单元是否位于同一个存内计算模块中;

103.当该目标计算单元与该第一计算单元位于同一个存内计算模块中时,与该第一计算单元连接的整体路由单元将经解析的数据访问请求转发至与该第一计算单元所连接的整体路由单元相连接的另一计算子模块的另一计算子模块的路由单元,以及经由该另一计算子模块的另一计算子模块的整体路由单元从该目标计算单元获取访问数据且将该访问数据转发至第一计算单元;

104.当该目标计算单元与该第一计算单元不位于同一个存内计算模块中时,与该第一计算单元连接的整体路由单元将经解析的数据访问请求转发至与该第一计算单元所连接的整体路由单元相连接的另一存内计算模块的整体路由单元,以及经由该另一存内计算模块的整体路由单元从该目标计算单元获取访问数据且将该访问数据转发至第一计算单元。

105.根据本发明的第六方面,提供了一种存内计算网络,该存内计算网络包括:

106.多个存内计算模块,该多个存内计算模块为多个上述的存内计算模块,该多个存内计算模块之间通过该多个存内计算模块的路由单元连接。

107.根据本发明的存内计算网络的一个优选实施方案,该多个存内计算模块被连接成总线型、星型、环型、树型、网状和混合型拓扑结构。

108.根据本发明的存内计算网络的一个优选实施方案,该多个存内计算模块之间通过路由单元经由金属线连接。

109.根据本发明的第七方面,提供了一种存内计算模块的构建方法,该构建方法包括:

110.将至少两个计算子模块布置为在一方向依次堆叠;

111.将每一计算子模块布置为与其相邻的计算子模块连接,其中每一计算子模块都包括至少一个计算单元和多个内存单元;

112.其中将该至少两个计算子模块布置于同一个芯片内。

113.根据本发明的构建方法的一个优选实施方案,每一计算子模块包括:一个计算单元;多个内存单元;一个路由单元;

114.该构建方法还包括:

115.将该路由单元与该计算单元连接,且将该路由单元与该多个内存单元中的每一内存单元连接,且将该路由单元与该路由单元所在的存内计算模块的至少另一计算子模块的路由单元连接,以及将该路由单元与至少另一存内计算模块的至少另一计算子模块的路由单元连接;并且,将该路由单元配置用于执行该路由单元所在的计算子模块的第一计算单元对该路由单元所在的计算子模块的第一内存单元的访问,对该路由单元所在的存内计算模块的至少另一计算子模块的第二计算单元或第二内存单元的访问,或者对至少另一存内计算模块的至少另一计算子模块的第三计算单元或者第三内存单元的访问。

116.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

117.将该路由单元的路由接口与该路由单元所在的存内计算模块的至少另一计算子模块的路由单元连接,和/或将该路由单元与至少另一存内计算模块的至少另一计算子模块的路由单元连接;

118.将该路由单元的内存控制接口与该多个内存单元中的每一内存单元连接。

119.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

120.将该路由单元的交换路由计算单元与该路由接口、一个交叉开关单元连接,且至少将关于该路由单元所在的存内计算模块和该路由单元所在的计算子模块的计算单元的路由信息存储在该交换路由计算单元中,以及将该交换路由计算单元配置为对所接收到的数据访问请求进行解析以及基于经解析的数据访问请求信息来控制交叉开关单元的切换;

121.将该路由单元的内存控制单元与该交叉开关单元、该内存控制接口连接,且至少将关于该多个内存单元的路由信息存储在该内存控制单元中,以及将该内存控制单元配置为响应于该交叉开关单元切换至该内存控制单元,对从该交叉开关单元所接收到的经解析的数据访问请求进行二次解析,以确定目标内存单元,且经由该内存控制接口来访问该目标内存单元。

122.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

123.将该计算单元配置为直接地经由该路由单元访问至少一个内存单元。即,该路由单元对该计算单元所发出的数据访问请求进行解析,直接地从该至少一个内存单元获取访问数据,以及将该访问数据转发至发出数据访问请求的计算单元,其中该数据访问请求至少包括该至少一个内存单元的地址。

124.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

125.将该计算单元配置为间接地经由该路由单元访问至少一个另一内存单元。即,该

路由单元对该计算单元所发出的数据访问请求进行解析,将经解析的数据访问请求转发至至少另一计算子模块的路由单元且转发至该至少另一计算子模块的路由单元所连接的另一计算单元,间接地经由该另一计算单元从至少一个另一内存单元获取访问数据,以及将该访问数据转发至发出数据访问请求的计算单元,其中该数据访问请求至少包括该至少一个另一内存单元的地址,其中该另一计算单元能够直接地经由路由单元访问该至少一个另一内存单元。

126.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

127.通过键合方式将该路由单元与该路由单元所在的存内计算模块的至少另一计算子模块的路由单元连接。

128.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

129.将该路由单元与该路由单元所在的存内计算模块的至少另一计算子模块的路由单元之间连接的总数据位宽设置成该计算单元的数据位宽的n倍,其中n为正整数。

130.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

131.至少根据该计算单元的数据位宽和单个内存单元的数据位宽来确定该多个内存单元的数目。

132.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

133.在每一计算子模块中,将该计算单元、该多个内存单元和该路由单元在相应的计算子模块中的位置设置成相同的。

134.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

135.在每一计算子模块中,将该计算单元和该路由单元布置于相应的计算子模块的中心处,将该多个内存单元布置为在该相应的计算子模块中围绕该计算单元和该路由单元分布。

136.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

137.将该至少两个计算子模块中的各个计算子模块设置成彼此相同。

138.根据本发明的构建方法的一个优选实施方案,每一计算子模块包括:至少两个计算单元;多个内存单元;至少两个路由单元,其中每一路由单元与至少一个计算单元连接,以及每一路由单元与至少一个内存单元连接;

139.该构建方法还包括:

140.将该至少两个路由单元彼此连接,以构成整体路由单元,且将该整体路由单元与该多个内存单元中的每一内存单元连接,将该整体路由单元与该整体路由单元所在的存内计算模块的至少另一计算子模块的整体路由单元连接,以及将该整体路由单元与至少另一存内计算模块的至少另一计算子模块的整体路由单元连接;以及,将该整体路由单元配置用于执行该整体路由单元所在的计算子模块的第一计算单元对该整体路由单元所在的计算子模块的第一内存单元或第二计算单元的访问,对该整体路由单元所在的存内计算模块的至少另一计算子模块的第二内存单元或第三计算单元的访问,或者对至少另一存内计算模块的至少另一计算子模块的第三内存单元或第四计算单元的访问。

141.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

142.将该至少两个路由单元中的每一路由单元的路由接口与该路由单元所在的计算子模块的至少另一路由单元连接,和/或与该路由单元所在的存内计算模块的至少另一计

算子模块的路由单元连接,和/或与至少另一存内计算模块的至少另一计算子模块的路由单元连接;

143.将该至少两个路由单元中的每一路由单元的内存控制接口与该多个内存单元中的至少一个内存单元连接。

144.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

145.将该至少两个路由单元中的每一路由单元的交换路由计算单元与该路由接口、一个交叉开关单元连接,且至少将关于该路由单元所在的存内计算模块和该路由单元所在的计算子模块的至少一个计算单元的路由信息存储在该交换路由计算单元中,以及将该交换路由计算单元配置为对所接收到的数据访问请求进行解析以及基于经解析的数据访问请求信息来控制交叉开关单元的切换;

146.将该至少两个路由单元中的每一路由单元的内存控制单元与该交叉开关单元、该内存控制接口连接,且至少将关于该多个内存单元中的至少一个内存单元的路由信息存储在该内存控制单元中,以及将该内存控制单元配置为响应于该交叉开关单元切换至该内存控制单元,对从该交叉开关单元所接收到的经解析的数据访问请求进行二次解析,以确定目标内存单元,且经由该内存控制接口来访问该目标内存单元。

147.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

148.将每一计算单元配置为直接地经由该整体路由单元访问至少一个内存单元。即,该整体路由单元对该计算单元所发出的数据访问请求进行解析,直接地从该至少一个内存单元获取访问数据,以及将该访问数据转发至发出数据访问请求的计算单元,其中该数据访问请求至少包括该至少一个内存单元的地址。

149.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

150.将每一计算单元配置为间接地经由该整体路由单元访问至少一个另一内存单元。即,该整体路由单元对该计算单元所发出的数据访问请求进行解析,将经解析的数据访问请求转发至至少另一计算子模块的整体路由单元且转发至该至少另一计算子模块的整体路由单元所连接的另一计算单元,间接地经由该另一计算单元从至少一个另一内存单元获取访问数据,以及将该访问数据转发至发出数据访问请求的计算单元,其中该数据访问请求至少包括该至少一个另一内存单元的地址,其中该另一计算单元能够直接地经由整体路由单元访问该至少一个另一内存单元。

151.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

152.通过键合方式将该整体路由单元与该整体路由单元所在的存内计算模块的至少另一计算子模块的整体路由单元连接。

153.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

154.将该整体路由单元与该整体路由单元所在的存内计算模块的至少另一计算子模块的整体路由单元之间连接的总数据位宽设置成该计算单元的数据位宽的n倍,其中n为正整数。

155.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

156.至少根据该计算单元的数据位宽和单个内存单元的数据位宽来确定该多个内存单元的数目。

157.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

158.在每一计算子模块中,将该至少两个计算单元、该多个内存单元和该整体路由单元在相应的计算子模块中的位置设置成相同的。

159.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

160.在每一计算子模块中,将该至少两个计算单元和该整体路由单元布置于相应的计算子模块的中心处,以及将该多个内存单元在该相应的计算子模块中设置成围绕该至少两个计算单元和该整体路由单元分布。

161.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

162.将该至少两个计算子模块中的各个计算子模块设置成彼此相同。

163.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

164.将该内存单元设置成包括动态随机存取存储器,且将该计算单元设置成包括中央处理器。

165.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

166.将该至少两个计算子模块设置成两个计算子模块。

167.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

168.将该内存单元的存储容量设置成可定制的。

169.根据本发明的第八方面,提供了一种存内计算网络的构建方法,该构建方法包括:

170.将多个存内计算模块之间通过该多个存内计算模块的路由单元连接,其中该多个存内计算模块为多个上述的存内计算模块。

171.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

172.将该多个存内计算模块连接成总线型、星型、环型、树型、网状和混合型拓扑结构。

173.根据本发明的构建方法的一个优选实施方案,该构建方法还包括:

174.通过路由单元经由金属线连接该多个存内计算模块。

附图说明

175.通过下文结合对附图的说明,将更容易理解本发明,其中:

176.图1是现有技术中的存内计算结构的示意图。

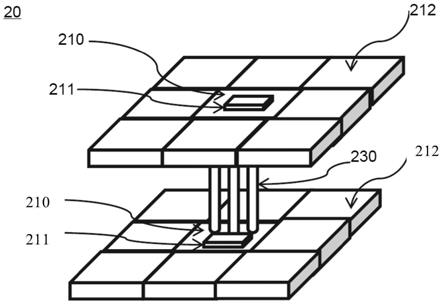

177.图2是根据本发明的一个实施方案的存内计算模块的示意图。

178.图3是根据本发明的一个实施方案的路由单元与计算单元的相对位置以及路由单元的接口的示意图。

179.图4是根据本发明的一个实施方案的路由单元的示意图。

180.图5是根据本发明的一个实施方案的存内计算方法的流程图。

181.图6是根据本发明的另一实施方案的存内计算方法的流程图。

182.图7是根据本发明的一个实施方案的存内计算模块的构建方法的流程图。

183.图8是根据本发明的一个实施方案的存内计算网络的示意图。

具体实施方式

184.下面将结合附图来对本发明的实施方案进行进一步详述。

185.图2是根据本发明的一个实施方案的存内计算模块20的示意图。

186.图2中示出的存内计算模块20包括两个计算子模块(或者称为,两个存内计算

“

层”),上方的计算子模块和下方的计算子模块依次堆叠。如图2中所示,每一计算子模块都包括计算单元210、内存单元212和路由单元211。

187.然而,本发明不限于两个计算子模块,也可以包括多于两个的计算子模块。在多于两个的计算子模块的情况下,这些计算子模块可以在一方向依次堆叠(例如,参照图2中两个计算子模块依次堆叠的情形,在多于两个的计算子模块的情况下,这些计算子模块可以依次在图2中所示出的两个计算子模块上方或下方进行堆叠)。

188.图2中示出的这两个计算子模块距离很近,位于同一个芯片内且构成了一个完整的系统。该完整的系统也称为存内计算模块,又称为存内计算节点。

189.如图2中所示,每一计算子模块包括一个计算单元210、一个路由单元211和八个内存单元212。由于这两个计算子模块21、22位于同一个芯片内,所有的计算单元210和内存单元212也被集成在一起,从而计算单元210在访问内存单元212时的延迟很小。

190.图2中所示出的这两个计算子模块21和22彼此相同,下面主要针对计算子模块21进一步描述。应理解,计算子模块21的所有特征均适用于计算子模块22。

191.内存单元212是用于存储计算单元210中的运算数据以及与硬盘等外存储器交换的数据的单元。由于动态随机存取存储器的工艺比较成熟,所以在本发明中,内存单元212优选地采用动态随机存取存储器。

192.内存单元212的数目是至少根据该计算单元210的数据位宽和单个内存单元212的数据位宽来确定的。

193.例如,如果计算子模块中存在一个计算单元210,该计算单元210的数据位宽为64比特,单个内存单元203的数据位宽为8比特,则所需要的内存单元212的个数是八个(如图2中所示)。

194.另外,内存单元212的存储容量也可以根据需求进行定制。

195.计算单元210是信息处理、程序运行的最终执行单元,优选的是中央处理器。

196.在计算子模块21中,路由单元211与计算单元210以及每一内存单元212连接。另外,计算子模块21中的路由单元211会与计算子模块22中的路由单元211连接。此外,计算子模块21中的路由单元211还会与至少另一存内计算模块的至少另一计算子模块的路由单元211连接。计算子模块21中的路由单元211的主要功能为执行计算子模块21的一个计算单元210对计算子模块21的一个内存单元212的访问,对至少另一计算子模块22的一个计算单元210或一个内存单元212的访问,或者对至少另一存内计算模块的至少另一计算子模块的计算单元210或者内存单元212的访问。

197.计算子模块21中的计算单元210能够“直接地”经由路由单元211访问该计算单元所对应的内存单元212。

198.例如,参考图2,计算子模块21中的计算单元210能够“直接地”经由路由单元211访问计算子模块21中的所有内存单元212。

199.也就是说,如果计算子模块21中的计算单元210发出对于该计算子模块21中的任一个内存单元212的数据访问请求,则该计算子模块21中的路由单元211能够解析该数据访问请求,“直接地”从该计算子模块21中的任一个内存单元212获取访问数据且将访问数据返回至计算单元210。

200.另外,计算子模块21中的计算单元210能够“间接地”经由路由单元211访问另一些

内存单元212。

201.再次参考图2,如果计算子模块21中的计算单元210发出对于计算子模块22中的任一个内存单元212的数据访问请求,则计算子模块21中的路由单元211能够解析该数据访问请求,且将经解析的数据访问请求转发至计算子模块22的路由单元211以及路由单元211所连接的计算单元210,“间接地”经由路由单元211所连接的计算单元210从任一个内存单元212获取访问数据,以及将访问数据返回至发出访问请求的计算单元210。

202.图2中示出了计算子模块21、22中的计算单元210、路由单元211和多个内存单元212的分布的一个实施例,其中计算单210和路由单元211位于相应的计算子模块的中心处,多个内存单元212在该相应的计算子模块中围绕计算单元210和路由单元211分布。

203.然而,这种分布是示意性的而非限制性的。多个内存单元212分布在计算单元210和路由单元211的一侧,或者分布在计算单元210和路由单元211的两侧等也落入本发明的范围内。

204.另外,如图2中所示,在计算子模块21和计算子模块22中,计算单元210、路由单元211和多个内存单元212的位置在相应的计算子模块中是相同的(图2中示出的计算子模块21和计算子模块22彼此相同)。

205.也就是说,图2中示出的存内计算模块20的这些计算子模块21、22具有层对称结构。这种层对称结构便于构造成拓扑网络,以实现大规模或超大规模计算。

206.在图2中,各个计算子模块21、22之间需要借助于路由单元210进行数据接口的连接,优选地采用三维连接230工艺进行连接。

207.常用的三维连接230工艺包括键合方式、硅通孔(through si vias,tsv)、倒装芯片以及晶圆级封装。在本发明中,三维连接230工艺优选地采用键合方式。

208.键合是一种常用的三维连接工艺,是一种芯片内的晶圆堆叠工艺。具体地,键合是将金属线通过一定工艺使晶圆连接在一起,以实现所需要的电气特性。

209.另外,为了缓解数据传输压力,计算子模块21的路由单元211和计算子模块22的路由单元211之间连接的总数据位宽是计算单元210的数据位宽的n倍,其中n为正整数。

210.在图2中,不同计算子模块21、22之间的访问需要经过路由单元210之间的连接。如果连接的总数据位宽和计算单元210相同,在计算子模块21、22之间的数据访问操作频繁(即,数据吞吐率高)的情况下,计算子模块21、22之间的数据吞吐率也随之增加,连接可能出现拥塞。因此,将连接的总数据位宽设置成计算单元210的数据位宽的正整数倍。针对图2中所示出的具体情形,连接的总数据位宽最多是计算单元210的数据位宽的8倍。

211.应理解,正整数n的具体值是根据业务需求来设置的。例如,一般的系统设计可以根据业务仿真得出芯片内的不同计算子模块之间的数据传输的带宽需求,根据带宽需求可以得出所需的数据位宽。

212.假设两个计算子模块21、22之间的数据带宽需求为144gb/s,而现有的连接的总数据位宽为72b、时钟为1ghz,则连接的数据带宽将是72gb/s。此时,就需要考虑将连接的数据位宽提高至144b,以此来适配数据带宽需求。

213.图3是根据本发明的一个实施方案的路由单元211与计算单元210的相对位置以及路由单元211的接口的示意图。

214.如图3中所示,路由单元211围绕计算单元210布置。然而,该布置是示例性而非限

制性的。路由单元211也可以布置在计算单元210的一侧或者两侧,这些也都落入本发明的范围内。

215.图3中还示意性示出了路由单元211的内存控制接口213和路由接口214。这些接口将参照图4进行更加详细的说明。

216.图4是根据本发明的一个实施方案的路由单元的示意图。

217.图4示出了路由单元211的外部接口,这些外部接口主要包括路由接口401和内存控制接口405。应理解,为了不模糊本发明的主旨,图3中仅示出了本发明所涉及到的外部接口,这些外部接口是示例性而非限制性的。

218.在图4中,路由接口示出为内存前端路由(memory front routing,mfr)接口401,这些内存前端路由接口401将该路由单元与该路由单元所在的存内计算模块的至少另一计算子模块的路由单元连接,和/或将该路由单元与至少另一存内计算模块的至少另一计算子模块的路由单元连接。

219.例如,返回参照图2,计算子模块21中的路由单元211的内存前端路由接口401与计算子模块22中的路由单元211的内存前端路由接口401连接,和/或与至少另一存内计算模块的至少另一计算子模块的路由单元的内存前端路由接口401连接。

220.内存控制接口示出为ddr操作接口(ddrio-bonding),该ddr操作接口与每一内存单元212连接。

221.图4中另外示出了路由单元211的内部构造,这些内部构造主要包括交换路由计算单元402、交叉开关单元403和内存控制单元404。应理解,为了不模糊本发明的主旨,图4中仅示出了本发明所涉及到的内部构造,这些内部构造是示例性而非限制性的。应理解,路由单元211也应当包括一些缓冲电路、数字模拟电路等。诸如,缓冲电路会对多个计算单元210的数据访问请求进行缓冲和优先级排序,数字模拟电路诸如可以配合内存控制单元404进行操作,等等。

222.在本发明中,交换路由计算单元402存储有关于计算单元210的路由信息。该路由信息可以以诸如路由表的形式存储。由此,交换路由计算单元402能够确定关于数据访问请求中的计算单元210是否能够“直接地”经由路由器访问一个内存单元的信息等。

223.此外,交换路由计算单元402还存储有关于存内计算模块的路由信息。该路由信息也可以以诸如路由表的形式存储。由此,交换路由计算单元402能够确定内存地址或目标计算单元地址在哪个存内计算模块内(是在本存内计算模块内,还是在另一存内计算模块内)等。例如,基于目标内存地址或目标计算单元地址中的某一特定位置信息(诸如,第一位)与该路由信息,交换路由计算单元402能够判断目标内存地址或目标计算单元地址在哪个存内计算模块内。举例而言,如果目标内存地址或目标计算单元地址的第一位为1,则表示目标内存或目标计算单元在第一存内计算模块中;如果目标内存地址或目标计算单元地址的第一位为3,则表示目标内存或目标计算单元在第三存内计算模块中。

224.内存控制单元404存储有关于内存单元212的路由信息。由此,内存控制单元404能够确定关于数据访问请求中的内存单元对应的端口信息,等等。

225.图5是根据本发明的一个实施方案的存内计算方法的流程图。

226.该存内计算方法包括如下步骤:

227.步骤s501:计算子模块中的路由单元接收数据访问请求。

228.本实施例中的该数据访问请求由该计算子模块中的第一计算单元发出且至少包括目标内存单元的地址。

229.步骤s502:计算子模块中的路由单元对数据访问请求进行解析,该路由单元判断该目标内存单元与该第一计算单元是否位于同一个存内计算模块中。

230.如果该目标内存单元与该第一计算单元不位于同一个存内计算模块中,则执行步骤s503:该路由单元将经解析的数据访问请求转发至与该路由单元相连接的另一存内计算模块的另一计算子模块的路由单元且转发至该另一存内计算模块的另一计算子模块的路由单元所连接的第二计算单元,以及经由该第二计算单元从该目标内存单元获取访问数据且将该访问数据转发至第一计算单元。

231.如果该目标内存单元与该第一计算单元位于同一个存内计算模块中,则执行步骤s504:该路由单元判断该第一计算单元是否能够直接地访问该目标内存单元。

232.如果该第一计算单元能够直接地经由该路由单元访问该目标内存单元,则执行步骤s505:该路由单元直接地从该目标内存单元获取访问数据且将该访问数据转发至第一计算单元。

233.如果该第一计算单元不能够直接地经由该路由单元访问该目标内存单元时,则执行步骤s506:该路由单元将经解析的数据访问请求转发至第二计算单元,以及经由该第二计算单元从该目标内存单元获取访问数据且将该访问数据转发至第一计算单元,其中该第二计算单元能够直接地经由该路由单元访问该目标内存单元。

234.图5中的方法流程图仅是示意性的,并非必须按照此顺序执行。例如,可以先判断第一计算单元是否能够直接地访问该目标内存单元,然后判断目标内存单元与第一计算单元是否位于同一个存内计算模块中。

235.图6是根据本发明的另一实施方案的存内计算方法的流程图。

236.该存内计算方法包括如下步骤:

237.步骤s601:计算子模块中的路由单元接收数据访问请求。

238.本实施例中的该数据访问请求由该计算子模块中的第一计算单元发出且至少包括目标计算单元的地址。

239.步骤s602:计算子模块中的路由单元对数据访问请求进行解析,且该路由单元判断该目标计算单元与该第一计算单元是否位于同一个存内计算模块中。

240.如果该目标计算单元与该第一计算单元位于同一个存内计算模块中,则执行步骤s603:该路由单元将经解析的数据访问请求转发至与该路由单元相连接的另一计算子模块的路由单元,以及经由该另一计算子模块的路由单元从该目标计算单元获取访问数据且将该访问数据转发至第一计算单元。

241.如果该目标计算单元与该第一计算单元不位于同一个存内计算模块中,则执行步骤s604:该路由单元将经解析的数据访问请求转发至与该路由单元相连接的另一存内计算模块的另一计算子模块的路由单元,以及经由该另一存内计算模块的另一计算子模块的路由单元从该目标计算单元获取访问数据且将该访问数据转发至第一计算单元。

242.下面结合图2-图4,针对存内计算模块中如下五种数据流处理的情形来进一步理解路由单元211的外部接口和内部构造以及图5和图6中的存内计算方法。

243.再次参考图2,假设计算子模块21中的计算单元210能够“直接地”经由路由单元

211访问所有内存单元212,计算子模块22中的计算单元210能够“直接地”经由路由单元211访问所有内存单元212。

244.情形(一):计算子模块21中的计算单元210访问计算子模块21中的任一个内存单元212

245.计算子模块21中的计算单元210通过路由接口mfr向交换路由计算单元402发送数据访问请求,交换路由计算单元402对该数据访问请求进行解析得出目标内存地址,且判断目标内存地址是否处于同一存内计算模块内(但是并不解析出具体为哪个内存单元)(在该情形中,判断处于同一存内计算模块内),以及判断出计算子模块21中的计算单元210是否能够“直接地”访问计算子模块21中的任一个内存单元212(在该情形中,判断能够“直接地”访问)。

246.之后,该交换路由计算单元402在其所存储的关于计算单元和存内计算模块的路由信息中查询目标内存地址,确定与目标内存地址对应的端口信息,进而控制交叉开关单元403的打开及闭合,使得将经解析的数据访问请求发送至内存控制单元404中进行二次解析,得出需要具体访问哪个内存单元,之后通过内存控制(ddrio-bonding)接口访问计算子模块21中的任一个内存单元212。

247.情形(二):计算子模块21中的计算单元210访问计算子模块22中的任一个内存单元212

248.计算子模块21中的计算单元210通过路由接口mfr向交换路由计算单元402发送数据访问请求,交换路由计算单元402对该数据访问请求进行解析得出目标内存地址,且判断目标内存地址是否处于同一存内计算模块内(但是并不解析出具体为哪个内存单元)(在该情形中,判断处于同一存内计算模块内),以及判断出计算子模块21中的计算单元210是否能够“直接地”访问计算子模块21中的任一个内存单元212(在该情形中,判断不能够“直接地”访问)。

249.之后,该交换路由计算单元402在其所存储的关于计算单元和存内计算模块的路由信息中查询目标内存地址,确定与目标内存地址对应的端口信息,进而控制交叉开关单元403的打开及闭合,使得将经解析的数据访问请求通过路由接口mfr发送至计算子模块22的路由单元211且发送至计算子模块22的路由单元211所连接的计算单元210,计算子模块22的路由单元211所连接的计算单元210执行如情形(一)中的操作,之后通过内存控制(ddrio-bonding)接口访问计算子模块22中的任一个内存单元212。

250.情形(三):计算子模块21中的计算单元210访问另一存内计算模块的内存单元212

251.计算子模块21中的计算单元210通过路由接口mfr向交换路由计算单元402发送数据访问请求,交换路由计算单元402对该数据访问请求进行解析得出目标内存地址,且判断目标内存地址是否处于同一存内计算模块内(但是并不解析出具体为哪个内存单元)(在该情形中,判断不处于同一存内计算模块内)。

252.之后,该交换路由计算单元402控制交叉开关单元403的打开及闭合,通过路由接口mfr将经解析的数据访问请求发送至另一存内计算模块。

253.另一存内计算模块执行如上述情形(一)和情形(二)中的操作,且之后通过另一存内计算模块的路由单元的内存控制(ddrio-bonding)接口访问另一存内计算模块的内存单元212。

254.情形(四):计算子模块21中的计算单元210访问计算子模块22中的计算单元210

255.计算子模块21中的计算单元210通过路由接口mfr向交换路由计算单元402发送数据访问请求,交换路由计算单元402对该数据访问请求进行解析得出目标计算单元地址,且判断目标计算单元地址是否处于同一存内计算模块内(在该情形中,判断处于同一存内计算模块内)。

256.之后,该交换路由计算单元402在其所存储的关于计算单元和存内计算模块的路由信息中查询目标计算单元地址,确定与目标计算单元地址对应的端口信息,进而控制交叉开关单元403的打开及闭合,通过路由接口mfr访问计算子模块22的路由单元211以及访问计算子模块22的路由单元211所连接的计算单元210。

257.情形(五):计算子模块21中的计算单元210访问另一存内计算模块的计算单元210

258.计算子模块21中的计算单元210通过路由接口mfr向交换路由计算单元402发送数据访问请求,交换路由计算单元402对该数据访问请求进行解析得出目标计算单元地址,且判断目标计算单元地址是否处于同一存内计算模块内(在该情形中,判断不处于同一存内计算模块内)。

259.之后,该交换路由计算单元402控制交叉开关单元403的打开及闭合,通过路由接口mfr将经解析的数据访问请求发送至另一存内计算模块。

260.另一存内计算模块执行如上述情形(四)中的操作,且之后通过路由接口mfr访问另一存内计算模块的路由单元211以及访问另一存内计算模块的路由单元211所连接的计算单元210的访问。

261.图7是根据本发明的一个实施方案的存内计算模块的构建方法的流程图。

262.该存内计算模块的构建方法包括如下步骤:

263.步骤s701:将至少两个计算子模块布置为在一方向依次堆叠。

264.步骤s702:将每一计算子模块布置为与其相邻的计算子模块连接,其中每一计算子模块都包括至少一个计算单元210和多个内存单元212。

265.步骤s703:将该至少两个计算子模块布置于同一个芯片内。

266.图8是根据本发明的一个实施方案的存内计算网络的示意图。

267.图8中所示出的存内计算网络包括:多个存内计算模块80,该多个存内计算模块80为多个如上所述的存内计算模块,该多个存内计算模块80之间通过该多个存内计算模块的路由单元连接。

268.通过将存内计算模块的互联和拓扑,可形成高的数据带宽和高性能计算需求。

269.图8中所示出的是一种典型的网状mesh拓扑结构。应理解,多个存内计算模块80也可以被连接成总线型、星型、环型、树型和混合型拓扑结构。

270.在本发明中,该多个存内计算模块之间通过路由单元经由金属线连接801。此处的金属线连接是传统用于二维连接中的金属线连接。

271.本发明中均是以计算子模块中包括单个路由单元211为实施例。然而,本发明并不限于一个路由单元,也可以包括多于一个的路由单元。在包括多于一个的路由单元的情况下,这些路由单元之间可以通过路由接口mfr连接(类似于一个存内计算模块的路由接口mfr与另一存内计算模块的路由接口mfr之间的操作),构成整体路由单元。

272.该整体路由单元对外部呈现与图2所示的单个路由单元210相同的功能。与图2中

的单个路由单元210的不同之处在于,该整体路由单元中的每一路由单元并非与内存子模块中的每一内存单元都连接。

273.例如,如果计算子模块中存在三个路由单元,这两个路由单元构成整体路由单元。例如,假设图2的计算子模块21中存在三个路由单元:路由单元a、路由单元b和路由单元c,路由单元a与最左侧的三个内存单元212及相关的计算单元210连接,路由单元b与中间的两个内存单元212及相关的计算单元210连接,路由单元c与最右侧的三个内存单元212及相关的计算单元210连接。

274.如果与路由单元a连接的计算单元210需要访问中间的两个内存单元中的任一个,则需要通过路由单元a和路由单元b之间的路由接口mfr进行连接来访问,操作类似于上述情形(三)。具体如下:

275.在路由器a中,与路由单元a连接的计算单元210通过路由单元a的路由接口mfr向交换路由计算单元402发送数据访问请求,交换路由计算单元402对该数据访问请求进行解析得出目标内存地址,且判断目标内存地址是否处于路由器a的寻址范围内(在该情形中,判断不处于路由器a的寻址范围内)。之后,交换路由计算单元402控制交叉开关单元403的打开及闭合,通过路由接口mfr将经解析的数据访问请求发送至路由器b,通过路由器b访问中间的两个内存单元中的任一个。

276.应注意,上文所提及的实施方案例示而非限制本发明,且在不脱离所附权利要求的范围的前提下,本领域技术人员将能够设计许多替代实施方案。应理解,本发明的范围由权利要求限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1