错误检测的制作方法

错误检测

[0001]

本申请要求于2019年9月4日提交的法国专利申请号1909725的优先权权益,其内容在法律允许的最大程度上通过引用以其全部内容结合在此。

技术领域

[0002]

本公开总体上涉及电子系统和电路,并且更具体地涉及包括存储器的电子系统和电路。本公开还更具体地涉及在这些存储器中的数据的读取和写入,并且更具体地涉及在数据的读取和写入期间的错误的检测。

背景技术:

[0003]

在系统或电子电路的操作期间,数据管理通常需要使用一个或多个存储器。例如,在使用之前或之后,从这些存储器写入和/或读取操作数据。

[0004]

在存储器中的数据的读取和/或写入期间可能会遇到许多错误或故障。作为示例,读取错误可包括读取不正确地址处的数据。写入错误可包括在不正确的地址处写入数据。这些错误可以是意外的或故意的。作为示例,故意的错误可由例如由攻击者实施的故障注入方法产生,其目的在于更改电子系统的操作。

[0005]

期望能够至少部分地改进用于在存储器中读取和/或写入数据的方法的某些方面,并且更具体地,改进用于在存储器中读取和/或写入数据中检测错误的方法的某些方面。

[0006]

需要用于在存储器中读取和/或写入数据的更可靠的方法。

[0007]

需要更好地进行用于检测在存储器中读取和/或写入数据中的错误的方法。

[0008]

需要用于在读取和/或写入中检测错误的方法,该方法被配置为检测其中数据在不正确的地址处写入的错误。

技术实现要素:

[0009]

一个实施例解决了用于在存储器中写入数据的已知方法的全部或一些缺点。

[0010]

一个实施例解决了用于在存储器中读取数据的已知方法的全部或一些缺点。

[0011]

一个实施例解决了用于检测在存储器中的读取和/或写入中的错误的已知方法的全部或一些缺点。

[0012]

一个实施例提供了一种用于检测存储器中的数据的写入错误的方法,包括:将表示所述数据的二进制字的相同大小的至少两个部分存储在至少两个相同的存储器电路中的相同地址处;以及比较两个存储器电路的内部控制信号。

[0013]

根据一个实施例,内部信号包括字信号。

[0014]

根据一个实施例,内部信号包括存储器电路中的一个的选择信号。

[0015]

根据一个实施例,内部信号包括写入激活信号。

[0016]

根据一个实施例,内部信号包括选择/列号信号。

[0017]

根据一个实施例,内部信号包括选择/行号信号。

[0018]

根据一个实施例,从所述数据和错误校正或检测码中获得二进制字,该错误校正或检测码表示所述数据和地址。

[0019]

根据一个实施例,二进制字是通过串接数据和错误校正或检测码获得的。

[0020]

根据一个实施例,错误校正或检测码表示数据和地址。

[0021]

根据一个实施例,错误校正或检测码是通过签名方法获得的。

[0022]

另一个实施例提供了一种用于在存储器中写入数据的方法,包括:将表示所述数据和错误校正或检测码的二进制字拆分成至少第一部分和第二部分;以及将第一部分写入在第一存储器电路中的逻辑地址处;并且将第二部分写入第二存储器电路中的逻辑地址处,该第二存储器电路被配置为存储与第一存储器电路一样多的二进制字,错误校正或检测码取决于数据和地址。

[0023]

根据一个实施例,第一部分和第二部分具有相同的大小。

[0024]

根据一个实施例,二进制字是数据与错误校正或检测码的串接。

[0025]

根据一个实施例,数据和地址由单个第一处理器提供。

[0026]

根据一个实施例,数据和地址由至少一个第二处理器和第三处理器提供。

[0027]

根据一个实施例,将由第二处理器提供的数据与由第三处理器提供的数据进行比较,并且将由第二处理器提供的地址与由第三处理器提供的地址进行比较。

[0028]

根据一个实施例,第二处理器将地址提供给至少两个存储器电路中的一个,并且第三处理器将地址提供给至少两个存储器电路中的另一个。

[0029]

根据一个实施例,第二处理器将地址提供给至少两个存储器电路。

[0030]

根据一个实施例,第一存储器电路和第二存储器电路具有相同的大小。

[0031]

根据一个实施例,比较至少两个存储器电路的内部控制信号。

[0032]

另一个实施例提供了一种用于读取根据以上公开的方法写入的数据的方法。

[0033]

根据一个实施例,二进制字是通过串接在第一存储器电路和第二存储器电路中读取的第一部分和第二部分形成的。

[0034]

根据一个实施例,数据是通过从二进制字中去除错误校正或检测码获得的。

[0035]

另一个实施例提供了一种用于检测在由以上公开的方法写入的数据中的错误的方法,其中再次从由以上公开的方法读取的数据中计算错误校正或检测码。

[0036]

根据一个实施例,验证错误校正或检测码。

附图说明

[0037]

将参照附图在通过说明而非限制的方式给出的具体实施例的以下描述中详细描述上述特征和优点以及其他特征和优点,在附图中:

[0038]

图1示意性地并以框图形式示出了电子系统的一个实施例的架构的一部分;

[0039]

图2示意性地并以框图形式示出了图1的系统的架构的另一部分;

[0040]

图3示意性地并以框图形式示出了电子系统的一个实施例的架构的一部分;

[0041]

图4示意性地并以框图形式示出了图3的系统的架构的另一部分;

[0042]

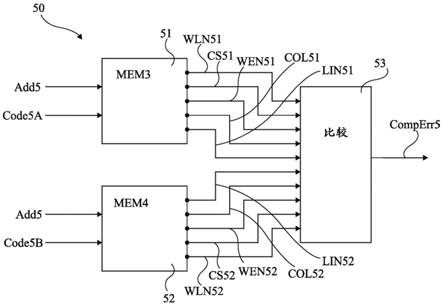

图5示意性地并以框图形式示出了电子系统的一个实施例的架构的一部分;

[0043]

图6示意性地并以框图形式示出了图5的系统的架构的另一部分;

[0044]

图7示意性地并以框图形式示出了电子系统的另一实施例的架构的一部分;

[0045]

图8示意性地并以框图形式示出了图7的系统的架构的另一部分;

[0046]

图9示意性地并以框图形式示出了存储器电路的架构的一部分;并且

[0047]

图10示意性地并以框图形式示出了电子系统的另一实施例的架构的一部分。

具体实施方式

[0048]

在不同的附图中,相同的特征由相同的附图标记表示。具体地,不同实施例中共有的结构和/或功能特征可具有相同的附图标记并且可布置相同的结构、尺寸和材料特性。

[0049]

为了清楚起见,仅详细示出和描述了对于理解本文描述的实施例有用的操作和元件。

[0050]

除非另外指明,否则当提及连接在一起的两个元件时,这表示直接连接而没有除了导体之外的任何中间元件,并且当提及耦接在一起的两个元件时,这表示这两个元件可以连接或者它们可以经由一个或多个其他元件连接。

[0051]

在以下公开内容中,除非另外指明,否则当提及绝对位置限定词时,例如,术语“前”,“后”,“顶部”,“底部”,“左”,“右”等,或提及相对位置限定词时,例如,术语“上方”,“下方”,“较高”,“较低”等,或提及方向限定词时,例如“水平”,“垂直”等,所提及的是图中所示的方向。

[0052]

除非另外指明,否则“左右”,“约”,“基本上”和“大约”的表述表示在10%以内,优选在5%以内。

[0053]

在本公开的其余部分中,将初始二进制字拆分、切割或划分成若干部分将指从初始二进制字的位形成若干次级二进制字。更具体地,每个次级二进制字被构成为使得所有次级二进制字以特定顺序的串接产生初始二进制字。

[0054]

另外,在本说明书的其余部分中,逻辑地址是指由处理器生成的并且旨在用于存储器电路的地址。该地址由与存储器电路相关联的地址解码电路解码,并且该地址解码电路依据存储器平面中的坐标(行-列)提供物理电路。

[0055]

图1示意性地并以框图形式示出了电子系统1的一个实施例的架构的部分10。部分10被配置为将数据写入电子电路1的存储器中。

[0056]

部分10包括:处理器101(cpu);电路102(edc gen),用于产生错误校正或检测码;电路103(edc add),用于形成二进制字;电路104(split,拆分),用于划分二进制字;两个存储器电路105(mem1)和106(mem2);以及地址解码电路107(add dec)。

[0057]

处理器101是被配置为请求将数据写入存储器105和106中的处理器。处理器101提供待写入数据data1和逻辑地址addl1作为输出。地址addl1是数据data1必须写入存储器中的逻辑地址。作为示例,逻辑地址addl1是二进制字,其高权重的位指示必须写入二进制字的存储器电路的行,而低权重的位指示必须写入二进制字的存储器电路的列。

[0058]

用于生成错误校正或检测码的电路102是被配置为计算表示数据data1和逻辑地址addl1的错误检测码(edc)edc1或错误校正码(ecc)的电路。因此,电路102接收数据data1和逻辑地址addl1作为输入,并且提供错误校正或检测码edc1作为输出。举例来说,错误检测码edc1是通过使用签名算法获得的。

[0059]

用于形成二进制字的电路103是被配置为形成表示数据data1和代码edc1的二进制字code1的电路。电路103接收数据data1和代码edc1作为输入,并且提供二进制字code1

作为输出。作为示例,数据data1和代码edc1由电路103串接以便形成二进制字code1。数据data1和代码edc1为了形成二进制字code1而串接的顺序不重要。

[0060]

二进制字划分电路104是被配置为将二进制字code1拆分成几个二进制字的电路。电路104接收二进制字code1作为输入,并且在此示例中,提供两个二进制字code1a和code1b作为输出。换言之,以特定顺序串接的二进制字code1a和code1b产生二进制字code1。二进制字code1a和code1b例如具有不同大小。作为变体,二进制字code1a和code1b大小相同,也就是说,它们各自包括二进制字code1的位的一半。

[0061]

地址解码电路107是被配置为从逻辑地址提供存储器电路可读的物理地址的电路。电路107接收逻辑地址addl1作为输入,并且提供两个物理地址add1a和add1b作为输出。电路107更具体地使得可以从由处理器101提供的逻辑地址addl1定义二进制字code1a和code1b将在存储器电路105和106中写入的两个物理地址add1a和add1b。作为示例,地址add1a和add1b是相同的。

[0062]

存储器电路105和106被配置为将二进制字code1a和code1b分别存储在地址add1a和add1b处。由此,存储器105接收二进制字code1a和地址add1a作为输入,并且存储器106接收二进制字code1b和地址add1b作为输入。存储器电路105和106被配置为存储相同数量的二进制字。存储器电路105和106例如是易失性存储器。作为示例,存储器电路105和106具有相同的大小。

[0063]

作为变体,部分10可包括具有相同结构和大小的两个以上存储器电路。在这种情况下,电路104将被配置为提供与包括在部分10中的存储器电路一样多的二进制字。换言之,电路104被配置为将二进制字code1划分成与部分10中所包括的存储器电路一样多的部分。此外,电路107被配置为从逻辑地址addl1提供与部分10中包括的存储器电路一样多的物理地址。

[0064]

实现系统1的部分10的用于将数据data1写入存储器中的方法如下。当处理器101希望将数据data1存储在存储器中时,处理器101生成其希望存储数据的地址addl1。然后,处理器101将数据data1和逻辑地址addl1提供给电路102,电路102为处理器101生成代码edc1。并行地,通过电路107将地址addl1转换为两个物理地址add1a和add1b。接着,电路103使用数据data1和代码edc1来提供二进制字code1。然后,通过电路104将二进制字code1划分成两个部分,即两个二进制字code1a和code1b。二进制字code1a和code1b在存储器电路105和存储器电路106中分别存储在地址add1a和add1b处。因此,数据data1以二进制字code1a和code1b的形式存储在存储器电路105和106中。

[0065]

图2示意性地并以框图形式示出了电子系统1的实施例的架构的另一部分11,其部分10是结合图1来描述的。部分11被配置为将数据写入电子系统1的存储器中。更具体地,在图2中,部分11被配置为读取结合图1所描述的在地址addl1处写入的数据data1。

[0066]

部分11包括:处理器111(cpu);电路112(edc check,edc检查),用于检查错误校正或检测码;电路113(edc removal,edc去除),用于恢复数据;电路114(merge,合并),用于串接二进制字;两个相同的存储器电路105(mem1)和106(mem2);以及地址解码电路107(add dec)。

[0067]

处理器111是被配置为请求读取存储器105和106中的数据的处理器。处理器111提供地址(例如,结合图1所描述的逻辑地址addl1)作为输出,并且接收与该地址相对应的数

据(也就是说,结合图1所描述的数据data1)作为输入。处理器111例如是与结合图1所描述的处理器101相同的处理器,但是作为变体,处理器111可以是与结合图1所描述的处理器101分开的处理器。

[0068]

用于检查错误校正或检测码的电路112是被配置为检查与数据data1相关联的代码edc1的电路。电路112接收二进制字code1和逻辑地址addl1作为输入,并且提供错误信号erredc1作为输出。为了检查代码edc1,电路112从二进制字code1中找到数据data1和代码edc1。接下来,电路112根据由处理器111提供的数据data1和地址addl1计算新的错误检测或校正码。然后,将新的代码与代码edc1进行比较。如果它们相同,则不存在错误。如果它们不相同,则存在错误。通过信号erredc1指示任何错误。结合图1所公开的电路102是例如电路112的一部分,但是作为变体,电路102和112可以是分开的电路。

[0069]

数据恢复电路113是被配置为从二进制字code1恢复数据data1的电路。电路113接收二进制字code1作为输入,并且提供数据data1作为输出。例如,在二进制字code1是数据data1和代码edc1的串接时,电路113被配置为截断二进制字code1的代码edc1,从而仅保留数据data1。结合图1所描述的电路113和电路103可以例如是同一电路的一部分,或者作为变体,可以是两个分开的电路。

[0070]

二进制字串接电路114是被配置为从两个二进制字code1a和code1b找到二进制字code1的电路。由此,电路114接收二进制字code1a和code1b作为输入,并且提供二进制字code1作为输出。电路114具体地被配置为以正确的顺序串接二进制字code1a和code1b,以便找到初始二进制字code1。结合图1所描述的电路114和电路104可以例如是同一电路的一部分,或者作为变体,可以是两个分开的电路。

[0071]

作为变体,部分10和11可以包括两个以上存储器电路。在这种情况下,电路114被配置为接收与部分10和11中所包括的存储器电路一样多的二进制字作为输入。换言之,电路114被配置为从与包括在部分10和11中的存储器电路一样多的二进制字接收二进制字code1。另外,在这种情况下,电路107被配置为提供尽可能多的物理地址。

[0072]

实现系统1的部分11的用于读取存储器中的数据data1的方法如下。处理器111向电路107提供其希望读取数据的地址addl1,在当前情况下是数据data1。电路107为存储器105和106提供来自逻辑地址addl1的物理地址add1a和add1b。二进制字code1a被存储在存储器电路105的地址add1a处,并且二进制字code1b被存储在存储器电路106的地址add1b处。存储器电路105和106向电路114提供两个二进制字code1a和code1b以改进二进制字code1。电路113的任务是从二进制字code1中提取数据data1并将其发送至处理器111。电路112又通过检查代码edc1来检查是否没有错误。

[0073]

这个实施例的一个优点是,在读取方法期间,电路112使得可以检测数据data1的寻址错误。实际上,代码edc1表示数据data1和写入该数据的逻辑地址addl1,将代码edc1与从处理器111提供的逻辑地址addl1生成的代码进行比较使得可以检测逻辑地址的差异。

[0074]

图3示意性地并以框图形式示出了电子系统2的一个实施例的架构的部分20。部分20被配置为将数据写入电子电路2的存储器中。

[0075]

部分20包括:两个处理器201(cpu1)和202(cpu2);电路203(edc gen),用于生成错误校正或检测码;电路204(edc add),用于形成二进制字;电路205(split,拆分),用于划分二进制字;两个存储器电路206(mem1)和207(mem2);两个地址解码电路209a(add dec1)和

209b(add dec2);以及比较电路208(comp,比较)。

[0076]

处理器201和202是具有相同结构并被配置为提供相同数据和控制的处理器。处理器201和202更具体地是被配置为请求将数据写入存储器206和207中的处理器。每个处理器201、202提供数据data2和逻辑地址addl2作为输出。地址addl2是数据data2必须被写入的逻辑地址。并行地使用两个处理器201和202尤其使得可以通过冗余检查来检测错误。

[0077]

用于生成错误校正或检测码的电路203是与结合图1所公开的电路102相同的电路。电路203接收来自处理器201的数据data2和来自处理器201的逻辑地址addl2作为输入。电路203提供错误校正或检测码edc2作为输出。

[0078]

用于形成二进制字的电路204是与结合图1所公开的电路103相同的电路。电路204接收来自处理器201的代码edc2和数据data2作为输入,并且提供二进制字code2作为输出。

[0079]

用于划分二进制字的电路205是与结合图1所公开的电路104相同的电路。电路205接收二进制字code2作为输入,并且提供对应于二进制字code2的两个部分的两个二进制字code2a和code2b作为输出。

[0080]

电路209a和209b是与结合图1所公开的电路107相似的电路。电路209a接收来自处理器201的逻辑地址addl2,并且提供物理地址add2a作为输出。电路209b接收来自处理器202的逻辑地址addl2,并且提供物理地址add2b作为输出。

[0081]

存储器电路206和207被配置为将二进制字code2a和code2b分别存储在地址add2a和add2b处。存储器电路206和207是被配置为存储相同数量的二进制字的存储器电路。存储器电路206接收二进制字code2a以及来自电路209a的地址ad2a作为输入。存储器电路207接收二进制字code2b以及来自电路209b的地址ad2b作为输入。存储器电路206和207是例如易失性存储器。作为示例,存储器电路206和207具有相同的大小。

[0082]

作为变体,部分20可包括具有相同结构和大小的两个以上存储器电路。在这种情况下,电路205将被配置为提供与部分20中所包括的存储器电路一样多的相同大小的二进制字。换言之,电路205被配置为将二进制字code2划分成与部分20中所包括的存储器电路一样多的二进制字。此外,在这种情况下,电路209a和209b被配置为从逻辑地址addl2提供与部分20中所包括的存储器电路一样多的物理地址。

[0083]

比较电路208是被配置为比较由处理器201和202提供的数据data2以及由处理器201和202提供的逻辑地址addl2的电路。如果两个处理器201和202发送的数据data2或者两个处理器201和202发送的地址addl2不相同,则检测到错误。电路208接收由两个处理器201和202发送的数据data2以及由两个处理器201和202发送的地址addl2作为输入,并且提供错误信号errcomp20作为输出。经由错误信号errcomp20发送由电路208检测到的任何错误。

[0084]

实现系统2的部分20的用于将数据data2写入存储器中的方法如下。当处理器201和202希望将数据data2存储在存储器中时,它们生成它们希望将数据data2存储在存储器中的逻辑地址addl2。然后,处理器201将数据data2和逻辑地址addl2提供给电路203,电路102为处理器201生成代码edc2。并行地,通过电路209a和209b将逻辑地址addl2分别转换成两个物理地址add2a和add2b。因此,代码edc2表示由处理器201提供的数据data2和地址addl2。接着,电路204使用数据data2和代码edc2来提供二进制字code2。接着,二进制字code2由电路205划分成两个二进制字code2a和code2b。二进制字code2a和code2b分别存储在存储器电路206中的地址add2a处和存储器电路207中的地址add2b处。

[0085]

图4示意性地并以框图形式示出了电子系统2的实施例的架构的另一部分21,其部分20是结合图3描述的。部分21被配置为将数据写入电子系统2的存储器中。更具体地,在图4中,部分21被配置为读取如结合图3所描述的在逻辑地址addl2处写入的数据data2。

[0086]

部分21包括:两个处理器211(cpu1)和212(cpu2);电路213(edc check),用于检查错误校正或检测码;电路214(edc removal),用于恢复数据;电路215(merge,合并),用于串接二进制字;以及两个相同的存储器电路206(mem1)和207(mem2);两个地址解码电路209a(add dec1)和209b(add dec2);以及比较电路218(comp)。

[0087]

处理器211和212是与处理器111相同的处理器。处理器211和212各自提供它们希望读取数据的逻辑地址addl2作为输出,并且各自接收数据data2。处理器211和212例如是与结合图3描述的处理器201和202相同的处理器,但是作为变体,处理器211和212可以是与处理器201和202分开的处理器。

[0088]

用于检查错误校正或检测码的电路213是与结合图2所公开的电路112相同的电路。电路213接收处理器211发送的逻辑地址addl2和二进制字code2作为输入,并且提供错误信号erredc2作为输出。结合图3所描述的电路213和电路203可以例如是同一电路的一部分,或者作为变体,可以是两个分开的电路。

[0089]

用于恢复数据的电路214是与结合图2所公开的电路113相同的电路。电路214接收二进制字code2作为输入,并且提供数据data2作为输出。

[0090]

用于串接二进制字的电路215是与结合图2所公开的电路114相同的电路。电路215接收两个二进制字code2a和code2b作为输入,并且提供二进制字code2作为输出。结合图3所描述的电路215和电路205可以例如是同一电路的一部分,或作为变体,可以是分开的电路。

[0091]

电路209a和209b将逻辑地址addl2分别转换为物理地址add2a和add2b。电路209a接收来自处理器211的逻辑地址addl2,并且提供物理地址add2a作为输出。电路209b接收来自处理器212的逻辑地址addl2,并且提供物理地址add2b作为输出。

[0092]

存储器电路206和207将二进制字code2a和code2b分别存储在地址add2a和add2b处。存储器电路206从电路209a接收地址add2a,并且存储器电路207从电路209b接收地址add2b。

[0093]

作为变体,部分20和21可以包括两个以上存储器电路。在这种情况下,电路215被配置为接收与部分20和21中所包括的存储器电路一样多的二进制字作为输入。换言之,电路215被配置为从与包括在部分20和21中的存储器电路一样多的二进制字接收二进制字code2。此外,电路209a和209b被配置为从逻辑地址addl2提供与部分20和21中存在的存储器电路一样多的物理地址。

[0094]

比较电路218是被配置为将由处理器211和212发送的逻辑地址addl2进行比较的电路。比较电路218接收处理器211提供的地址addl2和处理器212提供的地址addl2作为输入,并且提供错误信号errcomp21作为输出。如果处理器211和212发送的逻辑地址不相同,则检测到错误,并且通过错误信号errcomp21发送错误。结合图3所描述的电路218和电路208可以例如是同一电路的一部分,但是作为变体,电路208和218可以是分开的电路。

[0095]

实现系统2的部分21的用于读取存储器中的数据data2的方法如下。处理器211和212向电路209a和209b提供它们希望读取数据的地址addl2,在当前情况下是数据data2。电

路209a和209b将物理地址add2a和add2b提供给存储器电路206和207。比较电路218检查处理器211和212是否正在发送相同的逻辑地址addl2。二进制字code2a被存储在存储器电路206的地址add2a处,并且二进制字code2b被存储在存储器电路207的地址add2b处。存储器电路206和207向电路215提供两个二进制字code2a和code2b以重新形成二进制字code2。电路214占用其自身找到数据data2并将其发送至处理器211和212。电路213进而检查是否没有错误。

[0096]

该实施例的一个优点在于,在读取方法期间,电路213使得可以检测数据data2的寻址错误。实际上,代码edc2表示数据data2和数据被写入的逻辑地址,将代码edc2与从处理器211提供的逻辑地址addl2生成的代码进行比较使得可以检测逻辑地址的差异。

[0097]

这个实施例的另一个优点是并行地使用两个处理器201和202以及211和212,使得可以检测在读取命令或写入命令期间发出的错误。这些错误由电路208和218检测。

[0098]

图5示意性地并以框图形式示出了电子系统3的一个实施例的架构的部分30。部分30被配置为将数据写入电子电路3的存储器中。

[0099]

电子系统3与电子系统2相似,其部分20和21是结合图3和图4进行描述的。系统2和系统3共用的元件将在下文中不再描述。

[0100]

部分30包括与系统2的部分20基本相同的电路。由此,部分30包括:两个处理器201(cpu1)和202(cpu2);电路203(edc gen),用于生成错误校正或检测码;电路204(edc add),用于形成二进制字;电路205(split,划分),用于划分二进制字;两个相同的存储器电路206(mem1)和207(mem2);地址解码电路309(adddec);以及比较电路208(comp)。

[0101]

系统2的部分20与系统3的部分30之间的差异在于,在部分30中,逻辑地址addl2由处理器201发送至电路309,该电路309与结合图1所描述的电路107相同。电路309提供两个物理地址add2a和add2b作为输出。两个存储器电路206和207分别从电路309接收物理地址add2a和add2b。在部分20中,每个存储器电路从不同的解码电路接收物理地址add2a或add2b。在本实施例中,处理器202仅向比较电路208提供逻辑地址addl2。

[0102]

图6示意性地并以框图形式示出了电子系统3的实施例的架构的另一部分31,其部分30是结合图5描述的。电子系统3是优选实施例。部分31被配置为将数据写入电子系统3的存储器中。更具体地,在图6中,部分31被配置为读取结合图3所描述的在地址addl2处写入的数据data2。

[0103]

电子系统3与电子系统2相似,其部分20和21是结合关于图3和图4公开的。系统2和系统3共享的元件将在下文中不再描述。

[0104]

部分31包括系统2的部分21的一些电路。由此,部分31包括:两个处理器211(cpu1)和212(cpu2);电路213(edc check,edc检查),用于检查错误校正或检测码;电路214(edc removal),用于恢复数据;电路215(merge),用于串接二进制字;以及两个相同的存储器电路206(mem1)和207(mem2);地址解码电路309(adddec);以及比较电路218(comp)。

[0105]

系统2的部分21与系统3的部分31之间的区别在于,在部分31中,两个存储器电路206和207从电路309接收地址add2a和add2b。在部分20中,每个存储器电路从不同的地址解码电路接收地址add2a或add2b。在本实施例中,处理器212仅向比较电路218提供逻辑地址addl2。

[0106]

该实施例的一个优点在于,在读取方法期间,电路213使得可以检测数据data2的

寻址错误。实际上,代码edc2表示数据data2和数据被写入的逻辑地址,将代码edc2与从处理器211提供的逻辑地址addl2生成的代码进行比较使得可以检测逻辑地址的差异。

[0107]

这个实施例的另一个优点是,即使由处理器201和202发送的逻辑地址addl2在错误上不同,也将两个二进制字code2a和code2b写在存储器电路206和207中的来自相同逻辑地址addl2的物理地址add2a和add2b处。

[0108]

图7示意性地并以框图形式示出了电子系统4的一个实施例的架构的部分40。部分40被配置为将数据写入电子电路4的存储器中。

[0109]

部分40包括:两个处理器401(cpu1)和402(cpu2);两个电路403(edcgen1)和404(edcgen2),用于生成错误校正或检测码;两个电路405(edc add1)和406(edc add2),用于形成二进制字;电路407(split1)和408(split2),用于划分二进制字;两个相同的存储器电路409(mem1)和410(mem2);两个地址解码电路412(add dec1)和413(add dec2);以及比较电路411(comp)。

[0110]

处理器401和402与结合图3描述的系统2的部分20的处理器201和202相似。处理器401和402具有相同的结构并被配置为提供相同的数据和控制。处理器401和402更具体地是被配置为请求将数据写入存储器409和410中的处理器。每个处理器401、402提供要写入存储器中的数据data4和逻辑地址addl4作为输出。地址addl4是数据data4必须被写入存储器中的逻辑地址。并行地使用两个处理器401和402尤其使得可以通过冗余检查来检测错误。

[0111]

用于生成错误校正或检测码的电路403和404是与结合图1所公开的电路102相同的电路。电路403接收来自处理器401的数据data4和逻辑地址addl4作为输入,并且提供代码edc4作为输出。电路404接收来自处理器402的数据data4和逻辑地址addl4作为输入,并且提供错误校正或检测码edc4作为输出。

[0112]

用于形成二进制字的电路405和406是与结合图1所公开的电路103相同的电路。电路405接收来自电路403的代码edc4作为输入,并且提供二进制字code4作为输出。电路406接收来自电路404的代码edc4作为输入,并且提供二进制字code4作为输出。

[0113]

用于划分二进制字的电路407和408是被配置为将二进制字code4划分为若干二进制字的电路。电路407接收来自电路405的二进制字code4作为输入,并且在此示例中提供二进制字code4和二进制字code2a作为输出。电路408接收来自电路406的二进制字code4作为输入,并且在此示例中提供二进制字code4和二进制字code2b作为输出。

[0114]

地址解码电路412和413是与结合图1所公开的电路107相同的电路。电路412和413将逻辑地址addl4分别转换成物理地址add4a和add4b。电路412接收来自处理器401的逻辑地址addl4,并提供物理地址add4a作为输出。电路413接收来自处理器402的逻辑地址addl4,并提供物理地址add4b作为输出。

[0115]

存储器电路409和410是与结合图1所公开的存储器电路105和106相同的存储器电路。存储器电路409接收来自电路407的二进制字code4a以及来自电路412的地址add4a作为输入。存储器电路410接收来自电路408的二进制字code4b以及来自电路413的地址add4b作为输入。作为示例,存储器电路409和410具有相同的大小。

[0116]

作为变体,部分40可以包括两个以上存储器电路。在这种情况下,部分40包括与部分40中存在的存储器电路一样多的用于生成错误校正或检测码的电路、一样多的用于形成二进制字的电路、以及一样多的用于划分二进制字的电路。另外,二进制字划分电路被配置

为将它们作为输入接收的二进制字划分为与包括在部分40中的存储器电路的数量相等的多个二进制字。地址解码电路412和413被配置为提供与部分40中包括的存储器电路一样多的物理地址。

[0117]

比较电路411是与结合图3公开的电路208相同的电路。电路411接收由处理器401和402发送的数据data4以及由处理器401和402发送的地址addl4作为输入。电路411提供错误信号errcomp40作为输出。

[0118]

实现系统4的部分40的用于将数据data4写入存储器中的方法如下。当处理器401和402希望将数据data4存储在存储器中时,它们生成它们希望将数据data4存储在存储器中的逻辑地址addl4。然后,处理器401(或402)将数据data4和逻辑地址addl4分别提供至电路403(或404),电路403(或404)为其生成代码edc4。并行地,处理器401(或402)将地址addl4分别提供至电路412(或413)以便获得物理地址add4a(或add4b)。因此,代码edc4表示由处理器401和402提供的数据data4和逻辑地址addl4。接着,电路405从由电路403提供的代码edc4和由处理器401提供的数据data4生成二进制字code4。接着,电路406从由电路404提供的代码edc4和由处理器402提供的数据data4生成二进制字code4。电路407和408将分别从电路405和406接收的二进制字code4划分成二进制字code4a和code4b。二进制字code4a存储在存储器409中的由电路412发送的地址add4a处,二进制字code4b存储在存储器410中的由电路413发送的地址add4b处。

[0119]

图8示意性地并以框图形式示出了电子系统4的实施例的架构的另一部分42,其部分40是结合图7描述的。部分42被配置为将数据写入电子系统4的存储器中。更具体地,在图8中,部分42被配置为读取如结合图7所描述的在存储器电路409和410中的逻辑地址addl4处写入的数据data4。

[0120]

部分42包括:两个处理器421(cpu1)和422(cpu2);电路423(edccheck1)和424(edccheck2),用于检查错误校正或检测码;电路425(edc removal1)和426(edc removal2),用于恢复数据;电路427(merge1)和428(merge2),用于串接二进制字;以及两个存储器电路409(mem1)和410(mem2);两个地址解码电路412(add dec1)和413(add dec2);以及比较电路431(comp)。

[0121]

两个处理器421和422是与结合图4公开的处理器211和212相同的处理器。处理器421和422各自提供它们希望读取数据的逻辑地址addl4作为输出,并且各自接收数据data4。处理器421和422例如是与处理器401和402相同的处理器,但是作为变体,处理器421和422可以是与处理器401和402分开的处理器。

[0122]

用于检查错误校正或检测码的电路423和424是与结合图2所公开的电路112相同的电路。电路423接收来自处理器421的逻辑地址addl4和来自电路427的二进制字码4作为输入,并且提供错误信号erredc42作为输出。电路424接收来自处理器422的地址addl4和来自电路428的二进制字code4作为输入,并且提供错误信号erredc42作为输出。电路403和423可以例如是同一电路的一部分,但作为变体,可以是分开的电路。电路404和424可以例如是同一电路的一部分,但作为变体,可以是分开的电路。

[0123]

用于恢复数据的电路425和426是与结合图2所公开的电路113相同的电路。电路425接收来自电路427的二进制字code4作为输入,并且提供数据data4作为输出。电路426接收来自电路428的二进制字code4作为输入,并且提供数据data4作为输出。电路405和425可

以例如是同一电路的一部分,但作为变体,可以是分开的电路。电路406和426可以例如是同一电路的一部分,但作为变体,可以是分开的电路。

[0124]

二进制字串接电路427和428是与结合图2所公开的电路114相同的电路。电路427接收二进制字code4a和code4b作为输入,并且提供二进制字code4作为输出。电路428接收二进制字code4a和code4b作为输入,并且提供二进制字code4作为输出。电路407和427可以例如是同一电路的一部分,但作为变体,可以是分开的电路。电路408和428可以例如是同一电路的一部分,但作为变体,可以是分开的电路。

[0125]

电路412和413将地址addl4分别转换成物理地址add4a和add4b。电路412接收逻辑地址addl4作为输入,并且提供物理地址add4a作为输出。电路413接收逻辑地址addl4作为输入,并且提供物理地址add4b作为输出。

[0126]

存储器电路409和410将二进制字code4a和code4b分别存储在地址add4a和add4b处。存储器电路409从电路412接收地址add4a,存储器电路410从电路413接收地址add4b。

[0127]

作为变体,部分40和42可以包括两个以上存储器电路。在这种情况下,部分42包括与部分41中存在的存储器电路一样多的用于检查错误校正或检测码的电路、一样多的用于恢复数据的电路、以及一样多的二进制字串接电路。另外,多个二进制字划分电路被配置为将它们作为输入接收的二进制字划分为与包括在部分41中的存储器电路的数目相等的多个二进制字。此外,电路412和413被配置为提供与部分42中包括的存储器电路一样多的来自逻辑地址addl4的物理地址。

[0128]

比较电路431是被配置为尤其是将由处理器421和422发送的地址addl4与由电路425和426发送的数据data4进行比较的电路。比较电路431接收由处理器421提供的地址addl4和由处理器422提供的地址addl4作为输入,由接收电路425发送的数据data4和由电路426发送的数据data4作为输出。比较电路431提供错误信号errcomp42作为输出。如果处理器421和422发送的地址不相同,则检测到错误,并且通过错误信号errcomp42发送错误。结合图7所描述的电路431和电路411可以例如是同一电路的一部分,但是作为变体,电路411和431可以是分开的电路。

[0129]

用于读取在存储器中实现系统4的部分42的数据data4的方法如下。处理器421和422向电路412和413提供它们希望读取数据的地址addl4,在当前情况下是数据data4。电路412和413将物理地址add4a和add4b提供给存储器电路409和410。比较电路431检查处理器421和422是否正在发送相同的地址addl4。二进制字code4a被存储在存储器电路409的地址add4a处,并且二进制字code4b被存储在存储器电路410的地址add4b处。存储器电路409和410向电路427和428提供两个二进制字code4a和code4b以重新形成二进制字code4。电路425占用自身从由电路427发送的二进制字code4中找到数据data4,电路426占用自身从由电路428发送的二进制字code4中找到数据data4。然后,处理器421从电路425接收数据data4,并且处理器422从电路426接收数据data4。比较电路431检查提供给处理器421和422的数据data4之间的对应关系。电路423和424各自在其一侧检查代码edc4。

[0130]

该实施例的一个优点在于,在读取方法期间,电路423和424使得可以检测数据data4的寻址错误。实际上,代码edc4表示数据data4和数据被写入的逻辑地址,将代码edc4与从处理器421和422提供的逻辑地址addl4生成的代码进行比较使得可以检测地址上的差异。

[0131]

该实施例的另一个优点是并行地使用两个处理器401和402以及421和422,使得可以检测在读取控制或写入控制过程中所发出的错误。这些错误由电路411和431检测。

[0132]

图9示意性地并以框图形式示出了存储器电路mem的一部分。存储器电路mem例如是由结合图1至8公开的系统1至4使用的存储器电路类型。

[0133]

存储器电路mem的部分包括控制电路logic(逻辑)和线控制电路wl。

[0134]

控制电路logic是被配置为处理从存储器电路mem所属的系统接收的各种控制的电路。电路logic接收地址add和待写入的数据data作为输入。电路logic提供以下信号作为输出:用于选择存储器电路mem的信号cs;用于激活写入的信号wen;选择/列号信号col;以及选择/行号信号lin。

[0135]

地址add优选地是物理地址,也就是说,能够被直接解释为存储器电路中的行和列坐标。在变体中,该地址是由处理器提供的并且由与存储器电路相关联的地址解码电路(也就是说,属于存储器电路)转换的逻辑地址。

[0136]

信号cs使得可以在读取或写入操作期间选择存储器电路mem。

[0137]

信号wen使得可以向存储器电路mem指示所接收的控制的性质,并且更具体地,指示是否请求写入操作。

[0138]

信号col和lin是从由电路logic接收的地址add生成的信号,并且是使得可以选择希望写入数据data的存储器电路的存储器点(在图9中未示出)的信号。

[0139]

行控制电路wl是被配置为选择对应于由存储器电路接收的地址add的字线的电路。电路wl接收行选择/号信号lin作为输入,并且提供字wln作为输出。在图9中,仅示出一个字wln。

[0140]

图10示意性地并以框图形式示出了电子系统5的架构的部分50。部分50被配置为当在存储器中写入数据时检测错误。

[0141]

系统5的部分50包括:两个存储器电路51(mem3)和52(mem4);以及比较电路53(comp)。

[0142]

存储器电路51和52是具有与结合图9所公开的存储器mem的类型相同的结构和尺寸的存储器电路。因此,存储器电路51和52各自接收物理地址add5作为输入。存储器电路51还接收要存储在地址add5处的二进制字码5a作为输入。存储器电路52还接收要存储在地址add5处的二进制字码5b作为输入。如结合图9所公开的,每个存储器电路51(或52)提供以下输出信号作为输出:字wln51(或wln52);信号cs51(或cs52),用于选择存储器电路51(或存储器电路52);信号wen51(或wen52),用于激活写入;选择/列号信号col51(或col52);以及选择/行号信号lin51(或lin52)。

[0143]

二进制字code5a和code5b是相同大小的二进制字,两者都表示要写入存储器中的数据。作为示例,二进制字code5a和code5b是通过将待写入存储器中的数据分为两半获得的。根据另一实例,以与结合图1描述的二进制字code1a及code1b相同的方式获得二进制字code5a及code5b。

[0144]

比较电路53是使得可以比较两个存储器电路51和52的输出信号以便在写入操作期间检测错误的电路。比较电路53接收以下信号作为输入:字wln51和wln52;信号cs51和cs52;信号wen51和wen52;信号col51和col52;以及信号lin51和lin52。

[0145]

比较电路53提供比较信号comperr5作为输出。比较电路53更具体地将存储器电路

51的每个输出信号与存储器52的对应输出信号进行比较。换言之,比较电路53被配置为:比较字wln51和wln52;比较信号cs51和cs52;比较信号wen51和wen52;比较信号col51和col52;以及比较信号lin51和lin52。

[0146]

比较电路53可以是异或类型的逻辑门的组件。

[0147]

作为变体,部分50可以包括多于两个存储器电路。在这种情况下,比较电路53被配置为接收部分50的存储器电路的所有输出信号作为输入。另外,这些存储器电路中的每个存储器电路被配置为存储表示要被写入存储器中的数据的二进制字,该二进制字与存储在其他存储器电路中的二进制字不同。

[0148]

实现系统5的部分50的用于检测读取错误的方法如下。在将二进制字code5a和code5b在地址add5写入存储器电路51和52期间,存储器电路51和52将它们的输出信号发送到比较电路53。二进制字code5a和code5b是相同大小的二进制字,存储在相同存储器电路中的相同地址处,因此,存储器电路51和52的输出信号应是相同的。然后,比较电路53比较存储器电路51和52的输出信号,两个信号之间的每个差异都表示错误。潜在的错误通过信号comperr5发送。

[0149]

这个实施例的一个优点是,其使得可以在存储器中的数据的写入操作期间检测地址错误,而不需要所述数据的读取操作。

[0150]

已经描述了不同实施例和变体。本领域技术人员将理解,这些实施例的某些特征可以组合,并且本领域技术人员将容易想到其他变体。

[0151]

具体地,结合图1和2、图3和图4、图5和图6以及图7和图8所公开的实施例都与结合图9和10所公开的实施例兼容。

[0152]

另外,结合图3和图4、图5和图6以及图7和图8所公开的实施例包括两个相同的处理器,但是作为变体,这些实施例可以包括多于两个处理器。

[0153]

最后,基于上文提供的功能描述,本文描述的实施例和变体的实际实现在本领域技术人员的能力范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1