一种寄存器验证方法、装置、设备及存储介质与流程

1.本技术涉及寄存器验证技术,尤其涉及一种寄存器验证方法、装置、设备及存储介质。

背景技术:

2.现有的寄存器验证技术中,对于单线程寄存器的验证已经实现自动化验证,对于多线程寄存器的验证,现有技术还不能很好处理复杂的多线程激励来实现对寄存器的并行访问验证,且在验证过程中对于激励自动产生,无法自动筛除错误激励或重复激励,会减缓验证收敛速度,验证周期较长。

技术实现要素:

3.为解决上述技术问题,本技术实施例期望提供一种寄存器验证方法、装置、设备及存储介质。

4.本技术的技术方案是这样实现的:

5.第一方面,提供了一种寄存器验证方法,该方法包括:

6.控制激励生成单元生成验证目标寄存器的测试激励;

7.检测到所述测试激励为多线程激励,基于所述多线程激励在所述目标寄存器的寄存器模型中设置第一寄存器信息,并且将所述多线程激励并行输入到所述目标寄存器,输出第二寄存器信息;

8.基于所述第一寄存器信息和所述第二寄存器信息对所述目标寄存器进行验证,得到验证结果;

9.将所述验证结果反馈到所述激励生成单元,使所述激励生成单元在生成新的多线程测试激励时过滤掉重复的冲突激励。

10.第二方面,提供了一种寄存器验证装置,该装置包括:

11.激励产生单元,用于生成验证目标寄存器的测试激励;

12.验证单元,用于检测到所述测试激励为多线程激励,基于所述多线程激励在所述目标寄存器的寄存器模型中设置第一寄存器信息,并且将所述多线程激励并行输入到所述目标寄存器,输出第二寄存器信息;

13.监视单元,用于基于所述第一寄存器信息和所述第二寄存器信息对所述目标寄存器进行验证,得到验证结果;

14.所述监视单元,还用于将所述验证结果反馈到所述激励生成单元;

15.所述激励生成单元,还用于基于所述验证结果在生成新的多线程测试激励时过滤掉重复的冲突激励。

16.第三方面,本技术实施例中又提供了一种寄存器验证设备,包括:处理器和配置为存储能够在处理器上运行的计算机程序的存储器,

17.其中,所述处理器配置为运行所述计算机程序时,执行前述方法的步骤。

18.第四方面,本技术实施例中还提供了一种计算机存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现前述方法的步骤。

19.本技术实施例提供了一种寄存器验证方法、装置、设备及存储介质,该方法包括:控制激励生成单元生成验证目标寄存器的测试激励;检测到所述测试激励为多线程激励,基于所述多线程激励在所述目标寄存器的寄存器模型中设置第一寄存器信息,并且将所述多线程激励并行输入到所述目标寄存器,输出第二寄存器信息;基于所述第一寄存器信息和所述第二寄存器信息对所述目标寄存器进行验证,得到验证结果;将所述验证结果反馈到所述激励生成单元,使所述激励生成单元在生成新的多线程测试激励时过滤掉重复的冲突激励。这样,在验证多线程访问寄存器的过程中,通过将寄存器的验证结果反馈给激励生成单元,可以在后续激励的生成过程中过滤掉冲突激励,从而避免因使用冲突激励导致验证收敛速度降低的问题,缩短寄存器的验证周期,节约验证成本。

附图说明

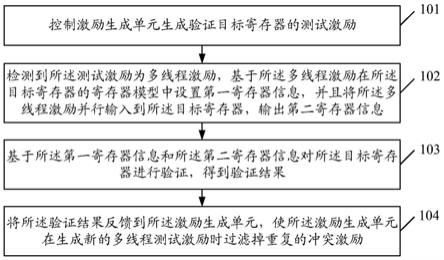

20.图1为本技术实施例中寄存器验证方法的第一流程示意图;

21.图2为本技术实施例中验证平台的第一组成结构示意图;

22.图3为本技术实施例中双线程访问冲突示意图;

23.图4为本技术实施例中寄存器验证方法的第二流程示意图;

24.图5为本技术实施例中寄存器验证方法的第三流程示意图;

25.图6为本技术实施例中验证平台的第二组成结构示意图;

26.图7为本技术实施例中寄存器验证装置的组成结构示意图;

27.图8为本技术实施例中寄存器验证设备的组成结构示意图。

具体实施方式

28.为了能够更加详尽地了解本技术实施例的特点与技术内容,下面结合附图对本技术实施例的实现进行详细阐述,所附附图仅供参考说明之用,并非用来限定本技术实施例。

29.本技术实施例提供了一种寄存器验证方法,如图1所示,该方法具体可以包括:

30.步骤101:控制激励生成单元生成验证目标寄存器的测试激励;

31.实际应用中,激励生成单元可以随机生成测试激励,用于测试目标寄存器的读写功能和任务处理性能。

32.在一些实施例中,基于预设的激励约束条件,控制激励生成单元生成验证目标寄存器的测试激励;其中,所述激励约束条件是根据所述目标寄存器的验证需求设定的。

33.这里,寄存器的验证需求是寄存器实现功能有关。比如,寄存器需要实现先写后读的功能,则验证需求可以包括验证寄存器对于多线程激励是否能够实现先写后读。相应的,激励约束条件包括生成先写后读的多线程激励。通过设定激励约束条件相比于不受任何约束的随机生成方式的能够缩小测试激励范围,过滤掉很多无用激励,加快验证收敛速度,缩短验证周期。

34.进一步地,激励生成单元既可以生成单线程激励也可以生成多线程激励。由于单线程激励在访问寄存器时不存在冲突问题,因此只能用来测试寄存器读写功能是否正确。多线程激励可能存在冲突问题,因此即可以用来测试寄存器读写功能是否正确,还可以进

一步测试寄存器任务处理性能。

35.步骤102:检测到所述测试激励为多线程激励,基于所述多线程激励在所述目标寄存器的寄存器模型中设置第一寄存器信息,并且将所述多线程激励并行输入到所述目标寄存器,输出第二寄存器信息;

36.实际应用中,该方法还包括为目标寄存器构建寄存器模型,利用寄存器模型对多线程访问寄存器进行验证。这里,寄存器模型是一组高级抽象的类,用来对待验证设计(design under test,dut)(即目标寄存器)中具有地址映射的寄存器和存储器进行建模。它非常贴切的反映dut中寄存器的各种特性,可以产生激励作用于dut并进行寄存器功能检查。通过通用验证方法学(universal verification methodology,uvm)构建的寄存器模型,可以简单高效的实现对dut的寄存器进行前门或后门操作。它本身也提供了一些寄存器测试的sequence(即激励发声单元),方便用户直接使用。

37.现有技术中处理器每次都会并行处理很多指令,常规的读写寄存器指令的验证已经不能满足大规模处理器寄存器验证的需求。本技术实施例中,基于寄存器模型以及并行访问寄存器的方法,能够对多线程访问寄存器进行自动验证。

38.在一些实施例中,所述将所述多线程激励并行输入到所述目标寄存器,输出第二寄存器信息,包括:基于所述多线程激励中每个线程的线程标识,确定每个线程对应的驱动器;将每个线程分别送入到各自对应的驱动器中;控制多个驱动器将所述多线程激励同时驱动到所述目标寄存器的多个接口,以实现对所述目标寄存器的多线程访问;利用多个监视器分别监视所述多个接口,得到所述第二寄存器信息。

39.也就是说,在寄存器验证平台中设置多个并列的驱动器,一个驱动器用于处理一个线程任务,激励生成单元可以根据线程和驱动器的对应关系,将每个线程送入到对应的驱动器。对于能够处理多线程任务的共享寄存器而言包括多个接口,一个驱动器连接一个接口,用于实现多线程的并行访问,一个监视器连接一个接口,用于监视每个线程的访问结果。

40.图2为本技术实施例中验证平台的第一组成结构示意图,如图2所示,验证平台包括:测试用例、验证环境(env)和待测组件(dut)。

41.测试用例包括:覆盖监视器(coverage monitor)、寄存器模型(reg model)和序列(sequence),这里,sequence也称为激励产生单元。

42.验证环境包括:适配器0(adapter0)、序列发生器(sequencer)、4个并列驱动器(d0、d1、d2和d3),4个并列监视器(m0、m1、m2和m3)、预测器(predictor)、适配器1(adapter1)和dut的参考模型(reference model)。

43.从图2中可以看出,本技术通过设置多个并列驱动器和监视器能够处理复杂的多线程激励,实现对dut的并行访问验证。

44.图2中4个并列的驱动器和4个并列的监视器只是为了示意多线程并行访问验证过程,并不是限定只能处理4个线程,本技术实施例提供的寄存器验证方法,能够验证2个及以上线程的对寄存器的并行访问,其他数量的多线程访问验证方法与图2这种4线程访问验证方法同理。

45.步骤103:基于所述第一寄存器信息和所述第二寄存器信息对所述目标寄存器进行验证,得到验证结果;

46.本技术实施例中,目标寄存器是能够处理并行任务的共享寄存器,多线程激励验证共享寄存器时,包括对寄存器进行读写验证和多线程冲突验证。这里,读写验证是为了验证每个线程对寄存器的读操作或写操作是否正确,只有寄存器的读写正确时,才会进一步验证多线程访问寄存器时是否存在冲突。

47.在一些实施例中,步骤103具体可以包括:基于所述第一寄存器信息和所述第二寄存器信息对所述目标寄存器进行读写验证,得到第一验证结果;所述第一验证结果表征所述目标寄存器的读写功能验证成功时,基于所述第二寄存器信息对所述多线程激励进行冲突验证,得到第二验证结果;

48.相应的,所述将所述验证结果反馈到所述激励生成单元,包括:将所述第二验证结果反馈到所述激励生成单元。

49.也就是说,第二寄存器信息中的一部分信息用于验证寄存器的读写功能是否正确,另一部分信息用于验证多线程激励是否冲突。

50.具体的,第一寄存器信息包括每个线程访问所述目标寄存器时的期望值和镜像值,所述第二寄存器信息包括每个线程访问所述目标寄存器时的真实值,第一寄存器信息中的期望值和镜像值和第二寄存器的真实值用来验证寄存器的读写功能是否正确。第二寄存器信息还包括每个线程访问所述目标寄存器时的执行顺序和执行状态,用来验证多线程访问是否冲突,其中,所述执行状态为读状态或写状态。

51.以图2为例对验证过程进行举例说明,实际应用中dut的验证过程具体包括:sequence产生多线程激励,将每个线程的期望值(m_desired)给寄存器模型,在寄存器模型中通过映射m_desired产生镜像值(m_mirrored),并且将多线程激励发送给adapter0,在adapter0中,调用reg_adapter.reg2bus将rw转换成bus driver对应的transaction;把transaction交给sequencer,最终由多个并列的bus driver(例如d0、d1、d2和d3)驱动到对应的多个bus interface(例如i0、i1、i2和i3)上。与多个bus interface相连的多个bus monitor(例如m0、m1、m2和m3)检测到bus transaction,并送给predictor。

52.predictor会调用adapter1.bus2reg将该bus transaction转换成uvm_reg_item,adapter1通过队列的形式将每个线程访问寄存器的uvm_reg_item以队列的形式写入到寄存器模型。寄存器模型根据返回的uvm_reg_item来更新寄存器的真实值(value),coverage monitor实时监视每个线程访问寄存器的真实值(value)以及镜像值(m_mirrored)和期望值(m_desired)并比较来验证寄存器读写的正确性,同时还可以根据每个线程对寄存器的执行信息来实时判断多线程访问共享寄存器会不会产生冲突,并反馈给sequence,对产生冲突的测试激励进行记录并关闭其运行。

53.图3为本技术实施例中双线程访问冲突示意图,如图3所示,双线程激励包括:线程1(线程标识为id0)和线程2(线程标识为id1);(w,5)表示线程1对目标寄存器执行写5操作,(r)表示线程2对目标寄存器执行读操作,为了使两个线程访问正确需要先执行线程1后执行线程0,但根据目标寄存器的竞争冒险机制,实际访问结果为先执行线程0后执行线程1,导致线程2实际读到的值并不是目标寄存器中之前存储的6,所以这种双线程访问寄存器时很大概率会导致访问错误的情况出现,会影响验证的收敛速度,因此将这种双线程激励定义为冲突激励。

54.实际应用中,当目标寄存器的读写功能验证失败时,需要分析读写问题并修改,之

后利用多线程激励对寄存器进行重新访问,直到读写验证成功再进一步验证多线程激励是否冲突。

55.步骤104:将所述验证结果反馈到所述激励生成单元,使所述激励生成单元在生成新的多线程测试激励时过滤掉重复的冲突激励。

56.实际应用中,验证结果中至少包括冲突激励的标识信息,激励生成单元可以根据冲突激励的标识信息确定冲突激励并删除冲突激励。由于运行冲突激励会使后期回归测试带来很大代价,延缓收敛验证速度,因此删除冲突激励可以缩短寄存器的验证周期,节约验证成本。

57.在一些实施例中,当多线程激励为正确激励时,验证结果中还可以包括正确激励的标志信息,由于再利用正确激励验证目标寄存器结果还是验证成功,因此,没有必要再利用正确激励去验证目标寄存器来浪费验证时间,可以将重复的正确激励删除,来进一步缩短验证周期。

58.这里,步骤101至步骤104的执行主体可以为寄存器验证设备的处理器。该方法可以基于uvm来构建验证平台,uvm是一个以system verilog类库为主体的验证平台开发框架,验证工程师可以利用其可重用组件构建具有标准化层次结构和接口的功能验证环境。

59.采用上述技术方案,在验证多线程访问寄存器的过程中,通过将寄存器的验证结果反馈给激励生成单元,可以在后续激励的生成过程中过滤掉冲突激励,从而避免因使用冲突激励导致验证收敛速度降低的问题,缩短寄存器的验证周期,节约验证成本。

60.为了能更加体现本技术的目的,在本技术上述实施例的基础上,进行进一步的举例说明,如图4所示,该方法具体包括:

61.步骤401:控制激励生成单元生成验证目标寄存器的多线程激励;

62.实际应用中,激励生成单元可以随机生成测试激励,或者基于预设的激励约束条件生成验证目标寄存器的测试激励。

63.进一步地,激励生成单元既可以生成单线程激励也可以生成多线程激励。由于单线程激励在访问寄存器时不存在冲突问题,因此只能用来测试寄存器读写功能是否正确。多线程激励可能存在冲突问题,因此即可以用来测试寄存器读写功能是否正确,还可以进一步测试寄存器任务处理性能。

64.步骤402:基于所述多线程激励在所述目标寄存器的寄存器模型中设置第一寄存器信息;

65.以图2为例,sequence产生多线程激励,将每个线程的期望值(m_desired)给寄存器模型,在寄存器模型中通过映射m_desired产生镜像值(m_mirrored),每个线程的m_desired和m_mirrored可以作为第一寄存器信息。

66.步骤403:基于所述多线程激励中每个线程的线程标识,确定每个线程对应的驱动器;

67.本技术实施例,在寄存器验证平台中设置多个并列的驱动器,一个驱动器用于处理一个线程任务,激励生成单元可以根据线程和驱动器的对应关系,将每个线程送入到对应的驱动器。对于能够处理多线程任务的共享寄存器而言包括多个接口,一个驱动器连接一个接口,用于实现多线程的并行访问,一个监视器连接一个接口,用于监视每个线程的访问结果。

68.步骤404:将每个线程分别送入到各自对应的驱动器中;

69.步骤405:控制多个驱动器将所述多线程激励同时驱动到所述目标寄存器的多个接口,以实现对所述目标寄存器的多线程访问;

70.步骤406:利用多个监视器分别监视所述多个接口,得到所述第二寄存器信息;

71.在一些实施例中,所述第二寄存器信息包括每个线程访问所述目标寄存器时的真实值、执行顺序和执行状态;其中,所述执行状态为读状态或写状态;

72.相应的,该步骤具体包括:利用所述多个监视器分别监视所述多个接口,基于每个线程的执行顺序从所述多个接口分别获取每个线程访问所述目标寄存器时的真实值和执行状态;基于每个线程访问所述目标寄存器时的执行顺序,将每个线程的真实值和执行状态依次存入到目标队列中;从所述目标队列中获取所述第二寄存器信息。

73.步骤407:基于所述第一寄存器信息和所述第二寄存器信息对所述目标寄存器进行读写验证,得到第一验证结果;

74.这里,第一验证结果表征读写功能验证成功或表征读写功能验证失败。

75.在一些实施例中,所述第一寄存器信息包括每个线程访问所述目标寄存器时的期望值和镜像值;所述第二寄存器信息包括每个线程访问所述目标寄存器时的真实值;

76.相应的,所述基于所述第一寄存器信息和所述第二寄存器信息对所述目标寄存器进行读写验证,得到第一验证结果,包括:所述多线程激励中所有线程访问所述目标寄存器时的期望值、镜像值和真实值相同时,确定所述目标寄存器的读写功能验证成功;所述多线程激励中至少部分线程访问所述目标寄存器的期望值、镜像值和真实值不相同时,确定所述目标寄存器的读写功能验证失败。

77.示例性的,双线程激励访问目标寄存器时,双线程包括:线程1(id0)对目标寄存器执行写5操作,线程2(id1)对目标寄存器执行读操作,为了使两个线程访问正确需要先执行线程1后执行线程0,通过驱动器0(d0)将线程1送入到接口0(i0),通过驱动器1(d1)将线程2送入到接口1(i1),监视器0(m0)监视i0得到线程1的访问结果,比如监视到写5操作,监视器1(m1)监视i1得到线程2的访问结果,比如监视到读6,且m1先监视到m0后监视到,则目标队列中先存入线程2的访问结果,再存入线程1的访问结果,并且id0对应的三个值都为5,id1对应的三个值都为6,表明每个线程的读写结果均正确,寄存器读写功验证成功;若存在至少一个线程对应的三个值不相同,表明寄存器读写功能验证失败。

78.在一些实施例中,该方法还包括:所述第一验证结果表征所述目标寄存器的读写功能验证失败时,生成修改提示信息,以提示所述目标寄存器读写功能异常。

79.实际应用中,当目标寄存器的读写功能验证失败时,需要分析读写问题并修改,之后利用多线程激励对寄存器进行重新访问,直到读写验证成功再进一步验证多线程激励是否冲突。

80.步骤408:所述第一验证结果表征所述目标寄存器的读写功能验证成功时,基于所述第二寄存器信息对所述多线程激励进行冲突验证,得到第二验证结果;

81.在一些实施例中,所述第二寄存器信息还包括每个线程访问所述目标寄存器时的执行顺序和执行状态;其中,所述执行状态为读状态或写状态;

82.相应的,所述基于所述第二寄存器信息对所述多线程激励进行冲突验证,得到第二验证结果,包括:基于每个线程访问所述目标寄存器时的执行顺序和执行状态,判断所述

多线程激励是否与预设的冲突特征匹配;若匹配,确定所述多线程激励为冲突激励;若不匹配,确定所述多线程激励为正确激励。

83.这里,预设的冲突特征是根据目标寄存器可能存在的冲突类型预先设定的。示例性的,所述冲突特征包括以下至少一种写后读、写后写、读后写。比如,对于某些特殊的寄存器不能出现写后读和写后写的情况,或者不能出现读后写的情况。因此通过提取每种冲突类型的冲突特征,将所有冲突特征存放到冲突列表中,在验证冲突时将每个线程访问所述目标寄存器时的执行顺序和执行状态与冲突列表中的冲突特征进行匹配,如果存在匹配上的冲突特征则表明多线程激励为冲突激励,否则为非冲突激励(也称正确激励)。

84.如图3所示,双线程激励包括:线程1(线程标识为id0)和线程2(线程标识为id1);(w,5)表示线程1对目标寄存器执行写5操作,(r)表示线程2对目标寄存器执行读操作,为了使两个线程访问正确需要先执行线程1后执行线程0,但根据目标寄存器的竞争冒险机制,实际访问结果为先执行线程0后执行线程1(即写后读),导致线程2实际读到的值并不是目标寄存器中之前存储的6,且冲突列表中将“写后读”定义为冲突激励,根据访问结果中的执行顺序和执行状态与冲突列表进行比较,确定与“写后读”的冲突特征匹配,确定线程1和线程2为冲突激励,执行冲突激励会影响验证的收敛速度,因此在后续的验证过程中可以根据激励标识将冲突激励直接删除,不去执行。

85.需要说明的是,每个多线程激励生成后都设置有激励标识,用于区分不同激励,因此,可以通过在验证结果中携带激励标识向激励生成单元反馈冲突激励信息。

86.步骤409:将所述第二验证结果反馈到所述激励生成单元,使所述激励生成单元在生成新的多线程测试激励时过滤掉重复的冲突激励。

87.在一些实施例中,所述第二验证结果表征所述多线程激励为正确激励时,该方法还包括:将所述验证结果反馈到所述激励生成单元,使所述激励生成单元在生成新的多线程测试激励时过滤掉重复的正确激励。

88.由于再利用正确激励验证目标寄存器结果还是验证成功,因此,没有必要再利用正确激励去验证目标寄存器来浪费验证时间,可以将重复的正确激励删除,来进一步缩短验证周期。

89.采用上述技术方案,在验证多线程访问寄存器的过程中,通过将寄存器的验证结果反馈给激励生成单元,可以在后续激励的生成过程中过滤掉冲突激励,从而避免因使用冲突激励导致验证收敛速度降低的问题,缩短寄存器的验证周期,节约验证成本。

90.为了能更加体现本技术的目的,在本技术上述实施例的基础上,进行进一步的举例说明,如图5所示,该方法具体包括:

91.步骤501:开始;

92.实际应用中,应先进行验证环境的搭建和参数的初始化,具体的,根据验证原理图搭建验证环境,对验证环境进行测试并保证验证完全通过,完成环境的参数初始化。

93.步骤502:判断测试激励是否为空;如果否,执行步骤503或步骤507;如果是,执行步骤514;

94.实际应用中,可以根据功能覆盖率自动产生随机激励,如果测试激励不为空,判断测试激励访问的是独立寄存器还是共享寄存器,如果是独立寄存器,执行步骤503开始独立寄存器的验证,如果是共享寄存器,执行步骤507开始共享寄存器的验证;如果测试激励为

空,则验证结束。

95.步骤503:确定测试激励访问独立寄存器;

96.步骤504:寄存器模型读写验证,如果验证成功,返回步骤502;如果验证失败,执行步骤505;

97.步骤505:分析和修改;

98.步骤506:重新验证,如果验证成功,返回步骤502;如果验证失败,返回步骤505;

99.这里,步骤503至步骤506是对独立寄存器进行验证,由于独立寄存器是进行单线程访问,不存在访问冲突,因此只要读写验证成功即可。

100.图2这种验证平台既可以用于验证独立寄存也可以验证共享寄存器,对于独立寄存器只需要使用一个驱动器和一个监视器即可。

101.在利用图2这种验证平台验证独立寄存器时,图2可以简化为图6这种结构,图6为本技术实施例中验证平台的第二组成结构示意图,如图6所示,验证平台包括:测试用例、验证环境(env)和待测组件(dut)。

102.测试用例包括:覆盖监视器(coverage monitor)、寄存器模型(reg model)和序列(sequence),这里,sequence也称为激励产生单元。

103.验证环境包括:适配器0(adapter0)、序列发生器(sequencer)、驱动器d0,监视器m0、预测器(predictor)、适配器1(adapter1)和dut的参考模型(reference model)。

104.通过coverage monitor实时获取寄存器模型的三个值,并检查三个值是否相同,相同则验证成功,验证失败时分析并修改,重复此操作直到验证成功返回步骤502。

105.步骤507:确定测试激励访问共享寄存器;

106.步骤508:寄存器模型读写验证,如果验证成功,执行步骤511;如果验证失败,执行步骤509;

107.步骤509:分析和修改;

108.步骤510:重新验证,如果验证成功,执行步骤511;如果验证失败,返回步骤509;

109.步骤511:提取多线程访问结果;

110.步骤512:判断多线程冲突,如果是,执行步骤513;如果否,返回步骤502;

111.步骤513:删除冲突激励,继续执行步骤502;

112.这里,步骤507至步骤513是对共享寄存器进行验证,由于共享寄存器能够进行多线程访问,存在访问冲突的可能,因此除了进行读写验证之外,还需要验证是否冲突。

113.这里,访问共享寄存器的测试激励为复杂的多线程激励。利用图2这种验证平台验证共享寄存器时,先对寄存器的三个值进行验证,通过coverage monitor实时获取寄存器模型的三个值并验证,如果寄存器读写值不正确,分析并修改,重复此操作直到case pass。如果寄存器验证通过,coverage monitor对多线程访问共享寄存器访问结果进行提取,并判断访问结果是否发生冲突,如果没有发生冲突返回步骤502;否则,记录并删除冲突激励,再返回步骤502。

114.步骤514:结束。

115.采用上述技术方案,基于寄存器模型,对多线程访问寄存器的技术进行验证,可以自动产生多线程寄存器测试模型,对寄存器进行自动验证并反馈冲突激励信号到激励发生单元对冲突激励进行分析和约束,能够加快多线程访问寄存器技术的验证,节约成本,保证

数字电路设计产品的质量和提高数字电路设计产品的生产率。还可以对重复的正确激励进行分析和约束,来加快验证收敛速度。

116.本技术实施例中还提供了一种寄存器验证装置,如图7所示,该装置包括:

117.激励产生单元701,用于生成验证目标寄存器的测试激励;

118.验证单元702,用于检测到所述测试激励为多线程激励,基于所述多线程激励在所述目标寄存器的寄存器模型中设置第一寄存器信息,并且将所述多线程激励并行输入到所述目标寄存器,输出第二寄存器信息;

119.监视单元703,用于基于所述第一寄存器信息和所述第二寄存器信息对所述目标寄存器进行验证,得到验证结果;

120.所述监视单元703,还用于将所述验证结果反馈到所述激励生成单元;

121.所述激励生成单元701,还用于基于所述验证结果在生成新的多线程测试激励时过滤掉重复的冲突激励。

122.在一些实施例中,验证单元702,具体用于基于所述多线程激励中每个线程的线程标识,确定每个线程对应的驱动器;将每个线程分别送入到各自对应的驱动器中;控制多个驱动器将所述多线程激励同时驱动到所述目标寄存器的多个接口,以实现对所述目标寄存器的多线程访问;利用多个监视器分别监视所述多个接口,得到所述第二寄存器信息。

123.在一些实施例中,所述第二寄存器信息包括每个线程访问所述目标寄存器时的真实值、执行顺序和执行状态;其中,所述执行状态为读状态或写状态;

124.验证单元702,具体用于利用所述多个监视器分别监视所述多个接口,基于每个线程的执行顺序从所述多个接口分别获取每个线程访问所述目标寄存器时的真实值和执行状态;基于每个线程访问所述目标寄存器时的执行顺序,将每个线程的真实值和执行状态依次存入到目标队列中;从所述目标队列中获取所述第二寄存器信息。

125.在一些实施例中,监视单元703,具体用于基于所述第一寄存器信息和所述第二寄存器信息对所述目标寄存器进行读写验证,得到第一验证结果;所述第一验证结果表征所述目标寄存器的读写功能验证成功时,基于所述第二寄存器信息对所述多线程激励进行冲突验证,得到第二验证结果;将所述第二验证结果反馈到所述激励生成单元。

126.在一些实施例中,所述第一寄存器信息包括每个线程访问所述目标寄存器时的期望值和镜像值;所述第二寄存器信息包括每个线程访问所述目标寄存器时的真实值;

127.监视单元703,具体用于所述多线程激励中所有线程访问所述目标寄存器时的期望值、镜像值和真实值相同时,确定所述目标寄存器的读写功能验证成功;所述多线程激励中至少部分线程访问所述目标寄存器的期望值、镜像值和真实值不相同时,确定所述目标寄存器的读写功能验证失败。

128.在一些实施例中,所述第二寄存器信息还包括每个线程访问所述目标寄存器时的执行顺序和执行状态;其中,所述执行状态为读状态或写状态;

129.监视单元703,具体用于基于每个线程访问所述目标寄存器时的执行顺序和执行状态,判断所述多线程激励是否与预设的冲突特征匹配;若匹配,确定所述多线程激励为冲突激励;若不匹配,确定所述多线程激励为正确激励。

130.这里,监视单元可以是图2中的覆盖监视器。也就是说,本技术实施例覆盖监视器主要实现两个功能:第一,实时收集寄存器模型的value,m_mirrored和m_desired三个值,

来验证寄存器读写功能的正确性;第二,实时监视寄存器的访问状态(寄存器模型和寄存器一一对应),来判断多线程访问共享寄存器是否发生冲突,并反馈给测试激励产生单元。

131.在一些实施例中,所述冲突特征包括以下至少一种写后读、写后写、读后写。

132.在一些实施例中,监视单元703,还用于所述第二验证结果表征所述多线程激励为正确激励时,将所述第二验证结果反馈到所述激励生成单元,使所述激励生成单元在生成新的多线程测试激励时过滤掉重复的正确激励。

133.在一些实施例中,监视单元703,还用于所述第一验证结果表征所述目标寄存器的读写功能验证失败时,生成修改提示信息,以提示所述目标寄存器读写功能异常。

134.在一些实施例中,激励生成单元701,还用于基于预设的激励约束条件,控制激励生成单元生成验证目标寄存器的测试激励;其中,所述激励约束条件是根据所述目标寄存器的验证需求设定的。

135.在一些实施例中,所述目标寄存器是能够处理并行任务的共享寄存器。

136.基于上述寄存器验证装置中各单元的硬件实现,本技术实施例还提供了一种寄存器验证设备,如图8所示,该设备包括:处理器801和配置为存储能够在处理器上运行的计算机程序的存储器802;

137.其中,处理器801配置为运行计算机程序时,执行前述实施例中的方法步骤。

138.当然,实际应用时,如图8所示,该设备中的各个组件通过总线系统803耦合在一起。可理解,总线系统803用于实现这些组件之间的连接通信。总线系统803除包括数据总线之外,还包括电源总线、控制总线和状态信号总线。但是为了清楚说明起见,在图8中将各种总线都标为总线系统803。

139.在实际应用中,上述处理器可以为特定用途集成电路(asic,application specific integrated circuit)、数字信号处理装置(dspd,digital signal processing device)、可编程逻辑装置(pld,programmable logic device)、现场可编程门阵列(field-programmable gate array,fpga)、控制器、微控制器、微处理器中的至少一种。可以理解地,对于不同的设备,用于实现上述处理器功能的电子器件还可以为其它,本技术实施例不作具体限定。

140.上述存储器可以是易失性存储器(volatile memory),例如随机存取存储器(ram,random-access memory);或者非易失性存储器(non-volatile memory),例如只读存储器(rom,read-only memory),快闪存储器(flash memory),硬盘(hdd,hard disk drive)或固态硬盘(ssd,solid-state drive);或者上述种类的存储器的组合,并向处理器提供指令和数据。

141.在示例性实施例中,本技术实施例还提供了一种计算机可读存储介质,例如包括计算机程序的存储器,计算机程序可由寄存器验证设备的处理器执行,以完成前述方法的步骤。

142.本技术实施例所记载的技术方案之间,在不冲突的情况下,可以任意组合。

143.在本技术所提供的几个实施例中,应该理解到,所揭露的方法、装置和设备,可以通过其它的方式实现。以上所描述的实施例仅仅是示意性的,例如,单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,如:多个单元或组件可以结合,或可以集成到另一个系统,或一些特征可以忽略,或不执行。另外,所显示或讨论的各组成部分

相互之间的耦合、或直接耦合、或通信连接可以是通过一些接口,设备或单元的间接耦合或通信连接,可以是电性的、机械的或其它形式的。

144.上述作为分离部件说明的单元可以是、或也可以不是物理上分开的,作为单元显示的部件可以是、或也可以不是物理单元,即可以位于一个地方,也可以分布到多个网络单元上;可以根据实际的需要选择其中的部分或全部单元来实现本实施例方案的目的。

145.另外,在本技术各实施例中的各功能单元可以全部集成在一个处理单元中,也可以是各单元分别单独作为一个单元,也可以两个或两个以上单元集成在一个单元中;上述集成的单元既可以采用硬件的形式实现,也可以采用硬件加软件功能单元的形式实现。

146.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1