具有总线仲裁器的主从通信系统及通信方法与流程

[0001]

本发明涉及fpga应用领域,尤其涉及一种具有总线仲裁器的主从通信系统以及一种通信方法。

背景技术:

[0002]

总线是计算机系统各种功能部件之间传送信息的公共通信干线,它是处理器、内存、输入输出设备传递信息的公用通道,主机的各个部件通过总线相连接,外部设备通过相应的接口电路再与总线相连接。

[0003]

在mcu(micro-controller unit,微控制器)领域,通常将mcu内核的外部设备分为主设备和从设备,主设备可以向从设备发送读指令和写指令。主设备和从设备可以均大于一个。多个主设备和多个从设备通过总线仲裁器连接到总线系统,其中,利用总线仲裁器可以分段mcu的内存地址空间,并将每段地址分配给各个从设备,通过区分地址分段分配给各个从设备的地址空间,来区分通过总线系统访问的各个从设备。

[0004]

现有总线仲裁器设计中,为从设备设置的内存地址空间一旦设计好就固定了下来,在实际应用过程中容易出现以下几种问题:一是从设备所需的地址空间大于总线仲裁器分配的地址空间,需重构mcu存储空间的地址映射;二是从设备所需的地址空间小于总线仲裁器分配的地址空间,造成mcu存储空间地址浪费;三是由于每个从设备分配的地址空间固定,会制约从设备的数量扩展,降低了mcu存储空间的地址利用率。

技术实现要素:

[0005]

为了解决上述问题,本发明提供了一种具有总线仲裁器的主从通信系统。另外还提供了一种通信方法。

[0006]

一方面,本发明提供一种具有总线仲裁器的主从通信系统,所述主从通信系统用于实现主设备和从设备之间的通信,所述主设备和所述从设备的数量均在两个以上,所述总线仲裁器包括基于fpga(field programmable gate array,现场可编程门阵列)实现的动态地址分配模块,所述动态地址分配模块用于分配所述从设备映射于系统内存中的起始地址和空间大小,其中,所述起始地址和空间大小动态可调,所述总线仲裁器利用所述动态地址分配模块获得各个所述从设备映射于系统内存中的起始地址和空间大小,并对两个以上的所述主设备向同一所述从设备发出的连接请求进行仲裁。

[0007]

可选的,所述从设备的数量大于或等于所述主设备的数量。

[0008]

可选的,所述动态地址分配模块配置有多个从设备起始地址寄存器和多个从设备地址空间寄存器,每个所述从设备起始地址寄存器配置为寄存一个所述从设备对应的起始内存地址,每个所述从设备地址空间寄存器配置为寄存一个所述从设备对应的内存地址空间。

[0009]

可选的,对应于每个所述主设备,所述动态地址分配模块配置有与所述主设备相关的从设备起始地址寄存器和从设备地址空间寄存器,且各个所述主设备对应的所述从设

备起始地址寄存器和从设备地址空间寄存器的数量动态可调。

[0010]

可选的,所述总线仲裁器还包括基于所述fpga实现的以下模块:

[0011]

主设备解析模块,与所述主设备一一对应设置,所述主设备解析模块配置为解析并锁存来自对应的所述主设备的信号,还配置为向对应的所述主设备反馈来自所述从设备的响应信号;

[0012]

从设备地址解析模块,与所述主设备一一对应设置,配置为从所述动态地址分配模块获得与对应的所述主设备相关的所述从设备的内存地址信息,还配置为调用所述主设备解析模块锁存的来自对应的所述主设备的信号,在多个从设备输出模块中选择要通信的一个,以建立通信通道;以及,

[0013]

从设备输出模块,与所述从设备一一对应设置,所述从设备输出模块配置为向对应的从设备输出来自所述主设备的信号,并读取对应的从设备反馈的响应信号。

[0014]

可选的,所述总线仲裁器还包括基于所述fpga实现的主设备竞争模块,所述主设备竞争模块与所述从设备输出模块一一对应地设置于所述从设备地址解析模块与所述从设备输出模块之间,每个所述主设备竞争模块与各个所述从设备地址解析模块均连接;其中,当两个以上的从设备地址解析模块均选择了同一个所述从设备进行通信时,与所述从设备对应的所述主设备竞争模块根据优先级规则来对所述从设备地址解析模块进行排序,并按照优先级顺序依次使各个所述从设备地址解析模块与所述从设备通信。

[0015]

可选的,所述主设备解析模块解析并锁存的来自对应的所述主设备的信号包括写数据信号、读数据信号、地址信号、读写控制信号和使能信号。

[0016]

可选的,所述主从通信系统为基于fpga和mcu内核配置的片上系统,所述mcu内核通过私有总线与所述动态地址分配模块交互,并利用所述mcu内核的可执行程序控制所述动态地址分配模块对所述从设备映射于系统内存中的起始地址和空间大小进行动态调节。

[0017]

可选的,所述片上系统具有主设备总线和从设备总线,所述主设备通过相应的总设备总线与所述总线仲裁器连接,所述从设备通过相应的从设备总线与所述总线仲裁器连接。

[0018]

一方面,本发明提供一种通信方法,采用了上述主从通信系统,所述通信方法包括以下步骤:

[0019]

对来自所述主设备的信号进行解析,判断所述主设备是否发出针对所述从设备的连接请求,若是,则向下执行,若否,则返回进行下一次判断;

[0020]

向所述总线仲裁器发送来自所述主设备的信号,所述总线仲裁器判断要通信的从设备,并利用所述动态地址分配模块分配的所述从设备的内存地址分配信息,选择要通信的从设备并形成相应的通信通道;以及,

[0021]

所述总线仲裁器从来自所述主设备的信号中获得读写控制信号,判断所述主设备对所述从设备执行的是读操作还是写操作,若是读操作,通过所述通信通道将所述从设备的数据信号发送给所述主设备,若是写操作,通过所述通信通道将所述主设备的数据信号发送给所述从设备。

[0022]

本发明提供的具有总线仲裁器的主从通信系统,其中所述总线仲裁器包括基于fpga实现的动态地址分配模块,所述动态地址分配模块用于配置从设备映射于系统内存中的起始地址和空间大小,基于fpga可编程的特点,所述起始地址和空间大小动态可调。可以

有效解决从设备所需的地址空间与原分配的地址空间不匹配的问题,提高了系统内存空间的地址利用率,同时利用总线仲裁器对两个以上的所述主设备向同一所述从设备发出的连接请求进行仲裁,从设备的数量可以灵活扩展,有利于提高系统的整体性能。

[0023]

本发明提供的通信方法,采用了上述具有总线仲裁器的主从通信系统,所述通信方法中,从设备的内存地址信息可以进行动态调整,并且可以实现主设备和从设备之间的通信,具有广泛的应用前景。

附图说明

[0024]

图1是本发明一实施例的主从通信系统的信号连接示意图。

[0025]

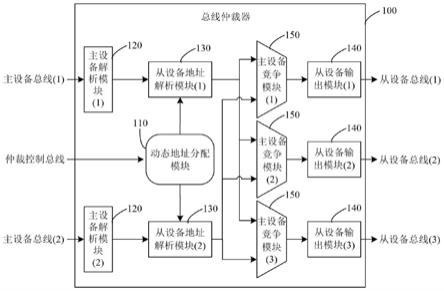

图2是本发明一实施例的主从通信系统中总线仲裁器的架构示意图。

[0026]

图3是本发明一实施例的总线仲裁器中动态地址分配模块的架构示意图。

[0027]

图4是本发明一实施例的通信方法的流程示意图。

[0028]

附图标记说明:

[0029]

100-总线仲裁器;110-动态地址分配模块;120-主设备解析模块;130-从设备地址模块;140-从设备输出模块;150-主设备竞争模块。

具体实施方式

[0030]

以下结合附图和具体实施例对本发明的具有总线仲裁器的主从通信系统及通信方法作进一步详细说明。根据下面的说明,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

[0031]

在mcu设计中,各功能部件之间常通过总线仲裁器连接到总线系统,并利用总线仲裁器确定的地址分段分配各个从设备在mcu内核中的地址以及空间大小,从而在对任意一个从设备执行操作时,可以利用从设备的地址分段信息来区分总线系统访问的各个从设备。但是,如背景技术所述的,现有技术常容易发生从设备实际所需的地址空间与总线仲裁器分配的地址空间不匹配的问题,降低了mcu存储空间的地址利用率,而且,在每个从设备分配的地址空间被固定的情况下,从设备的数量扩展会受到制约。

[0032]

fpga(field programmable gate array,现场可编程门阵列)具有强大的可定制性(能够通过编程来支持非标准接口)以及可扩展性(fpga的硬件可编程、易修改、方便升级),本发明基于fpga的优势,提出了一种具有总线仲裁器的主从通信系统以及采用该主从通信系统的通信方法,可以有效避免或改进现有技术中存在的诸如从设备所需的地址空间与总线仲裁器分配的地址空间不匹配、存储空间的地址利用率低而造成浪费、从设备的数量可扩展性差的问题。

[0033]

基于mcu和fpga的优点,可以利用fpga的资源将mcu、存储器、外部设备等连接起来,从而构成一个可充分满足用户设计中的灵活性需求的片上系统(soc:system-on-a-chip),是近年来的一个研究热点。以下实施例中,主要以基于mcu和fpga的片上系统对本发明的主从通信系统进行说明。但需要说明的是,本发明的主从通信系统并不限于基于mcu和fpga的片上系统,本发明的主从通信系统也可以覆盖利用了fpga构建的其它片上系统或者非片上系统。一实施例中,所述主从通信系统也可以是一控制装置或者数据传输装置。

[0034]

本发明实施例的主从通信系统用于实现主设备和从设备之间的通信,所述主设备和所述从设备的数量均在两个以上,所述主设备和从设备的数量可以相同或不同,所述从设备的设置较为灵活,从设备的数量可以大于或等于主设备的数量。以下通过主从通信系统连接两个主设备和三个从设备的情形为例,对本发明实施例的主从通信系统进行说明。

[0035]

图1是本发明一实施例的主从通信系统的信号连接示意图。参见图1,本发明一实施例的主从通信系统用于实现主设备和从设备之间的通信,所述主设备例如有两个(主设备(1)和主设备(2)),从设备例如有三个(从设备(1)、从设备(2)和从设备(3))。所述主从通信系统包括mcu内核和fpga,所述主从通信系统利用fpga的资源配置有总线仲裁器,所述mcu内核和总线仲裁器之间以总线方式连接。其中,利用总线仲裁器可以分段mcu内核的内存地址空间,并将每段地址分配给各个从设备。所述总线仲裁器包括基于fpga实现的动态地址分配模块,所述动态地址分配模块用于分配各个从设备映射于系统内存(此处可看作mcu内存)中的起始地址和空间大小,所述动态地址分配模块可以由mcu内核控制,例如通过mcu内核的软件,动态调整各个从设备映射于系统内存中的起始地址和空间大小。

[0036]

图2是本发明一实施例的主从通信系统中总线仲裁器的架构示意图。参见图2,所述主从通信系统具有总线仲裁器100,并且,所述总线仲裁器100包括基于fpga的可编程资源实现的动态地址分配模块110,所述动态地址分配模块110用于配置主从通信系统连接的各个从设备映射于系统内存中的地址和空间大小,其中,所述从设备映射于系统内存中的地址和空间大小动态可调,所述总线仲裁器100利用所述动态地址分配模块110获得各个从设备映射于系统内存中的起始地址和空间大小,并对两个以上的主设备向同一所述从设备发出的连接请求进行仲裁。

[0037]

本发明实施例的主从通信系统利用所述总线仲裁器100来对各个从设备的内存地址进行分配,并且,由于所述总线仲裁器100利用fpga的可编程资源来实现动态地址分配模块110,以对各个从设备映射于系统内存中的地址和空间大小进行配置。从而,可以根据主设备和从设备的实际情况对动态地址分配模块110的编程内容进行调整,即可以实现对从设备映射于系统内存中的地址和空间大小的动态可调。

[0038]

上述设置有助于提高本发明实施例的主从通信系统的功能,举例说明如下。一实施例中,对于所述总线仲裁器连接的任意一个从设备,若其所需的地址空间大于总线仲裁器100原始分配的地址空间时,此时可以通过对所述动态地址分配模块110进行控制调整,例如,可以由mcu内核执行软件程序来控制所述动态地址分配模块110,使所述动态地址分配模块110对应的fpga的逻辑资源描述发生变化,从而所反映的各个从设备映射于系统内存中的地址和空间大小发生变化,使所述动态地址分配模块110经过调整后,其内部为该从设备分配的地址空间与相应从设备的需求匹配。一实施例中,一个从设备所需的地址空间若小于甚至远小于总线仲裁器原始分配的地址空间,如果直接使用,会造成系统内存地址空间的很大浪费,此时,应用上述总线仲裁器100,可以通过对所述动态地址分配模块110进行控制调整(调整方式可参照上一实施例),使得调整后,为该从设备分配的地址空间与其需求匹配,这样可以节省出系统内存的地址空间,提高内存空间的地址利用率。一实施例中,若需要扩展从设备的数量而现有内存地址空间的分配方式不能满足时,也可以应用上述总线仲裁器100,并在使用中,按照从设备的扩展要求对动态地址分配模块110进行调整(调整方式可参见上面的实施例),使其在调整之后,为扩展后的各个从设备分配的地址空

间与它们的需求匹配,这样可以提高系统的可扩展性以及设计灵活性。

[0039]

参见图2,所述主从通信系统配置的主设备和从设备的数量均在两个以上。所述主从通信系统可以为基于fpga和mcu内核(未示出)配置的片上系统(soc),各个主设备和从设备可以是mcu内核的片内外部设备或片外外部设备。所述片上系统具有主设备总线(如图2中的主设备总线(1)和主设备总线(2))和从设备总线(如图2中的从设备总线(1)、从设备总线(2)和从设备总线(3)),并且,各个所述主设备通过相应的主设备总线与所述总线仲裁器100连接,各个所述从设备通过相应的从设备总线与所述总线仲裁器100连接。此外,所述主从通信系统还可以具有仲裁控制总线,mcu内核可以通过所述仲裁控制总线控制总线仲裁器100中的上述动态地址分配模块110。具体的,所述仲裁控制总线可以配置为mcu内核的私有总线,也即所述mcu内核与所述动态地址分配模块100的交互是通过私有总线执行的。一实施例中,所述mcu内核可以通过执行相应的可执行程序来控制所述动态地址分配模块110,使所述动态地址分配模块110对应的fpga的逻辑资源发生变化,从而所反映的各个从设备映射于系统内存中的地址和空间大小发生变化,所述可执行程序可根据从设备的配置需要进行编程修改。所述可执行程序可以通过c语言编写并存储于所述主从通信系统的存储模块中。所述存储模块可以为片外的存储器,也可以在片内设置。进一步的,所述存储模块也可以通过fpga的资源来实现。

[0040]

图3是本发明一实施例的总线仲裁器中动态地址分配模块的架构示意图。参见图3,上述动态地址分配模块110可配置有多个从设备起始地址寄存器(如图3中的从设备(1)起始地址寄存器、从设备(2)起始地址寄存器以及从设备(3)起始地址寄存器,图中数量仅为示例)和多个从设备地址空间寄存器(如图3中的从设备(1)地址空间寄存器、从设备(2)地址空间寄存器以及从设备(3)地址空间寄存器,图中数量仅为示例),每个所述从设备起始地址寄存器配置为存放一个与所述总线仲裁器100连接的从设备对应的起始内存地址,每个所述从设备地址空间寄存器配置为存放一个与所述总线仲裁器100连接的从设备对应的内存地址空间。另外,对应于与所述总线仲裁器100连接的每个主设备,所述动态地址分配模块100可以对应配置有与该主设备有关的(此处指存在主从设备交互关系)的从设备起始地址寄存器和从设备地址空间寄存器,以供与各个主设备一一对应的从设备地址解析模块130调用,如图3中的两个从设备地址解析模块130(从设备地址解析模块(1)和从设备地址解析模块(2))分别从各自对应的寄存器组调用各个从设备的起始地址和地址空间。图3中从设备地址解析模块130的数量仅为示例。一实施例中,各个主设备对应的(也即由各个从设备地址解析模块130调用的)从设备起始地址寄存器和从设备地址空间寄存器的数量在所述mcu内核的控制下能够动态调节,从而可以提高设计的灵活性,提升系统内存空间(如mcu内核内的内存空间)的地址利用率,提高主从通信系统的整体性能。

[0041]

参见图2和图3,一实施例中,上述总线仲裁器100还包括利用所述fpga的资源实现的主设备解析模块120、从设备地址解析模块130以及从设备输出模块140。总线仲裁器100中的各个模块可以通过fpga的连接线资源形成连接。

[0042]

所述主设备解析模块120与所述总线仲裁器100连接的主设备一一对应设置。图2中,所述总线仲裁器示例性地包括两个主设备解析模块120(分别为图2中的主设备解析模块(1)和主设备解析模块(2))。所述主设备解析模块120可以配置为解析并锁存来自对应的所述主设备的信号,还配置为向对应的所述主设备反馈来自所述从设备的有效的响应信号

(ack)。所述主设备解析模块120可以通过主设备总线连接对应的所述主设备。

[0043]

所述从设备地址解析模块130与所述主设备一一对应设置(即与主设备解析模块120一一对应设置,图2中的从设备地址解析模块130为从设备地址解析模块(1)和从设备地址解析模块(2)。所述从设备地址解析模块130连接对应的主设备解析模块120。一实施例中,所述从设备地址解析模块130配置为从上述动态地址分配模块110获得与对应的所述主设备有关的所述从设备的内存地址信息,还配置为调用所述主设备解析模块120锁存的来自对应的所述主设备的信号(包括连接请求信号),在所连接的多个从设备输出模块中选择要通信的一个,以建立通信通道。在此,所述从设备地址解析模块130对应的主设备指的是所述从设备地址解析模块130通过主设备解析模块120所连接的主设备。与主设备有关的从设备指的是与所述主设备具有通信关系的从设备。

[0044]

所述从设备输出模块140(如图2中示例性的从设备输出模块(1)、从设备输出模块(2)以及从设备输出模块(3))与总线仲裁器100所连接的从设备一一对应设置。所述从设备输出模块140可以配置为向对应的从设备输出来自所述主设备的信号(包括连接请求信号),并读取对应的从设备的响应信号(ack)。

[0045]

在通信过程中,当两个以上的从设备地址解析模块130均选择了同一个从设备进行通信时,即所述总线仲裁器100在判断两个以上的所述主设备均向同一所述从设备发出连接请求时,需要进行仲裁,因此,一实施例中,上述总线仲裁器100还可以包括基于所述fpga实现的主设备竞争模块150(如图2中的主设备竞争模块(1)、主设备竞争模块(2)以及主设备竞争模块(3)),各个主设备竞争模块150与各个上述从设备输出模块140一一对应地设置于从设备地址解析模块130与从设备输出模块140之间,每个所述主设备竞争模块150与各个所述从设备地址解析模块130均连接。所述主设备竞争模块150可以配置为:当两个以上的从设备地址解析模块130均选择了同一个从设备(主设备竞争模块150对应的从设备)进行通信时,与所述从设备对应的所述主设备竞争模块150根据优先级规则来对所述从设备地址解析模块130进行排序,并按照优先级顺序依次使各个所述从设备地址解析模块130与所述从设备通信。所述优先级规则中,可以设置较主设备竞争模块150位置更近(或更远)的从设备地址解析模块130优先级更高,相应的,设置较主设备竞争模块150位置较远(或较近)的从设备地址解析模块130优先级较低。主设备竞争模块150采用的优先级规则也可以根据公开方式设定。所述优先级顺序可以是优先级从高到低的顺序,也可以是优先级从低到高的顺序,例如按照优先级从高到低的顺序进行时,优先级最高的从设备地址解析模块130最先与所述从设备进行通信。

[0046]

本发明实施例涉及的主从通信系统传输的信号可包括写数据信号(wdata)、读数据信号(rdata)、地址信号(addr)、使能信号(enable)、读写控制信号(ctrl)和响应信号(ack)等。所述总线仲裁器100可以基于寄存器操作来实现主设备和从设备之间的信号传输。以下以基于mcu和fpga的片上系统为例,对总线仲裁器100的上述各个模块在通信过程中的作用作进一步说明。

[0047]

在mcu内核获得主设备的操作信号后,将所述操作信号通过主设备总线发送至上述主设备解析模块120。主设备解析模块120可以实现数据在主设备总线和内部寄存器的映射,从而解析并锁存来自对应的所述主设备的信号,此处主设备解析模块120锁存的信号包括mcu内核通过主设备总线发送写数据信号(wdata)、读数据信号(rdata)、地址信号

(addr)、读写控制信号(ctrl)、使能信号(enable)。这些信号可以供与主设备解析模块120连接的从设备地址解析模块130调用。在通信时,所述主设备解析模块120在接收到来自对应的所述主设备的信号后,可以先通过主设备总线向对应的主设备反馈一个电平(例如为低电平),代表初始的响应信号(ack),然后,所述主设备解析模块120监控内部的从设备地址解析模块130反馈的响应信号(ack),当从设备地址解析模块130反馈的响应信号(ack)与初始的电平相反(例如为高电平),则再给片外的主设备反馈该相反电平,相当于反馈了一个有效的响应信号(ack)。

[0048]

所述从设备地址解析模块130可以通过解析读取对应的主设备解析模块120中的addr寄存器(即地址寄存器),并选择需要控制的从设备所对应的主设备竞争模块150,目的是使要通信的主设备和从设备之间形成通信通道。从设备地址解析模块130可以先读取动态地址分配模块110的从设备起始地址寄存器和从设备地址空间寄存器(图3),产生地址查找表;然后根据地址查找表,从主设备解析模块120调用写数据信号(wdata)、读数据信号(rdata)、地址信号(addr)、使能信号(enable)、读写控制信号(ctrl)发送给相应的主设备竞争模块150,同时读取从相应的主设备竞争模块150反馈的响应信号(ack)并发送给主设备解析模块120,主设备解析模块120再将响应信号(ack)反馈给对应的主设备。

[0049]

其中,当两个以上的从设备地址解析模块130均选择了同一个从设备进行通信时(即两个以上的所述主设备均向同一所述从设备发出连接请求时),与该从设备对应的主设备竞争模块150首先锁存各个从设备地址解析模块130(如图2中从设备地址解析模块(1)和从设备地址解析模块(2)两个通道)发送的写数据信号(wdata)、读数据信号radta、地址信号(addr)、读写控制信号(ctrl)、使能信号(enable),具体可以存储于相应的寄存器中。主设备竞争模块150另外监控对应的从设备输出模块140的响应信号(ack),如果该信号为高电平则反馈高电平给优先级最高的从设备地址解析模块130通信通道,然后将该高优先级通信通道的写数据信号(wdata)、读数据信号radta、地址信号(addr)、读写控制信号(ctrl)、使能信号(enable)对应的寄存器的信号给到对应的从设备输出模块140,完成通信;然后继续监控对应的从设备输出模块140的响应信号(ack),如果为高电平则反馈高电平给较低优先级的从设备地址解析模块130的通信通道,并将低优先级通信通道的写数据信号(wdata)、读数据信号radta、地址信号(addr)、读写控制信号(ctrl)、使能信号(enable)给到对应的从设备输出模块140,完成通信;依照类似的顺序,完成该同一个从设备与各个从设备地址解析模块130在对应通信通道的通信。

[0050]

对于上述从设备输出模块140,在获得主设备竞争模块150(即上一级模块)中发送的写数据信号(wdata)、读数据信号(rdata)、地址信号(addr)、使能信号(enable)、读写控制信号(ctrl)(例如可以通过调用主设备竞争模块150的寄存器来实现),输出相应的信号到所连接的从设备,同时读取所连接的从设备反馈的响应信号(ack),反馈给与其连接的主设备竞争模块150。

[0051]

本发明实施例另外涉及一种通信方法,采用了上述主从通信系统。所述通信方法包括以下步骤:

[0052]

对来自所述主设备的信号进行解析,判断所述主设备是否发出针对所述从设备的连接请求,若是,则向下执行,若否,则返回进行下一次判断;

[0053]

向所述总线仲裁器发送来自所述主设备的信号,所述总线仲裁器判断要通信的从

设备,并利用所述动态地址分配模块分配的所述从设备的内存地址分配信息,选择要通信的从设备并形成相应的通信通道;以及,

[0054]

所述总线仲裁器从来自所述主设备的信号中获得读写控制信号,判断所述主设备对所述从设备执行的是读操作还是写操作,若是读操作,通过所述通信通道将所述从设备的数据信号发送给所述主设备,若是写操作,通过所述通信通道将所述主设备的数据信号发送给所述从设备。

[0055]

图4是本发明一实施例的通信方法的流程示意图。结合图2至图4,以下以如图2所示的两个主设备(与图中两个主设备总线连接)和三个从设备(与图中三个从设备总线连接)为例,对上述通信方法进行说明。

[0056]

所述通信方法可包括如下过程:

[0057]

s1:mcu内核对各个主设备的信号进行扫描,若某个主设备发出连接请求的操作信号,则mcu内核通过对应的主设备总线向总线仲裁器100发送信号,此时使能信号例如为高电平(enable=1);

[0058]

s2:总线仲裁器100根据地址信号判断通过哪一个从设备地址解析模块130进行地址解析和建立通信通道,并由对应的主设备解析模块120锁存来自主设备的信号,本实施例中,两个从设备地址解析模块130(如图2中的从设备地址解析模块(1)和从设备地址解析模块(2))分别与两个主设备交互,并且均与三个从设备交互,因而,在选择这两个从设备地址解析模块130中的一个(如图2中的从设备地址解析模块(1)和从设备地址解析模块(2))之后,该从设备地址解析模块130可以从动态地址分配模块110获得要连接的从设备(如图4中的从设备(1)、从设备(2)和从设备(3)),从设备地址解析模块130根据地址信号判断要通信的从设备对应的内存地址信息(包括起始地址和地址空间大小),以便于与要通信的从设备建立通信通路以进行信号传输,具体可以将从动态地址分配模块110中获得的从设备对应的内存地址信息发送给相应的主设备竞争模块150,并由主设备竞争模块150根据优先级规则在所述从设备地址解析模块130与要通信的从设备之间建立连接;

[0059]

s3:在通信通路建立之后,通过寄存器操作进行信号传输,首先总线仲裁器100的主设备解析模块120根据读写控制信号判断要进行的是读操作还是写操作,根据判断结果,从设备地址解析模块130调用其连接的主设备解析模块120中的读寄存器或者写寄存器,将信号发送到与选定的从设备连接的主设备竞争模块150,主设备竞争模块150根据优先级规则,将来自从设备地址解析模块130的信号给到对应的从设备输出模块140,从设备输出模块140再将信号发送给与其连接的从设备,另外从设备输出模块140在读取到所述从设备反馈的响应信号后,反馈给主设备竞争模块150,所述响应信号进一步通过从设备地址解析模块130、主设备解析模块120反馈给mcu内核以及主设备,从而本次通信结束。

[0060]

上述通信方法中,对来自所述主设备的信号进行解析的操作、向所述总线仲裁器发送来自所述主设备的信号的操作以及对所述总线仲裁器的控制操作可以由mcu内核执行。所述通信方法可以以计算机程序形式存储于一存储器中,当所述计算机程序被所述主从通信系统的处理器执行时,可以执行上述通信方法。

[0061]

本发明实施例描述的具有总线仲裁器100的主从通信系统,可以有效解决从设备所需的地址空间与总线仲裁器分配的地址空间不匹配的问题,提高了系统内存空间的地址利用率,同时利用总线仲裁器对两个以上的所述主设备向同一所述从设备发出的连接请求

进行仲裁,从设备的数量不会受固化地址制约,可以灵活扩展,有利于提高系统的整体性能。本发明实施例描述的通信方法,采用了上述具有总线仲裁器100的主从通信系统,所述通信方法中,从设备的内存地址信息可以根据从设备的实际配置而动态调整,并且可以实现主设备和从设备之间的通信,具有广泛的应用前景。

[0062]

上述描述仅是对本发明较佳实施例的描述,并非对本发明权利范围的任何限定,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1